# UNIVERSIDADE FEDERAL DA BAHIA ESCOLA POLITÉCNICA DEPARTAMENTO DE ENGENHARIA ELÉTRICA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

## TESE DE DOUTORADO

# ARQUITETURAS DE MULTIPLICADOR ANALÓGICO EM TECNOLOGIA CMOS PARA APLICAÇÃO COMO SINAPSE DE CNN

Antônio José Sobrinho de Sousa

Orientadora: Prof<sup>a</sup> Dr<sup>a</sup> Ana Isabela Araújo Cunha

**Salvador – Bahia – Brasil, 2020**©Antônio José Sobrinho de Sousa, Abril de 2020.

## Antônio José Sobrinho de Sousa

## Arquiteturas de Multiplicador Analógico em Tecnologia CMOS para Aplicação como Sinapse de CNN

Tese apresentada à Coordenação do Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal da Bahia, em cumprimento às exigências para obtenção do Grau de Doutor em Engenharia Elétrica.

Ana Isabela Araújo Cunha Orientadora

> Salvador – Bahia Abril de 2020

#### S725 Sousa, Antônio José Sobrinho de

Arquiteturas de Multiplicador Analógico em Tecnologia CMOS para Aplicação como Sinapse de CNN / Antônio José Sobrinho de Sousa. - Salvador, 2020.

126 f.: il.color.

Orientadora: Profa. Dra. Ana Isabela Araújo Cunha Tese (doutorado) - Universidade Federal da Bahia. Escola Politécnica, 2020.

1. Visão artificial. 2. Circuitos elétricos. 3. Transmissão sináptica. 4. Redes neurais (Computação). I. Cunha, Ana Isabela Araújo. II. Universidade Federal da Bahia. III. Título.

CDD: 006.32

#### Antonio José Sobrinho de Sousa

"Arquiteturas de Multiplicador Analógico em Tecnologia CMOS para Aplicação como Sinapse de CNN"

Tese apresentada à Universidade Federal da Bahia, como parte das exigências do Programa de Pós-Graduação em Engenharia Elétrica, para a obtenção do título de Doutor.

APROVADA em: 24 de abril de 2020.

#### **BANCA EXAMINADORA**

Orientadora/UFBA

Professor Dr. Edson Pinto Santana **UFBA**

Maricon O. Perrira Professor Dr. Maicon Deivid Pereira

Joquin Juinier hiblio de Dima Professor Dr. Joaquim Júnior Isídio de Lima **UNIVASF**

Professor Dr. Rieymison do Nascimento Souza

**UFOB**

## **DEDICATÓRIA**

À Noélia e Firmino (In Memoriam), a minha amada esposa Isa e aos meus quatro amados filhos, e a todos os meus familiares e amigos por minha ausência e dispersão.

## **AGRADECIMENTOS**

Nesta jornada longa e árdua, porém profícua, deparei-me com todo tipo de problemas e dificuldades, desde os inerentes às minhas próprias limitações, as do labor do doutoramento até as profissionais para minha liberação e conclusão de tão importante patamar na vida acadêmica. Mas apesar de todos os percalços não caminhei só, pois Deus nunca nos deixa caminhar, sem ao menos, nos observar. Então envia-nos seus anjos em forma de pessoas que nos auxiliam. Neste sentido externo meus mais sinceros agradecimentos a todos que direta ou indiretamente auxiliaram no desenvolvimento deste trabalho: aos colegas: Ademir Costa, Alípio Silva, Cléber Almeida, Eliyas Mehdipour, Fabian Souza, Fernando Cardoso, Gabriele Gonçalves, Hildelói Santos, Kelvin Kefren, Lucas D'Eça, Matheus Artur, Rodrigo Barros, Rafael Medeiros e Milton Leslie que de forma irrestrita sempre me auxiliaram. Aos professores do Laboratório de Concepção de Circuitos Integrados (LCCI-UFBA) Profo Dr. Edson Pinto Santana e Profo Dr. Maicon Deivid Pereira, ao Programa de Pós-Graduação em Engenharia Elétrica (PPGEE-UFBA) e à CAPES pela cessão da bolsa no inicio do curso, à Universidade Federal do Oeste da Bahia (UFOB) pela liberação parcial e integral, ao Departamento de Engenharia Elétrica (DEE-UFBA), e aos meus colegas da UFOB, em destaque ao Profo Dr. Kleymilson do Nascimento Souza, a Profa Andressa Pereira, Profo Ademário José de Carvalho Neto, Profo Manoel Messias Silva Júnior e Prof<sup>a</sup> Stefânia de Oliveira Silva.

Em especial, desejo expressar a minha mais profunda gratidão à Professora Doutora Ana Isabela Araújo Cunha, visto que palavras de agradecimento seriam ínfimas para um ser que acredito etéreo.

SOUSA, Antônio J. Sobrinho de. **Arquiteturas de Multiplicador Analógico em Tecnologia CMOS para Aplicação como Sinapse de CNN**. 126 f. 2020. Tese (Doutorado em Engenharia Elétrica) – Escola Politécnica, Universidade Federal da Bahia, Salvador, Bahia, Brasil, 2020.

## **RESUMO**

Este trabalho apresenta novas arquiteturas de multiplicadores analógicos em tecnologia CMOS (Complementary Metal-Oxide-Semiconductor)<sup>1</sup> para aplicação como elemento de sinapse em redes neuronais celulares analógicas (CNN: cellular neural networks). Os circuitos propostos apresentam as duas entradas em modo tensão e a saída em modo corrente e seguem o princípio segundo o qual o MOSFET em inversão forte e saturação atua como um quadrador da tensão porta-fonte. Embora este princípio seja utilizado por um grande número de multiplicadores com entradas em modo tensão, a inovação das propostas aqui descritas reside nos métodos de aplicação dos sinais, um dos quais dispensa geradores de referência de tensão. A análise de desempenho em variados aspectos foi realizada por meio de simulações considerando implementação em uma tecnologia CMOS de 130 nm, com tensão de alimentação simétrica de ±0,6 V. Em todos os projetos priorizou-se uma diminuição significativa da área ativa, em relação a trabalhos anteriores do mesmo grupo de pesquisa, sem prejuízos importantes de outras características de desempenho para aplicação como elemento de sinapse em CNN, como baixo consumo de energia e baixos níveis de distorção.

*Palavras-Chaves*: Sinapse eletrônica, CNN, multiplicador analógico CMOS, multiplicador de quatro quadrantes, redes neuronais, processamento de sinais analógicos.

-

<sup>&</sup>lt;sup>1</sup> Tecnologia de fabricação de circuitos integrados baseada em transistores de efeito de campo MOS (metal-óxido-semicondutor) complementares (canal N e canal P).

SOUSA, Antônio J. Sobrinho de. **Arquiteturas de Multiplicador Analógico em Tecnologia CMOS para Aplicação como Sinapse de CNN**. 126 f. 2020. Tese (Doutorado em Engenharia Elétrica) — Escola Politécnica, Universidade Federal da Bahia, Salvador, Bahia, Brasil, 2020.

## **ABSTRACT**

This work presents new architectures of analog multipliers in CMOS technology, for the application as synaptic elements in cellular neural networks (CNN). The proposed circuits adopt two voltage-mode inputs and current-mode output, and are based on the principle according to which the MOSFET acts as a gate-source voltage squarer in strong inversion and saturation. Although such principle is employed by numerous CMOS multipliers with voltage-mode inputs, the here described circuits are innovative concerning the signal application methods. One of these methods avoids the use of reference voltage generators. The circuit performance is analyzed in several aspects through simulation in 130 nm CMOS technology using symmetric power-supply of  $\pm 0.6$  V. In all designs a special care has been taken to reduce the area with respect to prior works of the same research group, without significantly impairing other performance features for the application as synapse elements in CNN, such as low power and low distortion level.

*Keywords*: Electronic synapse, CNN, CMOS analog multiplier, four-quadrant multiplier, analog signal processing.

## LISTA DE ABREVIATURAS E SIGLAS

A Ampère

AC Alternate Current

ACM Advanced Compact MOSFET

ADC Analog to Digital Converter

ADS Advanced Design System

AMP OP Amplificador Operacional

BSIM Berkeley Short-channel IGFET Model

CA Corrente Alternada

CAPES Coordenação de Aperfeiçoamento de Pessoal de Nível Superior

CC Corrente Contínua

CI Circuito Integrado

CMOS Complementary Metal-Oxide Semiconductor

CNN Cellular Neural Network

dB Decibel

DC Direct Current

EDA Electronic Design Automation

EKV Enz-Krummenacher-Vittoz model)

FSR Full Signal Range

Hz Hertz

IBM International Business Machines

JICS The Journal of Integrated Circuits and System

LASCAS Latin American Symposium on Circuits and Systems

LCCI Laboratório de Concepção de Circuitos Integrados

M4Q Multiplicador de Quatro Quadrantes

MATLAB *MATrix LABoratory*

MEP Mosis Educational Program

MOS Metal-Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MOSIS Metal Oxide Semiconductor Implementation Service

(Integrated Circuit Fabrication Service)

mV Milivolt

nA Nanoampère

nm Nanometro

OTA Operational Transconductance Amplifier

RMS Root Mean Square

SBCCI Symposium on Circuits and Systems Design

TBJ Trasistor Bipolar Junction

THD Total Harmonic Distortion

V Volt

V<sub>TH</sub> Tensão de Limiar (*Threshold*)

$i_{in}$  Corrente de Entrada

i<sub>out</sub> Corrente de Saída

$V_{0v}$  Sobretensão de Condução

V<sub>GS</sub> Tensão Porta-Fonte (*Gate-Source*)

VLSI Very Large-Scale Integration

WSLVC Wide Swing Low Voltage Cascode

## LISTA DE SÍMBOLOS

μ Mobilidade global dos portadores

μm Micrometro

C'<sub>OX</sub> Capacitância por unidade de área do óxido

$g_{md}$  Transcondutância de dreno  $g_{mg}$  Transcondutância de porta  $g_{ms}$  Ttranscondutância de fonte  $I_B$  Corrente de polarização

I<sub>D</sub> Corrente de dreno

$\begin{array}{lll} i_f & & & & & \\ Ccorrente normalizada direta \\ I_F & & & & \\ Corrente de saturação direta \\ I_R & & & & \\ Corrente de saturação reversa \\ i_r & & & & \\ Corrente normalizada reversa \\ I_S & & & & \\ Corrente de normalização \\ \end{array}$

k Parâmetro de TranscondutânciaL Comprimento efetivo do canal

n Fator de rampa

q Magnitude da carga eletrônica

$Q'_{ID}$  Densidade de carga de inversão no lado do dreno  $Q'_{IS}$  Densidade de carga de inversão no lado da fonte  $V_{DB}$  Tensão entre os terminais de dreno e substrato

V<sub>DBSAT</sub> Tensão entre os terminais de dreno e substrato no limiar da saturação

V<sub>DD</sub> Tensão de alimentação positiva

V<sub>DS</sub> Tensão entre os terminais de dreno e fonte

V<sub>DSSAT</sub> Tensão entre os terminais de dreno e fonte no limiar da saturação

$V_{GB}$  Tensão entre os terminais de porta e substrato  $V_{P}$  Tensão de "pinch-off" ou estrangulamento  $V_{SB}$  Tensão entre os terminais de fonte e substrato

V<sub>SS</sub> Tensão de alimentação negativa

V<sub>TON(P)</sub> Tensão de limiar em equilíbrio do transistor canal N (P)

W Largura efetiva do canal

λ Parâmetro de ajuste do comprimento da seção do dreno

φ<sub>t</sub> Potencial termodinâmico

# LISTA DE ILUSTRAÇÕES

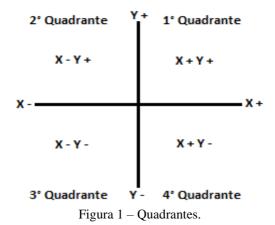

| Figura 1 – Quadrantes.                                                                        | 26   |

|-----------------------------------------------------------------------------------------------|------|

| Figura 2 – Multiplicador por Dispositivo Não Linear                                           | 27   |

| Figura 3 – Amplificador de Transcondutância.                                                  |      |

| Figura 4 – Multiplicador Baseado em Amplificador de Transcondutância: (a) Adiçã               |      |

| pequeno sinal $i_2$ à corrente de polarização; (b) Utilização de segundo transcondutor        | para |

| geração de $i_2$ ; (c) Célula de Gilbert utilizando três transcondutores                      |      |

| Figura 5 – Esquemas de Cancelamento por Combinação de: (a) Quadradores; (b)                   |      |

| Multiplicadores de 1 quadrante.                                                               | 29   |

| Figura 6 – Multiplicadores para aplicação em baixa tensão: (a) baseado em somador             | res  |

| de baixa tensão; (b) baseados em subtratores de baixa                                         | 33   |

| Figura 7 – Multiplicador analógico CMOS escalável, de larga excursão                          | 35   |

| Figura 8 – Multiplicador analógico de quatro quadrantes                                       | 37   |

| Figura 9 – Multiplicador analógico de quatro quadrantes                                       | 38   |

| Figura 10 – Multiplicador analógico CMOS de quatro quadrantes                                 | 39   |

| Figura 11 – Multiplicador analógico CMOS de quatro quadrantes                                 | 40   |

| Figura 12 – Multiplicador analógico de quatro quadrantes no regime de sub-limiar:             | (a)  |

| núcleo; (b) gerador da tensão de referência.                                                  | 41   |

| Figura 13 – Espelho de Corrente Widlar.                                                       | 43   |

| Figura 14 – Espelho de Corrente <i>Cascode</i> .                                              |      |

| Figura 15 – Espelho de Corrente Wilson                                                        |      |

| Figura 16 – Espelho de Corrente Wilson Melhorado.                                             |      |

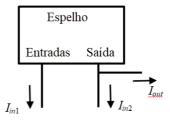

| Figura 17 – Configuração de subtrator de corrente com um espelho                              |      |

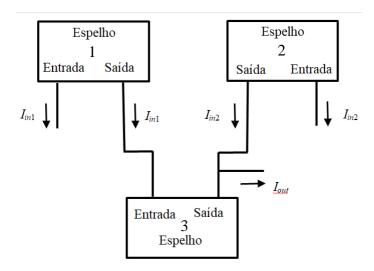

| Figura 18 – Configuração de subtrator de corrente com três espelhos                           |      |

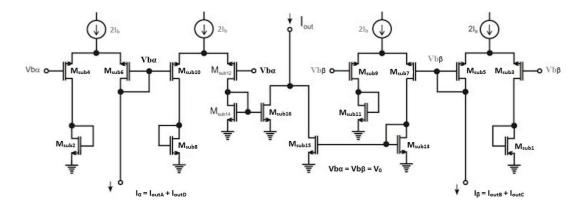

| Figura 19 – Topologia simétrica para o circuito subtrator.                                    |      |

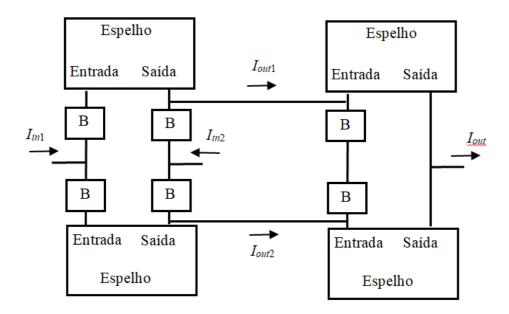

| Figura 20 – Configuração de subtrator de corrente com quatro espelhos                         |      |

| Figura 21 – Diagrama Simplificado da Estrutura de uma Rede Celular Neuronal                   |      |

| Figura 22 – Diagrama de blocos para a Célula Padrão.                                          |      |

| Figura 23 – Diagrama de blocos para a Célula FSR.                                             |      |

| Figura 24 – Arquitetura Completa do Multiplicador Proposto                                    |      |

| Figura 25 – Metade Esquerda do Núcleo do Multiplicador Proposto                               |      |

| Figura 26 – Meia Direita do Núcleo do Multiplicador Proposto                                  |      |

| Figura 27 – Bloco Deslocador de Nível do Multiplicador Completo da Figura 24                  |      |

| Figura 28 – Destaques do Bloco Deslocador de Nível: (a) Lado Direito – Injeção de             |      |

| v <sub>IN1</sub> ; (b) Lado Esquerdo                                                          |      |

| Figura 29 – Blocos para Injeção de Sinal nos Terminais de Fonte dos Núcleos M <sub>3</sub> -M |      |

| (a) e M <sub>1</sub> -M <sub>2</sub> (b)                                                      |      |

| Figura 30 – Bloco de Divisores de Tensão                                                      |      |

| Figura 31 – Bloco Subtrator.                                                                  | 66   |

| Figura 32 – Características DC: Corrente de Saída $vs$ . Tensão de Entrada $v_{IN1}$ ,        |      |

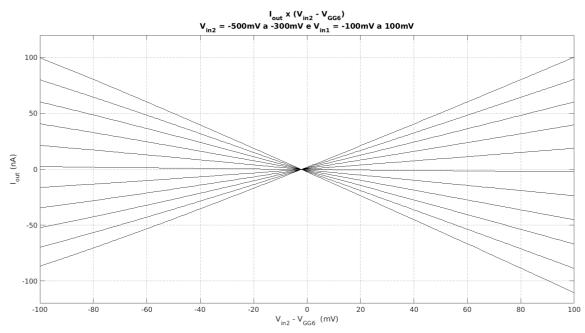

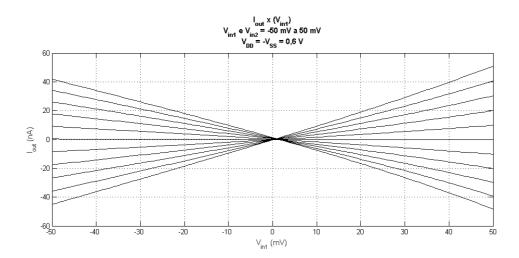

| Parametrizadas por <i>v</i> <sub>IN2</sub>                                                    | 69   |

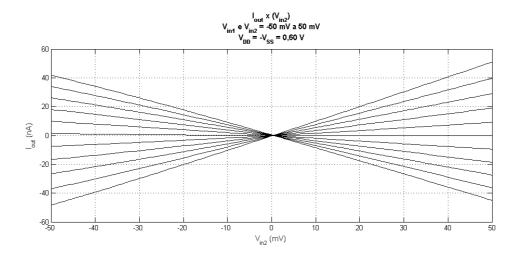

| Figura 33 – Características DC: Corrente de Saída vs. Tensão de Entrada $v_{IN2}$ ,           |      |

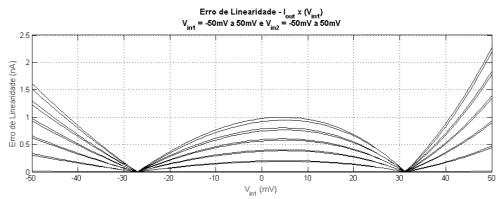

| Parametrizadas por <i>v</i> <sub>IN1</sub> c                                                  |      |

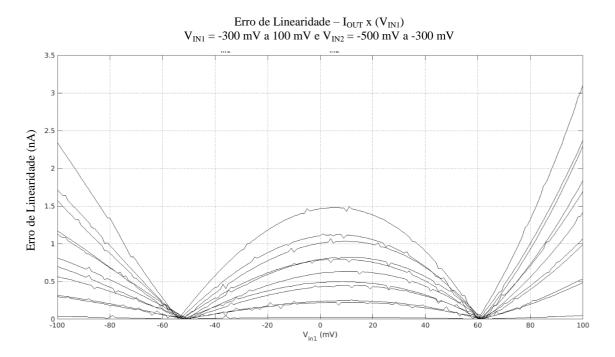

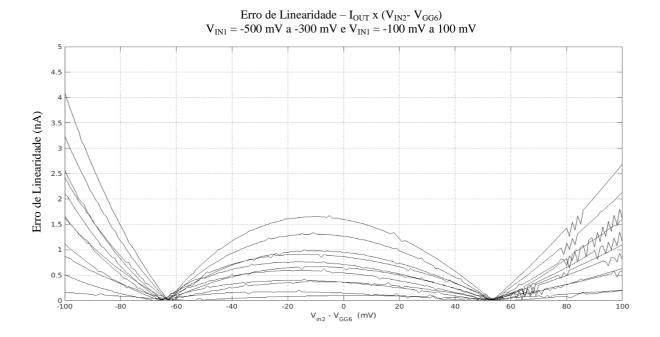

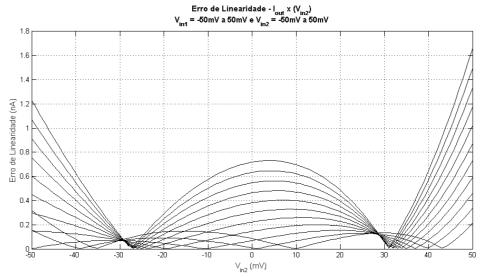

| Figura 34 – Erro de Linearidade Relativo às Características DC da Figura 32                   |      |

| Figura 35 – Erro de Linearidade Relativo às Características DC da Figura 33                   |      |

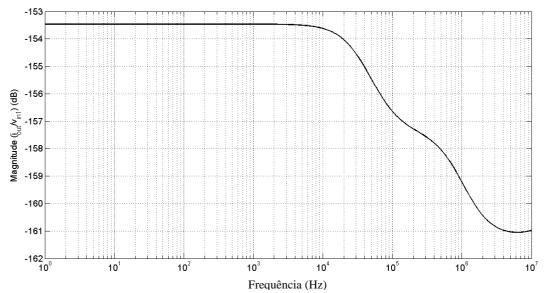

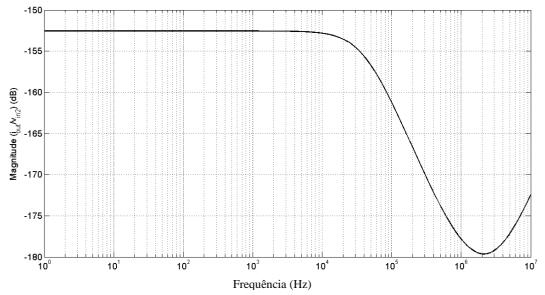

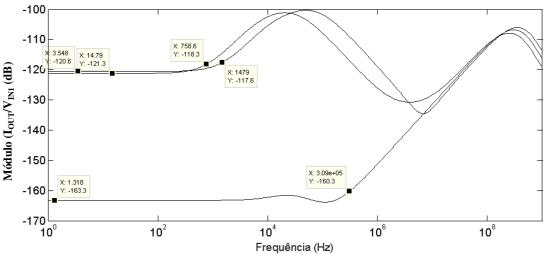

| Figura 36 – Diagrama de Bode de Magnitude do Ganho $i_{OUT}/v_{IN1}$ com $v_{IN2}$ constante  |      |

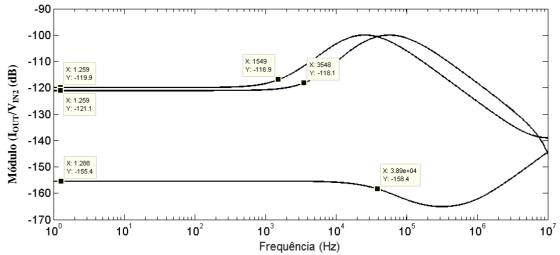

| Figura 37 – Diagrama de Bode de Magnitude do Ganho $i_{OUT}/v_{IN2}$ com $v_{IN1}$ constante  | 72   |

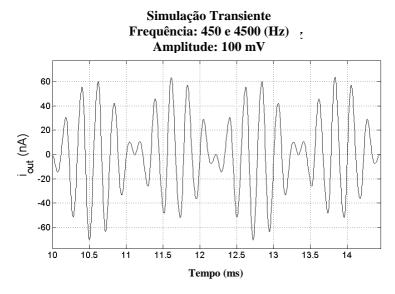

| Figura 38 – Forma de Onda da Corrente de Saída com Entradas Senoidais de 450 Hz e                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------|

| 4,5 kHz e Amplitude de 100 mV73                                                                                                      |

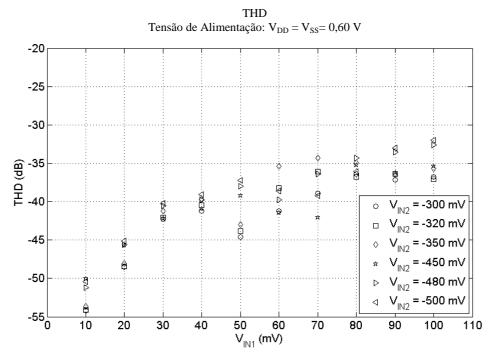

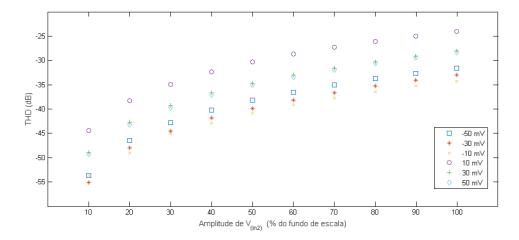

| Figura 39 – THD vs. Amplitude do Sinal de Entrada $v_{IN1}$ , com $V_{DD} = -V_{SS} = 0.6$ V e                                       |

| Temperatura: 27 °C                                                                                                                   |

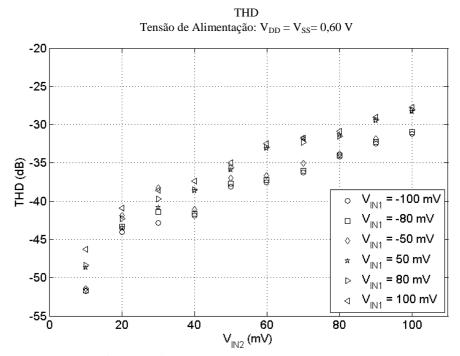

| Figura 40 – THD vs. Amplitude do Sinal de Entrada $v_{IN2}$ , com $V_{DD} = -V_{SS} = 0.6$ V e                                       |

| Temperatura: 27 °C                                                                                                                   |

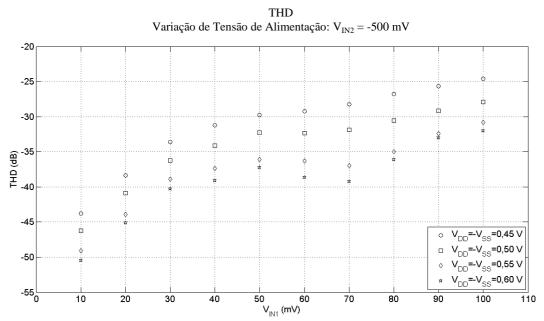

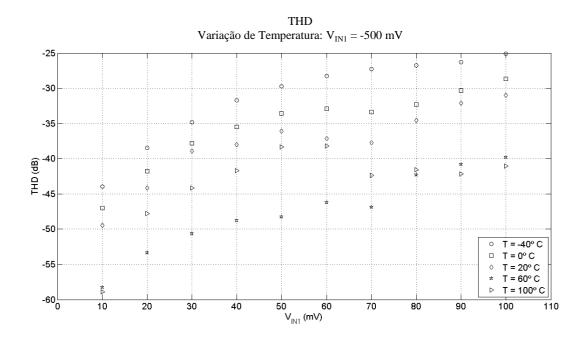

| Figura 41 – THD vs. Amplitude do Sinal de Entrada $v_{IN1}$ , com $v_{IN2} = -500$ mV76                                              |

| Figura 42 – THD vs. Amplitude do Sinal de Entrada $v_{IN1}$ , com $v_{IN2} = -300$ mV77                                              |

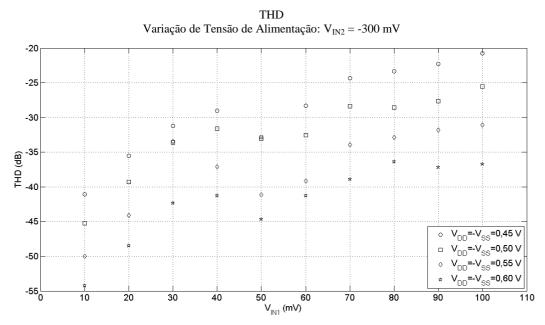

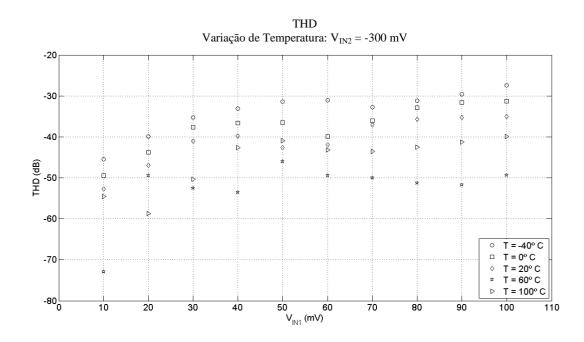

| Figura 43 – THD vs. Amplitude do Sinal de Entrada $v_{IN2}$ , com $v_{IN1}$ = -100 mV77                                              |

| Figura 44 – THD vs. Amplitude do Sinal de Entrada $v_{IN2}$ , com $v_{IN1} = 100 \text{ mV}$ 78                                      |

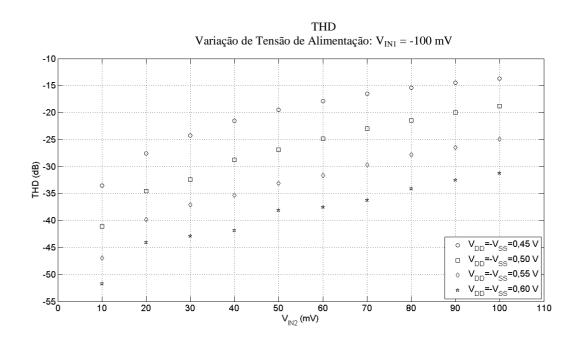

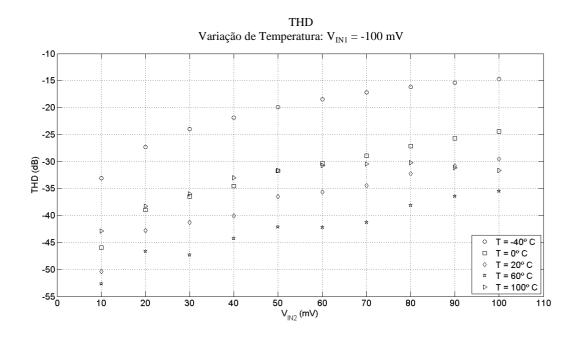

| Figura 45 – THD vs. Amplitude do Sinal de Entrada $v_{IN1}$ , com $v_{IN2} = -500$ mV79                                              |

| Figura 46 – THD vs. Amplitude do Sinal de Entrada $v_{IN1}$ , com $v_{IN2} = -300$ mV79                                              |

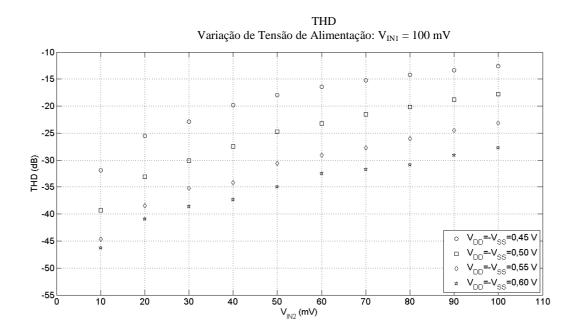

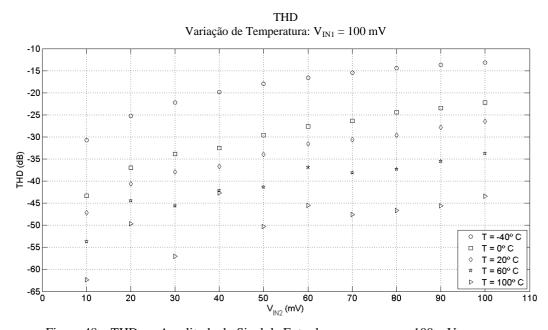

| Figura 47 – THD vs. Amplitude do Sinal de Entrada $v_{IN2}$ , com $v_{IN1}$ = -100 mV80                                              |

| Figura 48 – THD vs. Amplitude do Sinal de Entrada $v_{IN2}$ , com $v_{IN1} = 100 \text{ mV}80$                                       |

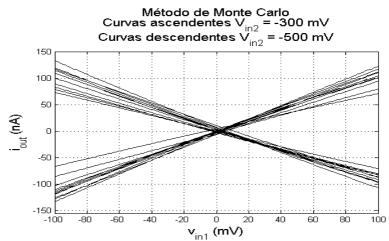

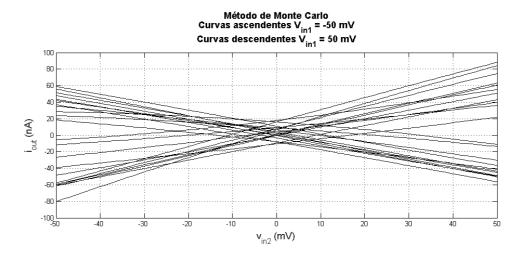

| Figura 49 – Características de Transferência DC com Variações de Processo Utilizando                                                 |

| o Método de Monte Carlo81                                                                                                            |

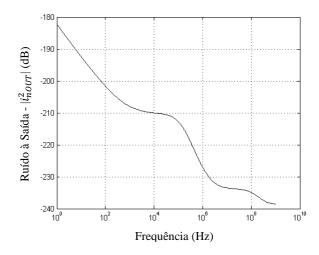

| Figura 50 – Densidade espectral da corrente de ruído à saída do multiplicador82                                                      |

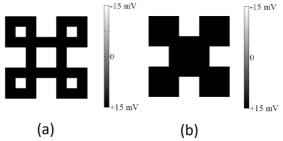

| Figura 51 – Resultados da simulação para a função de processamento de imagem de                                                      |

| preenchimento de buracos: (a) Imagem inicial e (b) Imagem final84                                                                    |

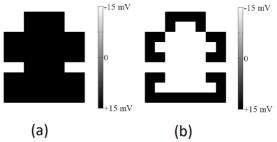

| Figura 52 – Resultados da simulação para a função de processamento de imagem de                                                      |

| detecção de borda: (a) imagem inicial e (b) imagem final84                                                                           |

| Figura 53 – Princípio básico do núcleo multiplicador proposto88                                                                      |

| Figura 54 – Bloco de Média Aritmética                                                                                                |

| Figura 55 – Bloco de Meia Diferença: (a) bloco de diferença; (b) bloco de meia                                                       |

| diferença; (c) bloco de meia diferença com deslocadores de nível90                                                                   |

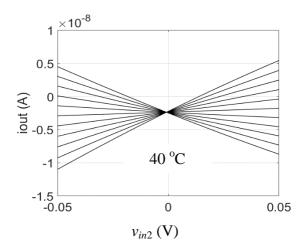

| Figura 56 – Núcleo multiplicador para operação em um único quadrante92                                                               |

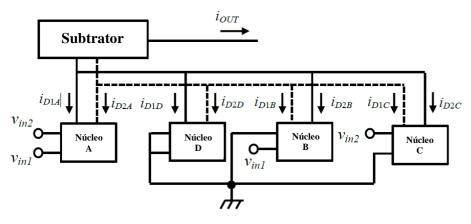

| Figura 57 – Esquema de cancelamento para operação em quatro quadrantes92                                                             |

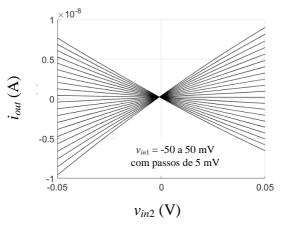

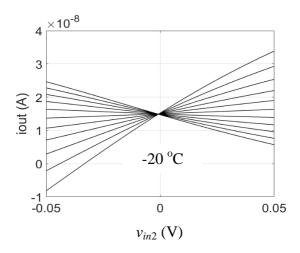

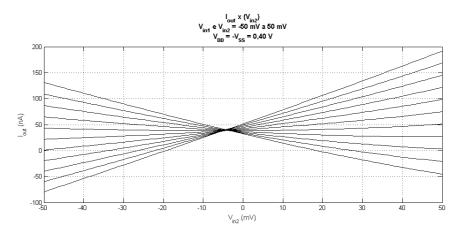

| Figura 58 – Características de transferência DC do multiplicador: $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$                            |

| variando de -50 mV a 50 mV com passos de 5 mV; circuito completo, incluindo o                                                        |

| subtrator94                                                                                                                          |

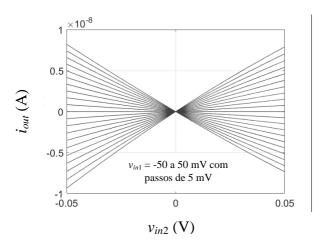

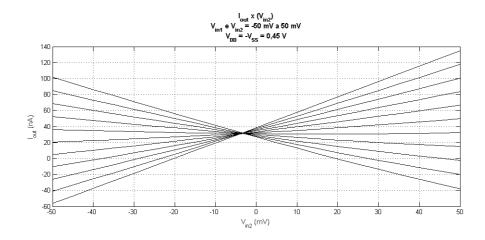

| Figura 59 – Características de transferência DC do multiplicador: $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$                            |

| variando de -50 mV a 50 mV com passos de 5 mV; subtração ideal94                                                                     |

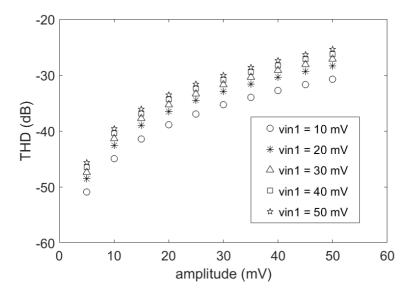

| Figura 60 – Distorção harmônica total do multiplicador: $v_{in2}$ senoidal (100 Hz) e $v_{in1}$                                      |

| constante95                                                                                                                          |

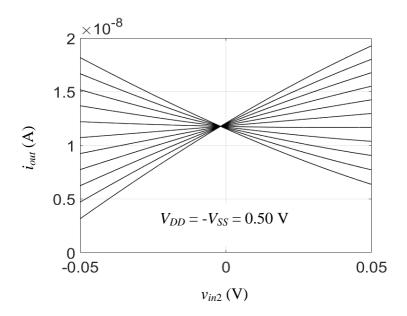

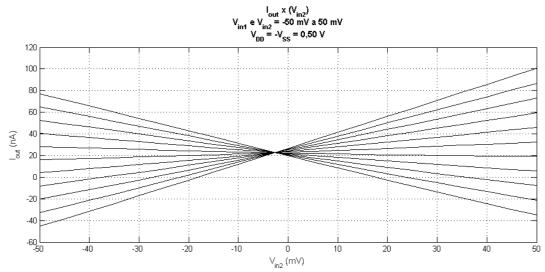

| Figura 61 – Características de transferência DC do multiplicador para tensões de                                                     |

| alimentação de +0,50 V: $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$ variando de -50 mV a 50 mV com passos                                |

| de 10 mV; circuito completo, incluindo o subtrator96                                                                                 |

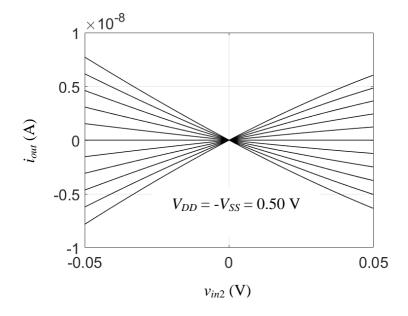

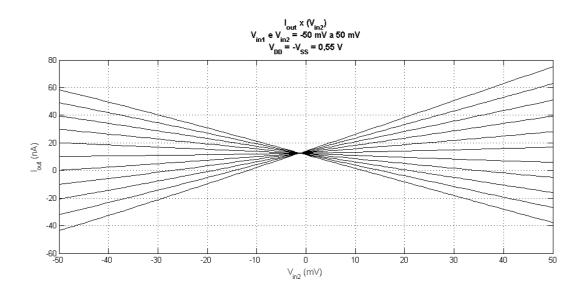

| Figura 62 – Características de transferência DC do multiplicador para tensões de                                                     |

| alimentação de $+0.50 \text{ V}$ : $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$ variando de $-50 \text{ mV}$ a $50 \text{ mV}$ com passos |

| de 10 mV; subtração ideal                                                                                                            |

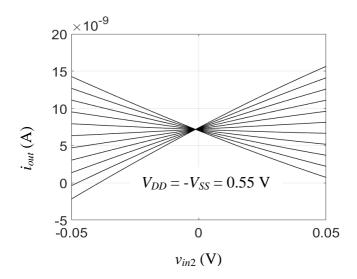

| Figura 63 – Características de transferência DC do multiplicador para tensões de                                                     |

| alimentação de $+0.55 \text{ V}$ : $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$ variando de $-50 \text{ mV}$ a $50 \text{ mV}$ com passos |

| de 10 mV; circuito completo, incluindo o subtrator                                                                                   |

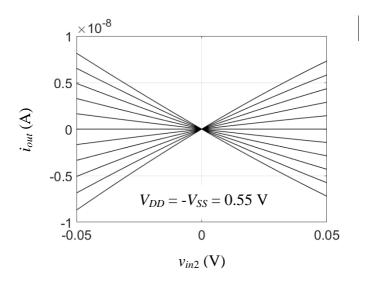

| Figura 64 – Características de transferência DC do multiplicador para tensões de                                                     |

| alimentação de $+0.55$ V: $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$ variando de $-50$ mV a $50$ mV com passos                          |

| de 10 mV; subtração ideal                                                                                                            |

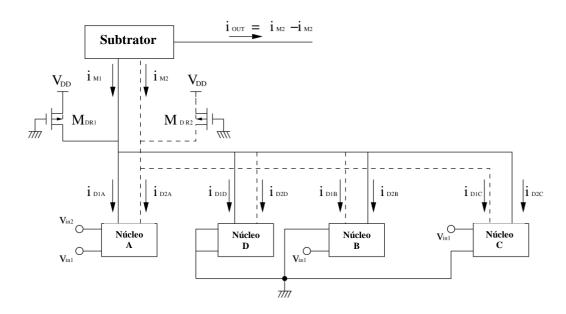

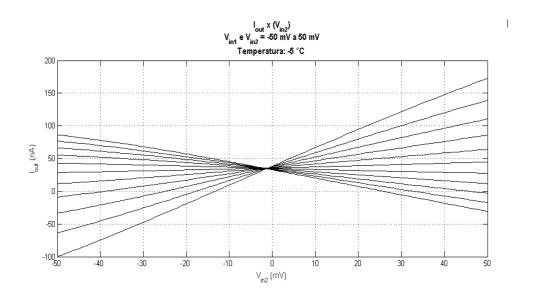

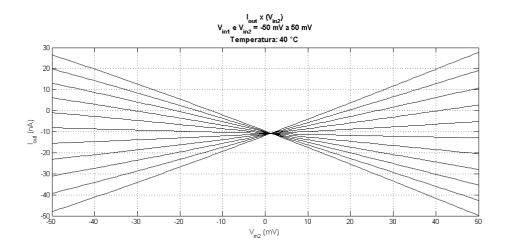

| Figura 65 – Características de transferência DC do multiplicador para temperatura de -                                               |

| $20^{\circ}$ C: $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$ variando de -50 mV a 50 mV com passos de 10 mV98                             |

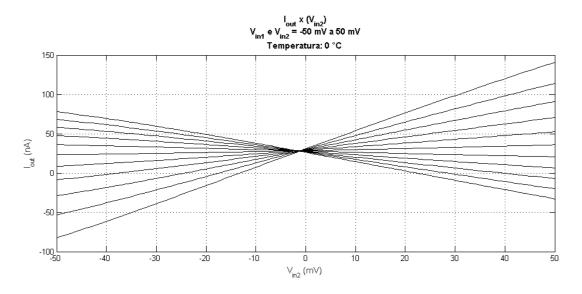

| Figura 66 – Características de transferência DC do multiplicador para temperatura de                                                 |

| $40^{\circ}$ C: $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$ variando de -50 mV a 50 mV com passos de 10 mV98                             |

|                                                                                                                                      |

| Figura 67 – Arquitetura do Subtrator WSLV <i>cascode</i> 102                                                |

|-------------------------------------------------------------------------------------------------------------|

| Figura 68 – Arquitetura completa do multiplicador de quatro quadrantes proposto102                          |

| Figura 69 – Características de transferência DC do multiplicador melhorado: $i_{out}$ vs. $v_{in1}$ ,       |

| com $v_{in2}$ variando de -50 mV a 50 mV com passos de 10 mV; circuito completo,                            |

| incluindo o subtrator                                                                                       |

| Figura 70 – Características de transferência DC do multiplicador melhorado: $i_{out}$ vs. $v_{in2}$ ,       |

| com $v_{in1}$ variando de -50 mV a 50 mV com passos de 10 mV105                                             |

| Figura 71 – Erro de Linearidade Relativo às Características DC da Figura 33105                              |

| Figura 72 – Erro de Linearidade Relativo às Características DC da Figura 33105                              |

| Figura 73 – Distorção Harmônica Total do multiplicador: $v_{in2}$ senoidal (100 Hz) e $v_{in1}$             |

| constante nos valores de -50 mVa 50 mVcom passos de 20 mV. Fundo de escala de $v_{in2}$ :                   |

| 50 mV106                                                                                                    |

| Figura 74 – Diagrama de Bode de Magnitude do Ganho $i_{OUT}/v_{IN1}$ com $v_{IN2}$ constante. 107           |

| Figura 75 – Diagrama de Bode de Magnitude do Ganho $i_{OUT}/v_{IN2}$ com $v_{IN1}$ constante. 108           |

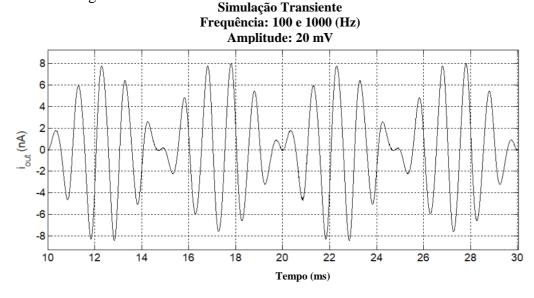

| Figura 76 – Forma de onda da corrente de saída com entradas senoidais de 100 Hz e 1,0                       |

| kHz e amplitude de 20 mV108                                                                                 |

| Figura 77 – Características de transferência DC do multiplicador para tensões de                            |

| alimentação de +0,4 V: $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$ variando de -50 mV a 50 mV com passos de     |

| 10 mV                                                                                                       |

| Figura 78 – Características de transferência DC do multiplicador para tensões de                            |

| alimentação de +0,45 V: $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$ variando de -50 mV a 50 mV com passos       |

| de 10 mV                                                                                                    |

| Figura 79 – Características de transferência DC do multiplicador para tensões de                            |

| alimentação de +0,5 V: $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$ variando de -50 mV a 50 mV com passos de     |

| 10 mV                                                                                                       |

| Figura 80 – Características de transferência DC do multiplicador para tensões de                            |

| alimentação de $+0,55$ V: $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$ variando de $-50$ mV a $50$ mV com passos |

| de 10 mV                                                                                                    |

| Figura 81 – Características de transferência DC do multiplicador para temperatura de -                      |

| $5^{\circ}$ C: $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$ variando de -50 mV a 50 mV com passos de 10 mV111    |

| Figura 82 – Características de transferência DC do multiplicador para temperatura de 0                      |

| $^{\circ}$ C: $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$ variando de -50 mV a 50 mV com passos de 10 mV112     |

| Figura 83 – Características de transferência DC do multiplicador para temperatura de 40                     |

| $^{\circ}$ C: $i_{out}$ vs. $v_{in2}$ , com $v_{in1}$ variando de -50 mV a 50 mV com passos de 10 mV112     |

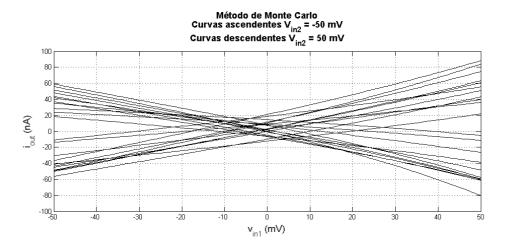

| Figura 84 – Características de transferência DC com variações de processo utilizando o                      |

| Método de Monte Carlo, $i_{OUT}$ x $v_{in1}$ com variações de $v_{in2}$ nos extremos: -50 mV e 50           |

| mV                                                                                                          |

| Figura 85 – Características de transferência DC com variações de processo utilizando o                      |

| Método de Monte Carlo, $i_{OUT}$ x $v_{in2}$ com variações de $v_{in1}$ nos extremos: -50 mV e 50           |

| mV                                                                                                          |

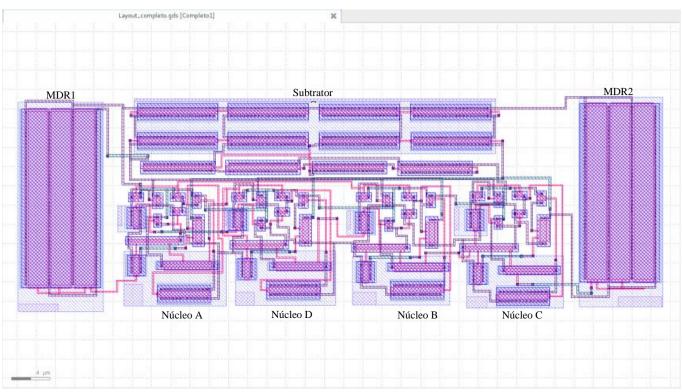

| Figura 86 – Leiaute do multiplicador analógico completo                                                     |

## LISTA DE TABELAS

| Tabela 1 – Resumo de Modos Operacionais dos Multiplicadores               | 31  |

|---------------------------------------------------------------------------|-----|

| Tabela 2 – Dimensões dos Transistores e Área Ativa.                       | 83  |

| Tabela 3 – Dimensões dos Transistores e Área Ativa.                       | 99  |

| Tabela 4 – Dimensões dos Transistores e Área Ativa.                       | 114 |

| Tabela 5 – Síntese das Características de Desempenho dos Multiplicadores. | 117 |

## **SUMÁRIO**

| 1. II | NTRO   | DUÇÃO                                                         | 18 |

|-------|--------|---------------------------------------------------------------|----|

| 1.1.  | . Coi  | ntextualização                                                | 18 |

| 1.2.  | Ob     | jetivo                                                        | 21 |

| 1.2.  | 1. (   | Objetivos Específicos                                         | 21 |

| 1.3.  | Jus    | tificativas                                                   | 22 |

| 1.4.  | Org    | ganização do Texto                                            | 23 |

| 2. F  | UND    | AMENTAÇÃO TEÓRICA                                             | 25 |

| 2.1.  | . Mu   | ltiplicadores                                                 | 25 |

| 2     | 2.1.1. | Princípio de Operação dos Multiplicadores                     | 25 |

| 2     | 2.1.2. | Multiplicação por Dispositivo Não-Linear                      | 26 |

| 2     | 2.1.3. | Multiplicação por Dispositivo de Transcondutância Programável | 27 |

| 2     | 2.1.4. | Esquemas de Cancelamento                                      | 28 |

| 2     | 2.1.5. | Tipos de Multiplicadores                                      | 30 |

| 2.2.  | Esp    | pelhos de Corrente em Tecnologia CMOS                         | 42 |

| 2.3.  | Sub    | otratores de Corrente                                         | 48 |

| 2.4.  | Red    | des Celulares Neuronais (CNN)                                 | 51 |

| 3. N  | MULTI  | PLICADOR ANALÓGICO CMOS MUITO COMPACTO PARA                   |    |

| APLIC | CAÇÃ(  | D EM SINAPSES DE CNN                                          | 56 |

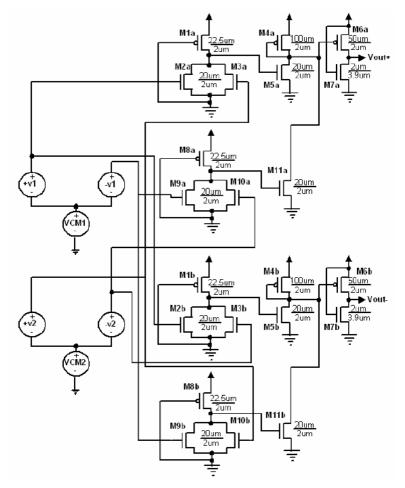

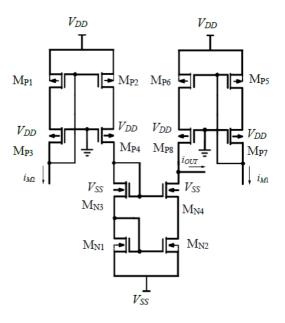

| 3.1.  | Arc    | quitetura Proposta                                            | 56 |

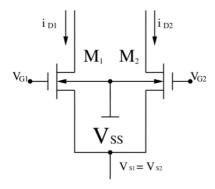

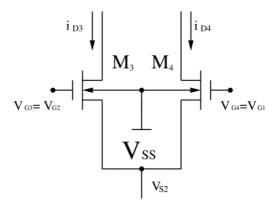

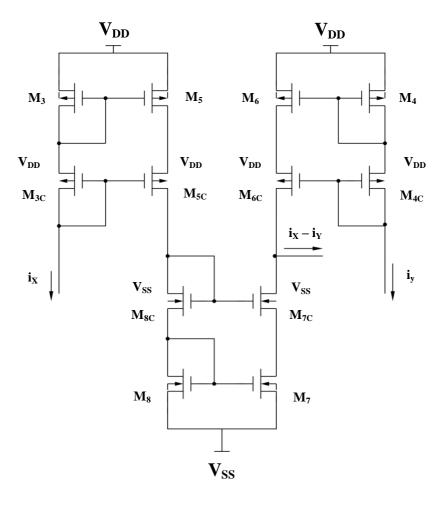

| 3     | .1.1.  | Núcleos do Multiplicador                                      | 58 |

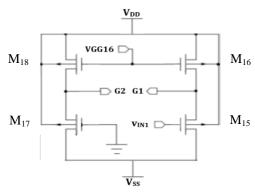

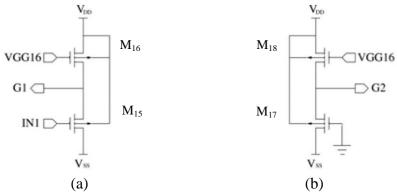

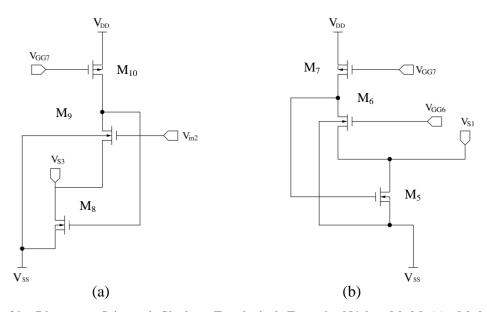

| 3     | .1.2.  | Transferência de Sinal para os Terminais de Porta dos Núcleos | 61 |

| 3     | .1.3.  | Transferência de Sinal para os Terminais de Fonte dos Núcleos | 63 |

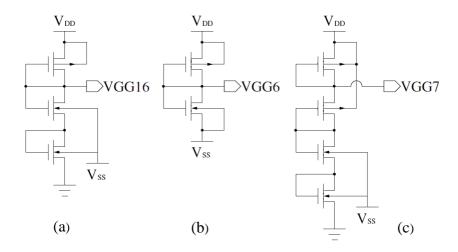

| 3     | 5.1.4. | Tensões de Referência                                         | 65 |

| 3.2.  | Sub    | otrator de Corrente Cascode                                   | 66 |

| 3.3.  | Co     | nsiderações sobre Modularidade                                | 67 |

| 3.4.  | Res    | sultados de Simulação e Análise de Desempenho                 | 68 |

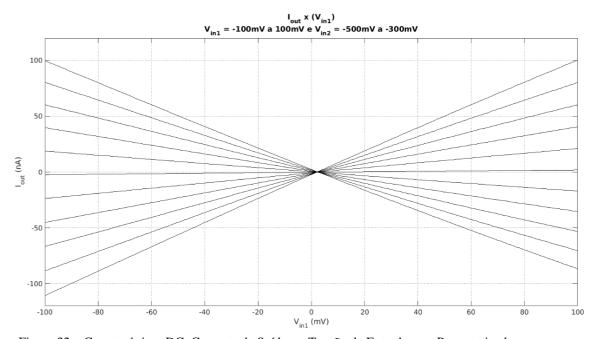

| 3     | 3.4.1. | Características de Transferência DC                           | 68 |

| 3     | 3.4.2. | Erro de Linearidade                                           | 69 |

| 3     | 3.4.3. | Banda de Passagem                                             | 71 |

| 3     | 3.4.4. | Simulação no Domínio do Tempo                                 | 73 |

| 3     | 3.4.5. | Distorção Harmônica Total (THD)                               | 73 |

| 3     | 5.4.6. | Análise da THD com Variações das Tensões de Alimentação       | 76 |

## SUMÁRIO

|     | 3.4.7.            | Análise da THD com Variações da Temperatura                        | 78  |

|-----|-------------------|--------------------------------------------------------------------|-----|

|     | 3.4.8.            | Características de Transferência DC com Variações de Processo      | 81  |

|     | 3.4.9.            | Análise de Ruído na Saída                                          | 82  |

|     | 3.4.10.           | Potência DC                                                        | 82  |

|     | 3.4.11.           | Considerações sobre Área                                           | 83  |

|     | 3.4.12.           | Operação como sinapse de uma CNN                                   | 84  |

| 3.  | 5. Con            | siderações Finais                                                  | 85  |

| 4.  | MULTII            | PLICADOR ANALÓGICO CMOS DE QUATRO QUADRANTES SE                    | M   |

| GER | ADORE             | S DE TENSÃO DE REFERÊNCIA                                          | 87  |

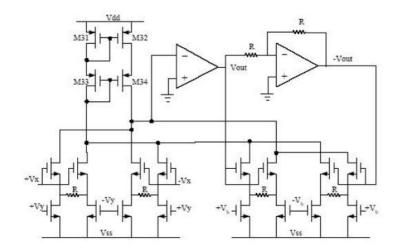

| 4.  | 1. Arq            | uitetura Proposta                                                  | 87  |

|     | 4.1.1.            | Principio de Operação                                              | 87  |

|     | 4.1.2.            | Bloco de Média Aritmética                                          | 88  |

|     | 4.1.3.            | Bloco de Meia-Diferença                                            | 90  |

| 4.  | 2. Resi           | ultados de Simulação e Análise de Desempenho                       | 93  |

|     | 4.2.1.            | Características de Transferência DC                                | 93  |

|     | 4.2.2.<br>Aliment | Características de Transferência DC com Variação de Tensão de ação | 95  |

|     | 4.2.3.            | Características de Transferência DC com Variação de Temperatura    | 97  |

|     | 4.2.4.            | Potência DC                                                        | 99  |

|     | 4.2.5.            | Considerações sobre Área                                           | 99  |

| 4.  | 3. Con            | siderações Finais                                                  | 100 |

| 5.  | VERSÃ             | O MELHORADA DO MULTIPLICADOR ANALÓGICO CMOS DE                     |     |

| QUA | ATRO Q            | UADRANTES SEM GERADORES DE TENSÃO DE REFERÊNCIA .                  | 101 |

| 5.  | 1. Arq            | uitetura Melhorada                                                 | 101 |

| 5.  | 1.1. St           | ubtrator e Fontes de Corrente Auxiliares                           | 101 |

| 5.  | 1.2. C            | onsiderações sobre o Dimensionamento                               | 103 |

| 5.  | 2. Resi           | ultados de Simulação e Análise de Desempenho                       | 103 |

|     | 5.2.1.            | Características de Transferência DC                                | 104 |

|     | 5.2.2.            | Banda de Passagem                                                  | 107 |

|     | 5.2.3.            | Simulação no Domínio do Tempo                                      | 108 |

|     | 5.2.4.            | Características de Transferência DC com Variação de Tensão de      | 100 |

|     |                   | ação                                                               |     |

|     | 5.2.5.            | Características de Transferência DC com Variação de Temperatura    |     |

|     | 5.2.6.            | Características de Transferência DC com Variações de Processo      |     |

|     | 5.2.7.            | Potência DC                                                        |     |

|     | 528               | Considerações sobre Área                                           | 114 |

## SUMÁRIO

| 5.2   | 2.9. Leiaute do Circuito                          | 115   |

|-------|---------------------------------------------------|-------|

| 5.3.  | Considerações Finais                              | 116   |

| 6. Al | NÁLISE COMPARATIVA ENTRE OS MULTIPLICADORES ANALÓ | GICOS |

| CMOS  |                                                   | 117   |

| 7. CC | ONCLUSÃO                                          | 119   |

| 7.1.  | Sugestões para Trabalhos Futuros                  | 121   |

| 7.2.  | Divulgação da Pesquisa                            | 122   |

| REFER | ÊNCIAS BIBLIOGRÁFICAS                             | 123   |

INTRODUÇÃO 18

## 1. INTRODUÇÃO

## 1.1. Contextualização

Próteses retinianas eletrônicas se apresentam na atualidade como uma solução viável e promissora para os problemas de visão subnormal ou cegueira completa oriundos da degeneração da retina (TOMBRAN-TINK et al., 2007) e (MARTINS; SOUSA, 2009). Tais próteses consistem de microchips que podem substituir parcial ou totalmente a retina, podendo incluir funções como: foto-recepção, interação com centros avançados de processamento do sistema nervoso, filtragem temporal e espacial, ajuste de ganho e quantização adaptativa (SANTANA, 2013).

As próteses totalmente implantáveis são constituídas por uma matriz de milhares de microelementos fotossensíveis (fotodiodos ou fototransistores), circuitos eletrônicos de processamento de imagem e eletrodos, cuja função é capturar os sinais elétricos que codificam a informação de imagem e os encaminhar para o nervo ótico. O processamento do sinal visual através da retina, deste a foto-recepção até a estimulação do nervo ótico, inclui operações que são melhor desempenhadas pixel a pixel, o que requer uma alta densidade de integração dos circuitos eletrônicos.

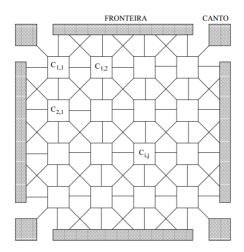

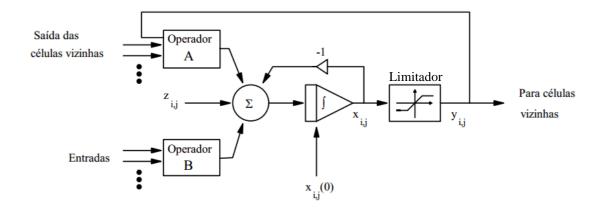

Dentre as possibilidades de implementação de próteses retinianas, os sistemas biomórficos de modelagem da retina compreendem circuitos eletrônicos analógicos que procuram imitar o processamento de imagem de forma aproximada àquela que ocorre ao longo das camadas de células biológicas. Algumas implementações biomórficas são extremamente simples e compactas (MAHER et al., 1989), (ZAGHLOUL; BOAHEN, 2004a,b), contudo, muito provavelmente, não comportam modificações para a melhora de desempenho ou para expansão das funções. Por outro lado, sistemas biomórficos que utilizam rede celular neuronal ou CNN² analógica (CHUA; ROSKA, 2002), (CARMONA-GÁLAN et al., 2003), (HEGT et al., 1998), possibilitam um alto grau de reconfigurabilidade. Uma CNN é composta por vários blocos estruturais, entre os quais, multiplicadores (sinapses), somadores, integradores, grampeadores ou limitadores.

-

<sup>&</sup>lt;sup>2</sup> Cellular Neural Network

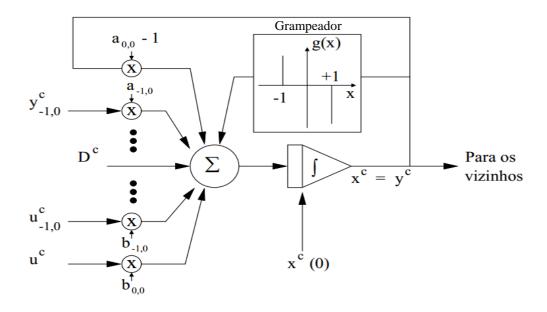

Num trabalho anterior da equipe do Laboratório de Concepção de Circuitos Integrados do Departamento de Engenharia Elétrica da UFBA, desenvolvido no contexto da tese de doutorado do professor Edson Pinto Santana (SANTANA, 2013), foi concebida, projetada, simulada, desenhada na forma de leiaute e fabricada na tecnologia CMOS³ IBM® 0.13 μm uma CNN com características específicas para a futura reprodução de funções relacionadas à visão precoce (*early vision*), que se refere aos estágios da visão que envolvem a captura, pré-processamento e codificação da informação visual, mas não envolvem interpretação ou outro processamento cognitivo da informação visual, e que são funções próprias da retina humana (CARMONA-GÁLAN et al., 2003). A célula FSR⁴ que consiste na estrutura básica desta rede inclui uma arquitetura original de multiplicador de sinais analógicos, que sintetiza as sinapses, ou seja, a ponderação dos sinais de entrada das células por coeficientes associados à função a ser realizada.

Na arquitetura do multiplicador proposta em (SANTANA, 2013) e (SANTANA et al., 2012a,b), compacta e de baixo consumo, uma entrada é um sinal de tensão e a outra, bem como a saída, são sinais de corrente. A entrada em corrente é utilizada para implementar cada operador sináptico (coeficiente), possibilitando uma programação analógica em um contexto contínuo. A entrada em tensão permite que o mesmo sinal seja aplicado a várias outras conexões sinápticas. A saída em corrente torna prescindível o uso de circuitos somadores. Vários blocos do multiplicador podem ser compartilhados entre sinapses de uma mesma célula e entre células de uma rede, o que viabilizou a economia em área de silício. Os demais blocos necessários à síntese de uma célula FSR, integrador e grampeador (clamper) foram extraídos de publicações científicas nesta área e incorporados ao circuito. Redes celulares neuronais de uma e duas dimensões foram simuladas em aplicações relevantes de processamento de imagens binárias (SANTANA, 2013), (SANTANA et al., 2012a,b), assim como em operações de filtragem de baixa ordem de imagens em escala de cinza (ANDRADE, 2013), (ANDRADE, 2015), apresentando resultados satisfatórios. Foram fabricados dois circuitos integrados na tecnologia CMOS IBM® 0,13 µm (IBM, 2010), um incluindo o multiplicador de quatro quadrantes utilizado na sinapse da célula FSR e uma CNN unidimensional de oito células e outro incluindo uma CNN bidimensional de 64 células (8 x 8). Em

\_

<sup>&</sup>lt;sup>3</sup> Complementary Metal-Oxide Semiconductor

<sup>&</sup>lt;sup>4</sup> Full Signal Range

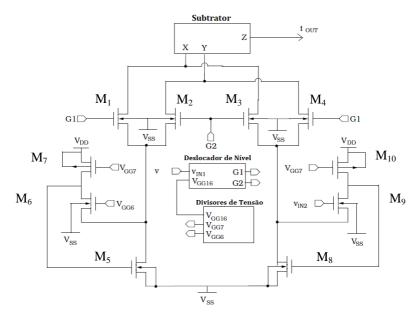

(CARDOSO; SCHNEIDER; SANTANA, 2018) foram introduzidas alterações na arquitetura de multiplicador analógico de (SANTANA, 2013), (SANTANA et al., 2012a,b) para torná-la menos sensível à tensão de alimentação, aspecto importante quando o dispositivo de aplicação é alimentado por baterias e apresenta difícil acessibilidade, como é o caso de circuitos implantados no corpo humano. Convém ressaltar que características de desempenho dos circuitos multiplicadores de (SANTANA, 2013), (SANTANA et al., 2012a,b) e de (CARDOSO; SCHNEIDER; SANTANA, 2018), como erro de linearidade, distorção harmônica total, banda de frequências, ruído, entre outras, foram analisadas por meio de simulação, exibindo níveis aceitáveis.

No entanto, limitações de linearidade na operação dos transistores de entrada terminaram por requerer valores muito baixos de corrente de entrada e, por isto, observaram-se dificuldades em fazer uma caracterização experimental dos circuitos fabricados, uma vez que os valores destas correntes ficam mascarados por ruído externo ao circuito. Além disto, a indispensabilidade da utilização de conversores tensãocorrente para se obterem os sinais representativos dos coeficientes (pesos sinápticos), a divergência entre a faixa de variação dos valores de tensão que representam os pixels e os níveis gerados pelo circuito de sensoriamento, bem como a complexidade do circuito, são também fatores que acabam por elencar necessários aprimoramentos. Os conversores tensão-corrente são redes complementares ao circuito principal, que elevam o consumo de energia e o dispêndio de área de silício, além de eventualmente introduzir alguma contribuição ao nível de distorção do multiplicador. Pelo fato de ser muito baixa a faixa de variação dos sinais de tensão representativos dos pixels nos multiplicadores de (SANTANA, 2013), (SANTANA et al., 2012a,b) e de (CARDOSO; SCHNEIDER; SANTANA, 2018), provavelmente será necessário introduzir uma rede de condicionamento entre eles e o circuito de sensoriamento, o que acrescentará ainda mais área, consumo e complexidade. Finalmente, tais circuitos multiplicadores por si mesmos já são bastante complexos, compreendendo muitos transistores e ocupando uma área apreciável. Todo este panorama justifica os objetivos da proposta de pesquisa aqui apresentada.

## 1.2. Objetivo

O objetivo mais abrangente deste projeto é dar continuidade a uma linha de pesquisa voltada ao estudo e concepção de próteses retinianas eletrônicas para recuperação parcial da visão em casos de degeneração da retina. Este trabalho estará concentrado na análise de desempenho de arquiteturas de multiplicadores analógicos em tecnologia CMOS, para operação como elementos de sinapse, no que concerne à distorção, consumo de energia, área de silício ocupada, sensibilidade à variação das tensões de alimentação, da temperatura e de parâmetros tecnológicos e seu impacto no desempenho da rede neuronal celular.

Os principais objetivos desta proposta de trabalho baseiam-se em realizar modificações e melhoramentos nas arquiteturas de multiplicadores analógicos, adaptando-as para operar com sinais de entrada exclusivamente em tensão, com níveis coadunáveis com o circuito de sensoriamento, e visando: diminuição de área ativa; baixa sensibilidade em relação às variações de temperatura, tensão de alimentação e parâmetros tecnológicos; operação com baixa potência. Outrossim, como uma continuação ao trabalho desenvolvido, pretende—se realizar uma análise minuciosa sobre o desempenho das estruturas alternativas de multiplicador propostas, enquanto blocos de circuito isolados e incorporadas à CNN analógica de (SANTANA, 2013), (SANTANA et al., 2012a,b), analisando a confiabilidade da operação desta como processador de imagens.

## 1.2.1. Objetivos Específicos

Os objetivos específicos deste trabalho são:

(i) Proposição de arquiteturas alternativas para os multiplicadores que implementam as sinapses da célula FSR de (SANTANA, 2013), (SANTANA et al., 2012a,b) com as seguintes características: entradas em tensão e saída em corrente; faixa de variação das tensões de entrada em níveis de fácil discriminação do ruído e compatíveis com sinais gerados pelo circuito de sensoriamento, de modo a reduzir os requisitos e complexidade dos condicionadores de sinal; baixa complexidade;

possibilidade de reaproveitamento de blocos dentro da célula FSR e dentro da rede neuronal.

(ii) Análise de desempenho, por meio de simulação, das arquiteturas de multiplicador propostas, nos aspectos: linearidade e distorção harmônica total; banda de frequências; sensibilidade à variação de parâmetros tecnológicos; sensibilidade à variação da tensão de alimentação; sensibilidade à variação de temperatura; ruído; potência; área ativa.

#### 1.3. Justificativas

Os multiplicadores analógicos têm um papel essencial em alguns sistemas de processamento de sinais analógicos, como as redes neuronais celulares (CNN), onde atuam como elementos sinápticos (CHUA; YANG, 1988). Na implementação de multiplicadores analógicos em tecnologia CMOS, a arquitetura deve lidar com os requisitos atuais de baixa tensão, o que torna os circuitos em modo corrente preferíveis (BAHARMAST; MOWLAVI, 2016) e (BEYRAGHI; KHOEI, 2015). Além disto, o sinal de saída do multiplicador deve ser uma corrente para simplificar a soma que é executada entre os produtos resultantes na saída das sinapses. No entanto, em redes de processamento de alta densidade, como é o caso da CNN, há a necessidade de se aplicar o mesmo sinal a várias entradas de células, a fim de ser ponderado pelos operadores sinápticos. Este aspecto é determinante para a escolha da topologia do multiplicador. Para conseguir uma implementação mais compacta do circuito, o modo tensão nas entradas do multiplicador é bastante adequado. Entradas em modo corrente demandam a introdução de muitos espelhos de corrente para reproduzir os sinais nas entradas de vários multiplicadores, implicando em mais área de silício para a implementação do circuito. Multiplicadores com sinais de entrada em modo misto (SANTANA; FREIRE; CUNHA, 2012) e (CARDOSO; SCHNEIDER; SANTANA, 2018), onde os sinais de entrada de corrente correspondem aos operadores sinápticos (pesos), demandam o uso de conversores tensão-corrente para gerar e programar corretamente os valores dos coeficientes.

Portanto, os projetistas de circuitos integrados analógicos em tecnologia CMOS devem enfrentar o desafio de conciliar as restrições das tecnologias submicrométricas, entre as quais o ambiente de baixa tensão, às especificações de desempenho das

arquiteturas multiplicadoras em modo tensão na entrada (MAHMOUD, 2009), (KUMNGERN; CHANWUTITUM, 2008). O método de aplicação do sinal de tensão é uma questão crítica, uma vez que muitas vezes requer o uso de amplificadores e/ou inversores e, portanto, os elementos de polarização associados, como fontes e sorvedores de corrente bem regulados e referências de tensão de alta precisão. Além da complexidade que tais circuitos auxiliares (amplificadores, inversores e elementos de polarização) adicionam à topologia do multiplicador, o comportamento deste pode se tornar extremamente sensível à variação da tensão de alimentação, a menos que uma rede ainda mais complexa seja incorporada.

Como o número de elementos de sinapse em uma CNN voltada ao processamento de imagens é extremamente alto (em geral, cerca de dezoito vezes o número de células, que, por sua vez, pode ser da ordem de dezenas a centenas de milhares), (CHUA; ROSKA, 2002), a simplicidade é uma característica obrigatória em arquiteturas multiplicadoras para essa finalidade. Neste trabalho, propomos novas arquiteturas de multiplicadores para aplicação como elementos de sinapse em CNN, investindo um esforço criativo nos métodos de aplicação dos sinais, a fim de atender aos requisitos de simplicidade, baixo consumo de energia, baixa sensibilidade, conciliados às restrições da tecnologia CMOS.

## 1.4. Organização do Texto

Esta tese está organizada em 7 (sete) capítulos com a seguinte distribuição de tópicos:

- ➤ No Capítulo 2, são apresentados os fundamentos teóricos sobre multiplicadores analógicos, espelhos de corrente, subtratores e redes neuronais celulares (CNN);

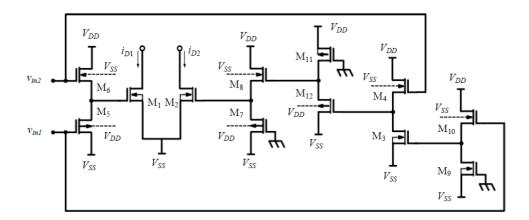

- ➤ No Capítulo 3, descreve-se e analisa-se o desempenho de uma nova arquitetura de multiplicador analógico em tecnologia CMOS muito compacto para aplicação em sinapses de CNN. Este circuito gerou uma publicação apresentada no LASCAS 2019 Latin American Symposium on Circuits and Systems, em 2019, na Armenia, Colômbia, com o título "A Very Compact CMOS Analog Multiplier for Application in CNN Synapses";

➤ No Capítulo 4, descreve-se e analisa-se o desempenho de uma nova arquitetura de multiplicador analógico CMOS de quatro quadrantes que dispensa geradores de tensão de referência, para aplicação também em sinapses de CNN. Este circuito gerou uma publicação apresentada no SBCCI 2019 - 32nd SBCCI – Symposium on Circuits and Systems Design, em 2019, São Paulo-SP, Brasil, com o título "CMOS Analog Four-Quadrant Multiplier Free of Voltage Reference Generators";

- ➤ No Capitulo 5 descreve-se uma versão melhorada do multiplicador apresentado no Capítulo 4;

- ➤ No Capítulo 6, efetua-se uma análise comparativa entre os multiplicadores analógicos CMOS propostos neste trabalho e em (SANTANA, 2013) e (CARDOSO; SCHNEIDER; SANTANA, 2018);

- Finalizando, no Capitulo 7 expõem-se as conclusões desta tese.

## 2. FUNDAMENTAÇÃO TEÓRICA

Neste capítulo expõe-se uma revisão dos principais conceitos envolvidos neste estudo: os fundamentos e as características dos multiplicadores analógicos, espelhos de corrente e subtratores de corrente em tecnologia CMOS, assim como uma breve explanação sobre a operação de redes neuronais celulares analógicas (CNN), particularmente com células do tipo FSR (*full signal range*).

## 2.1. Multiplicadores

A multiplicação analógica em tempo real de dois sinais é uma das operações mais importantes no processamento de sinais analógicos. O multiplicador é utilizado não apenas como um bloco de construção computacional, mas também como um elemento de programação em sistemas como filtros, redes neuronais (CNN), misturadores e moduladores em sistemas de comunicação (HAN; SÁNCHEZ-SINENCIO, 1998). Multiplicadores analógicos a MOSFET possibilitam compatibilizar as tecnologias de fabricação da porção analógica e da porção digital dos circuitos analógicos ditos mistos e também demandam menores tensões de alimentação que congêneres a transistores bipolares de junção (TBJ) (HAN; SÁNCHEZ-SINENCIO, 1998).

## 2.1.1. Princípio de Operação dos Multiplicadores

Os multiplicadores ideais executam produtos lineares de dois sinais (*x* e *y*), que podem variar no tempo, resultando em um sinal *cxy*, sendo *c* uma constante (HAN; SÁNCHEZ-SINENCIO, 1998), (MACHADO, 2007).

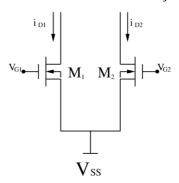

Multiplicadores podem ser classificados como de quadrante único (no qual os dois sinais de entrada devem ser unipolares), de dois quadrantes (onde um sinal de entrada pode ser bipolar e o outro deve ser unipolar) e de quatro quadrantes (onde ambos sinais de entrada podem ser bipolares). A Figura 1 ilustra a disposição dos sinais de entrada do multiplicador por quadrantes.

Segundo Han e Sánchez-Sinencio (1998), apesar do grande número de artigos propondo novas estruturas de multiplicadores MOS, os princípios básicos que regem a operação de multiplicadores analógicos são dois: por dispositivo não linear e por transcondutância programável. Embora duas décadas tenham se passado, uma revisão bibliográfica mostrou que esta afirmação continua verdadeira.

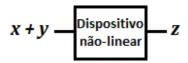

#### 2.1.2. Multiplicação por Dispositivo Não-Linear

Uma forma de implementação de circuitos multiplicadores, exposta na Figura 2, ocorre através da exploração das características não lineares dos dispositivos. A soma de dois sinais, x e y, aplicada à entrada de um dispositivo não linear, caracterizado por uma função polinomial de alta ordem, gera na saída um sinal z na forma:

$$z = a_0 + a_1(x+y) + a_2(x+y)^2 + a_3(x+y)^3 + \cdots$$

(1)

O termo desejado, proporcional ao produto xy, está embutido no termo de  $2^a$  ordem:

$$a_2(x+y)^2 = a_2x^2 + 2a_2xy + a_2y^2$$

(2)

Contudo, muitos outros termos são gerados e, assim, é necessário que em sua saída seja acoplado um esquema de cancelamento destes elementos indesejáveis.

Figura 2 – Multiplicador por Dispositivo Não Linear.

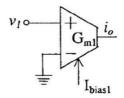

# **2.1.3.** Multiplicação por Dispositivo de Transcondutância Programável

Um multiplicador pode ser formado utilizando-se componentes de transcondutância programável. Considere-se o amplificador de transcondutância programável conceitual, ilustrado na Figura 3, em que a corrente de saída pode ser representada por  $i_o = G_{m1}v_1$ , sendo a transcondutância  $G_{m1}$  igual a  $\frac{I_{Bias1}}{V_K}$ , onde  $I_{BIAS1}$  é a corrente de polarização e  $V_K$  é um parâmetro constante com unidade de tensão.

Figura 3 – Amplificador de Transcondutância.

Fonte: (HAN; SÁNCHEZ-SINENCIO, 1998)

Adicionando-se um pequeno sinal  $i_2$  à corrente de polarização, como ilustrado na Figura 4(a), a corrente de saída fica:

$$i_o = G_{m1} v_1 = \frac{(I_{Bias1} + i_2)}{V_K} v_1 \tag{3}$$

Se esta corrente é oriunda de outro transcondutor, com tensão de entrada  $v_2$ , transcondutância  $G_{m2}$  igual a  $\frac{I_{Bias2}}{V_K}$  e polarizado com corrente  $I_{BIAS2}$ , como ilustrado na Figura 4(b), então:

$$i_o = G_{m1}v_1 = \frac{I_{Bias1} + G_{m2}v_2}{V_K}v_1 = \frac{I_{Bias1}}{V_K}v_1 + \frac{I_{Bias2}}{V_K}v_1v_2$$

(4)

Figura 4 – Multiplicador Baseado em Amplificador de Transcondutância: (a) Adição de pequeno sinal  $i_2$  à corrente de polarização; (b) Utilização de segundo transcondutor para geração de  $i_2$ ; (c) Célula de Gilbert utilizando três transcondutores.

Fonte: (HAN; SÁNCHEZ-SINENCIO, 1998)

Assim, a corrente de saída  $i_0$  é constituída por um termo proporcional ao produto dos dois sinais  $v_1$  e  $v_2$ , somado a um componente  $k_2v_1$  indesejado. Este componente pode ser eliminado através de um esquema de cancelamento, no qual um terceiro transcondutor é utilizado e as entradas em tensão são aplicadas no modo diferencial, como ilustrado na Figura 4(c). Este é o princípio básico de operação de uma célula de Gilbert, cujas implementações baseadas no Amplificador de Transcondutância Operacional (OTA) são relatadas por Han e Sánchez-Sinencio, (1998).

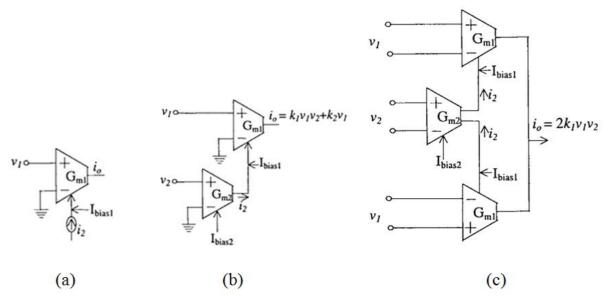

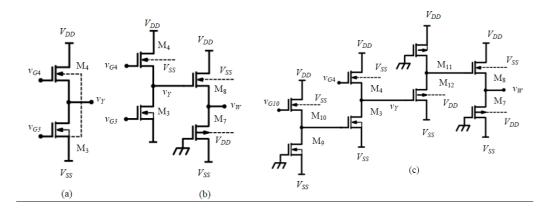

#### 2.1.4. Esquemas de Cancelamento

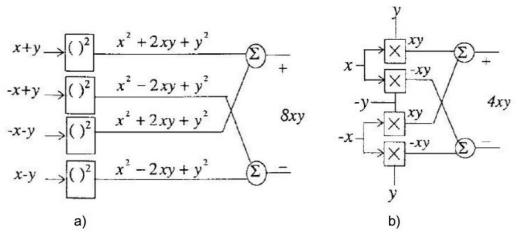

Os esquemas de cancelamento citados anteriormente são usualmente construídos por combinações de dispositivos ou *células quadradoras*, como ilustrado na Figura 5(a), ou de *células multiplicadoras* de um quadrante, como ilustrado na Figura 5(b).

Figura 5 – Esquemas de Cancelamento por Combinação de: (a) Quadradores; (b) Multiplicadores de 1 quadrante.

Fonte: (HAN; SÁNCHEZ-SINENCIO, 1998)

Nestes esquemas tanto os termos indesejados como as componentes de polarização são eliminados. No caso de cancelamento por combinação de células quadradoras, o princípio de operação se baseia na expressão:

$$\{[(X+x)+(Y+y)]^2 + [(X-x)+(Y-y)]^2\} - \{[(X-x)+(Y+y)]^2 + [(X+x)+(Y-y)]^2\} = 8xy$$

(5)

em que x e y são os sinais e X e Y sãos suas respectivas componentes de polarização.

No caso de cancelamento por combinação de multiplicadores de um quadrante, o princípio de operação se baseia na expressão:

$$[(X + x) (Y + y) + (X - x) (Y - y)] - [(X - x) (Y + y) + (X + x) (Y - y)] = 4xy$$

(6)

Em multiplicadores que operam com saída em modo corrente, a adição entre dois ou mais sinais, ocorrente várias vezes em (5) e (6), pode ser realizada em um nó. Por outro lado, a subtração também presente nestas expressões é implementada por subtratores de corrente, em geral constituídos por espelhos de correntes, tópico que será abordado na Seção 2.2.

#### 2.1.5. Tipos de Multiplicadores

De acordo com Han e Sánchez-Sinencio (1998), os multiplicadores em tecnologia CMOS podem ser agrupados em oito tipos, que podem ser categorizados em dois grupos com base na região de operação dos transistores MOS, supostamente no regime de inversão forte: linear (HAN; SÁNCHEZ-SINENCIO, 1998), (COLLI-MONTECCH, 1996) e de saturação (WANG, 1993), (QIN; GEIGER, 1987). Os oito tipos, por sua vez, restritos a multiplicadores com entradas em tensão, diferem pelo método de injeção dos sinais e são relacionados na Tabela 1, extraída de (HAN; SÁNCHEZ-SINENCIO, 1998). Nesta tabela, a terceira coluna (Termo Ativo) indica o termo da relação quadrática entre a corrente de dreno e as tensões terminais que é efetivamente utilizado para gerar o produto entre os sinais de entrada. A quarta coluna (Método de Cancelamento) refere-se a qual dos dois métodos indicados na Figura 5 é utilizado para eliminar os termos indesejados e os níveis de polarização. A sexta coluna (Comentários) exibe conclusões dos autores do trabalho a respeito da viabilidade de implementação. Deve-se enfatizar que os princípios fundamentais são os mesmos para muitos dos multiplicadores apresentados em publicações científicas e, apesar da antiguidade do tutorial de Han e Sánchez-Sinencio, esta classificação ainda continua atual. Além das estruturas multiplicadoras básicas da Tabela 1, multiplicadores operando na região de inversão fraca (SONG-KIM, 1990), multiplicadores dinâmicos para sistemas que operam com sinais amostrados ou multiplicadores voltados para aplicações em redes neuronais, com entradas no modo tensão-corrente ou correntecorrente foram reportados (HAN; SÁNCHEZ-SINENCIO, 1998), (JOORDENS; HEGT; LEENAERTS, 1995).

$Tabela\ 1-Resumo\ de\ Modos\ Operacionais\ dos\ Multiplicadores.$

Fonte: (HAN; SÁNCHEZ-SINENCIO, 1998)

| Região<br>de<br>Operação | Metodo de Injeção de<br>Sinal                                                        | Termo<br>Ativo | Método de<br>Cancelamento     | Tipo | Comentários   |

|--------------------------|--------------------------------------------------------------------------------------|----------------|-------------------------------|------|---------------|

|                          |                                                                                      | $V_{gs}V_{ds}$ | 1 Quadrante                   | I    |               |

| Linear                   | $ \begin{array}{c} \pm x \pm y \\ \downarrow i_d \end{array} $                       | $V_{ds}^{2}$   | Quadrador                     | II   | não é prática |

|                          |                                                                                      | $V_{gs}V_{ds}$ | 1 Quadrante                   | III  | não é prática |

|                          |                                                                                      | ${V_{gs}}^2$   | Quadrador                     | IV   | não é prática |

|                          |                                                                                      | ${V_{gs}}^2$   | Quadrador                     | V    |               |

| Saturação                | $\pm x -   \frac{   i_d}{  } \pm y$                                                  | ${V_{gb}}^2$   | Quadrador                     | VI   | não é prática |

|                          | $\pm x \pm y - \begin{vmatrix}    \mathbf{i}_d \\    \mathbf{j} \end{vmatrix}$       | ${V_{gs}}^2$   | Quadrador                     | VII  |               |

|                          | $\pm x \rightarrow \begin{bmatrix} \downarrow i_d \\ \downarrow \pm y \end{bmatrix}$ | ${V_{gs}}^2$   | Célula Gilbert<br>1 Quadrante | VIII |               |

Como as arquiteturas de multiplicadores analógicos em tecnologia CMOS propostas no presente trabalho possuem entradas em modo tensão, é apresentada a seguir uma relação de trabalhos publicados nesta mesma linha nas últimas duas décadas, ressaltando as principais características dos circuitos.

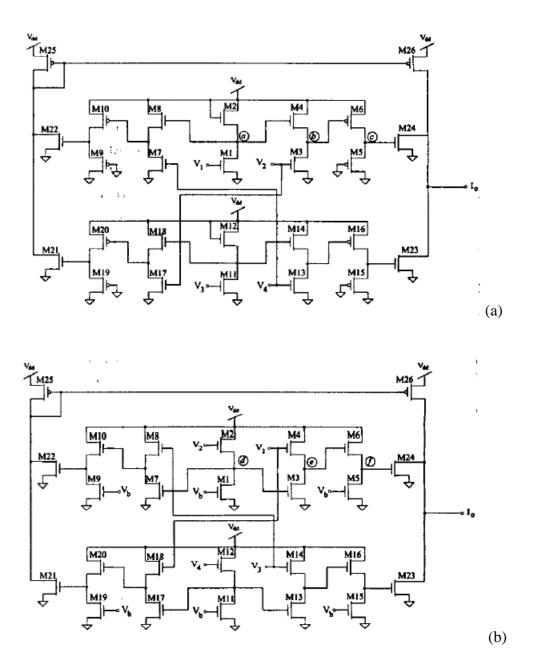

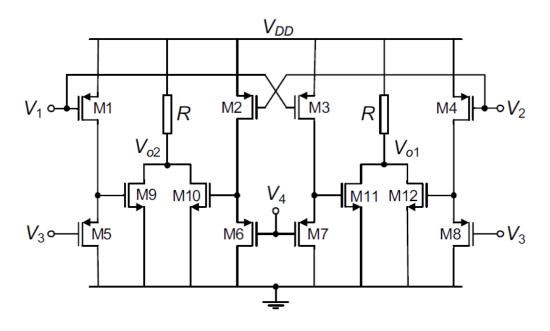

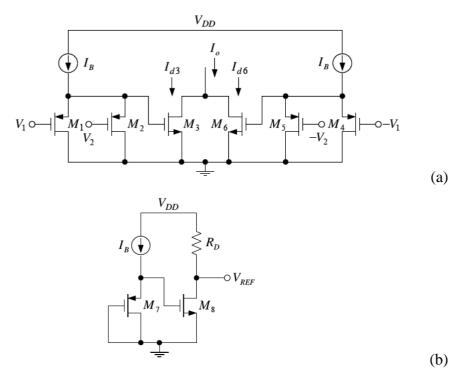

(i) Em (MAUNDY; ARONHIME, 2002) são apresentadas duas arquiteturas de multiplicadores de quatro quadrantes do tipo VII da Tabela 1, ou seja, baseadas na relação quadrática entre a corrente de dreno e a tensão portafonte em transistores MOS operando em inversão forte e saturação. Numa arquitetura, ilustrada na Figura 6(a), é utilizado um esquema de cancelamento igual ao de (5) e na outra, ilustrada na Figura 6b), um esquema semelhante, no qual as tensões de entrada são subtraídas antes de serem elevadas ao quadrado. Na primeira, são utilizados transistores canal P e transistores canal N e na segunda, apenas transistores canal N, mas é requerido um gerador de tensão de referência, que não é apresentado. Cada um dos dois sinais a serem multiplicados é aplicado a duas entradas, numa das quais invertido, não sendo, contudo, apresentado o circuito auxiliar que realiza esta inversão. Todos os sinais são aplicados acompanhados de uma tensão de polarização. É utilizado o princípio de que o potencial entre dois transistores do mesmo tipo em série contém um termo proporcional à diferença entre os potenciais de porta. O sinal de saída é a corrente resultante de um subtrator de corrente formado por um espelho Widlar. Os circuitos são implementados para simulação em uma tecnologia CMOS canal N de 0,35 µm, utilizando transistores de grandes dimensões (largura de 200 µm para todos os dispositivos e comprimentos de 4 µm, para os dispositivos canal N e de 2 µm, para os dispositivos canal P). Adotou-se tensão de alimentação de 3,3 volts. Foram reportados como resultados de simulação: distorção harmônica total de 0,4 % e de 0,2 % para o primeiro e segundo circuitos, respectivamente, com sinais de amplitude igual a 150 mV e frequência de até 100 kHz; largura de banda de aproximadamente 84 MHz e 30 MHz para o primeiro e o segundo circuitos, respectivamente. Nenhuma informação sobre a potência, área ativa e sensibilidade foi apresentada. Os autores clamam que o circuito é adequado para aplicações de baixa tensão

porque todos os ramos entre os terminais de alimentação (*rails*) incluem apenas dois transistores em série.

Figura 6 – Multiplicadores para aplicação em baixa tensão: (a) baseado em somadores de baixa tensão; (b) baseados em subtratores de baixa.

Fonte: (MAUNDY; ARONHIME, 2002)

(ii)

Em (HASAN, 2005), é apresentado um multiplicador de quatro quadrantes também do tipo VII da Tabela 1, ilustrado na Figura 7. Em cada uma de quatro seções multiplicadoras de um quadrante as correntes de dreno de dois transistores, que recebem sinais em seus terminais de porta, são somadas e aplicadas a um dispositivo operando no início da região triodo para atuar como resistência quase linear, convertendo a soma das correntes em tensão. As duas tensões assim resultantes na saída de dois blocos de um quadrante são aplicadas aos terminais de porta de outros dois transistores, cujas correntes de dreno também são somadas e transferidas por meio de um espelho Widlar a outro dispositivo no início da região triodo, gerando o potencial de saída de um dos dois blocos multiplicadores de dois quadrantes. Desta forma, obtêm-se os dois potenciais que constituem a tensão diferencial de saída do multiplicador de quatro quadrantes. Como no exemplo (i), os sinais a serem multiplicados são acrescidos de tensões de modo comum e são apresentados também na versão invertida, mas os circuitos que fazem estas operações não são apresentados. As mais importantes características ressaltadas pelo autor são: a larga excursão dos sinais, a extensa largura de banda e a escalabilidade do circuito (conversão entre diferentes tecnologias de fabricação). Para ilustrar esta última propriedade, resultados de simulação são apresentados para implementação em duas tecnologias CMOS: 0,5 μm, com alimentação de 3,3 V, e 0,18 µm, com alimentação de 1,0 V. Uma das implementações (não é especificada qual) utiliza transistores comprimento igual a 2 µm (exceto por dois com comprimentos de 3,9 µm) e larguras variando entre 2 µm e 100 µm, a maior parte das quais na faixa de 20 μm. É relatado sucesso na modulação de sinais por portadoras de 50 MHz nas duas tecnologias, com distorção harmônica total de -56 dB e de -54 dB para as tecnologias de 0,5 µm e 0,18 µm, respectivamente. A excursão máxima dos sinais é de 500 mV pico-a-pico. A mencionada largura de banda com corte em 3 dB de 1 GHz é desmentida pelo diagrama de Bode de magnitude da função de transferência apresentado. Neste diagrama a variação da magnitude do ganho em relação ao valor de baixas frequências é maior que 100 dB. É reportada uma potência de 1 mW para o caso da tecnologia de  $0.18~\mu m$ .

Figura 7 – Multiplicador analógico CMOS escalável, de larga excursão.

Fonte: (HASAN, 2005)

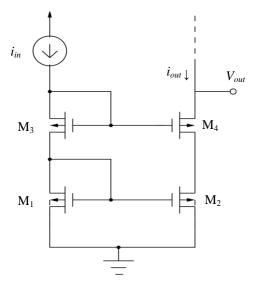

(iii) Em (HUANG et al., 2006), é apresentado um multiplicador de quatro quadrantes do tipo III da Tabela 1, ilustrado na Figura 8. Uma célula multiplicadora básica é constituída de quatro ramos, cada um com um seguidor de fonte em série com um MOSFET na região triodo, o primeiro transferindo o sinal aplicado ao seu terminal de porta para o dreno do segundo, que é conectado por uma resistência ao terminal correspondente em outro ramo. Cada sinal a ser multiplicado é aplicado a quatro terminais de porta, sendo que em dois deles na forma invertida, não sendo apresentado o circuito que efetua esta inversão. As correntes de saída dos ramos desta célula são somadas e subtraídas por meio de um espelho *cascode*. Uma outra

célula idêntica é utilizada como um recurso para melhorar a linearidade do circuito, denominado realimentação ativa (active feedback): suas correntes de ramo são também somadas e subtraídas às da primeira célula, mas suas tensões de entrada consistem de um potencial constante (e seu simétrico) nos terminais de porta dos transistores que operam na região triodo e do potencial no nó de saída do multiplicador global (e seu simétrico) nos terminais de porta dos seguidores de fonte. O potencial na saída do multiplicador e seu simétrico são obtidos de uma rede com dois amplificadores operacionais e resistores, em cuja entrada é aplicado o potencial no nó de saída do subtrator. São apresentados resultados de simulação referentes à implementação em uma tecnologia CMOS de 0,6 µm, com alimentação simétrica de  $\pm 2,5$  V. Não são informadas as dimensões dos transistores tampouco dos resistores do circuito, se considerados partes do circuito integrado. Também não são fornecidos detalhes da implementação dos amplificadores operacionais. A distorção harmônica total para amplitudes de 0,1 a 1,5 V no sinal aplicado às entradas dos seguidores de fonte, com as outras entradas fixadas em 0,5 V, varia entre aproximadamente -64 a -39 dB. A banda não é informada, mas foram efetuados testes com sinais de 1 MHz. A propriedade mais importante desta arquitetura, realçada pelos autores, é a larga faixa dinâmica, a amplitude dos sinais nas entradas dos seguidores de tensão podendo variar numa faixa de 72 % da tensão de alimentação e a amplitude das outras entradas, numa faixa de 48 %.

Figura 8 – Multiplicador analógico de quatro quadrantes.

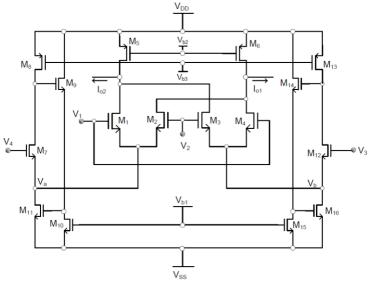

Fonte: (HUANG et al., 2006)

(iv) Em (SAWIGUN et al., 2007), é proposta uma arquitetura de multiplicador analógico de quatro quadrantes muito simples, que se enquadra no tipo VII da Tabela 1. Este multiplicador é ilustrado na Figura 9. As entradas são tensões diferenciais que são aplicadas aos terminais de porta de pares de transistores canal P em série que realizam a diferença dos potenciais de porta no nó de conexão entre eles. Estas diferenças são então aplicadas nos terminais de porta de quatro transistores canal N operando em inversão forte e em saturação, de modo que suas correntes de dreno apresentam uma relação quadrática com a tensão porta-fonte. As correntes são somadas em nós e convertidas em tensão por meio de dois resistores. A diferença entre as tensões dos resistores é a tensão de saída, proporcional ao produto das entradas diferenciais. Segundo os autores, o circuito proporciona elevada linearidade e opera com baixa potência e baixa tensão de alimentação. Para corroborar suas afirmações, são realizadas simulações implementação em tecnologia CMOS de 0,35 µm, com tensão de alimentação de 1,2 V. Adotou-se comprimento de 0,5 µm para todos os doze transistores do circuito, largura de 3 µm para os oito transistores canal P e largura de 0,5 µm para os quatro transistores canal N. Os resistores são de 5,7 k $\Omega$ , não tendo sido explicitado se a sua implementação é integrada. Foram registradas: largura de banda com corte em 3 dB de 110 MHz,

excursão satisfatória dos sinais diferenciais na entrada de  $\pm 0,25$  V, distorção harmônica total abaixo de -45 dB para amplitudes de até 275 mV, potência estática de 34  $\mu$ W. Tensões de modo comum são requeridas, não sendo apresentados os circuitos geradores das mesmas.

Figura 9 – Multiplicador analógico de quatro quadrantes.

Fonte: (SAWIGUN et al., 2007)

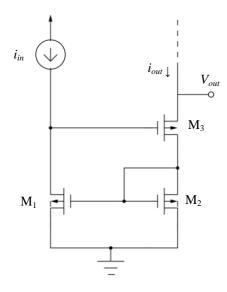

(v) Em (MAHMOUD, 2009) é apresentado um multiplicador de quatro quadrantes também bastante simples, ilustrado na Figura 10, que se enquadra no tipo V da Tabela 1, no qual se aproveita a relação quadrática entre a corrente de dreno e a diferença entre os potenciais de porta e fonte de um MOSFET em inversão forte e saturação. A arquitetura inclui dois pares de transistores com terminais de fonte conectados dois a dois. Uma das tensões diferenciais de entrada é aplicada aos terminais de porta. A outra é transferida aos terminais de fonte por meio de transistores na configuração de seguidor de fonte, polarizados com corrente constante. As correntes de dreno dos transistores que recebem os sinais são somadas duas a duas e também com correntes de polarização. A saída em modo corrente, consiste na diferença entre as duas somas de corrente, mas o circuito subtrator não é apresentado. Tampouco são apresentados os circuitos geradores das tensões

de referência necessárias para a fixação das correntes de polarização do circuito. São apresentados resultados de simulação para uma implementação em tecnologia CMOS de 0,25  $\mu$ m, adotando-se alimentação simétrica de  $\pm 1$  V. São reportadas como vantagens do circuito: larga excursão dos sinais diferenciais de entrada ( $\pm 0,75$  V) e operação em baixa tensão, com baixa potência (0,326 mW). Registrou-se uma distorção harmônica total inferior a 1 % para amplitudes de 0,5 V do sinal diferencial de entrada e largura de banda com corte em 3 dB de 16 MHz.

Figura 10 – Multiplicador analógico CMOS de quatro quadrantes.

Fonte: (MAHMOUD, 2009)

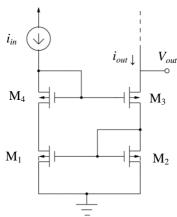

(vi) Em (POPA, 2014) é proposta uma arquitetura de multiplicador de quatro quadrantes do tipo VII da Tabela 1, ilustrada na Figura 11. As tensões de entrada são diferenciais, sendo aplicadas aos terminais de porta de pares de transistores casados. Uma das tensões diferenciais é aplicada a um par de transistores canal P com terminais de fonte conectados ao substrato. A outra tensão diferencial é aplicada a dois blocos simétricos, cada um dos quais compostos de um trio de transistores canal N conectados pelos terminais de fonte. Um dos transistores do trio de cada bloco está em série com um dos transistores canal P e sua corrente é então espelhada por um outro transistor do trio que compartilha seu terminal de porta, para ser somada à corrente do terceiro transistor canal N do trio, porém do bloco oposto. Os resultados das duas somas de correntes são aplicados a um espelho Widlar que realiza a

subtração e, subsequente cancelamento de termos estranhos à multiplicação. Apesar da simplicidade da estrutura, não são apresentados resultados de simulação, tampouco experimentais, para ilustrar a funcionalidade e o desempenho do circuito e corroborar a elevada linearidade sugerida pelo autor.

Figura 11 – Multiplicador analógico CMOS de quatro quadrantes.

Fonte: (POPA, 2014)

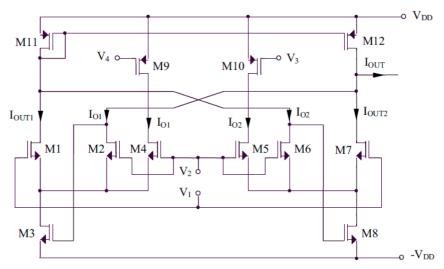

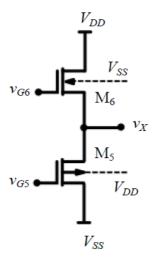

Em (BOONCHU, 2018), é apresentado um multiplicador de quatro (vii) quadrantes com entradas em modo tensão, baseado no comportamento exponencial da relação corrente-tensão do MOSFET em inversão fraca. Desta forma, não se enquadra em nenhum dos tipos da Tabela 1, que se restringem ao comportamento em inversão forte. O circuito, ilustrado na Figura 12(a), combina dois somadores de tensão no regime de sublimiar, aos quais são aplicados os sinais de tensão a serem multiplicados e seus simétricos. Não é apresentado o circuito responsável pela inversão dos sinais de entrada nem as arquiteturas de três fontes de corrente de polarização utilizadas em todo o circuito, duas no núcleo multiplicador e uma no bloco gerador de uma tensão de referência. As correntes de saída destes somadores são somadas e convertidas em tensão através de um resistor. Outro resistor é utilizado no bloco gerador da tensão de referência, ilustrado na Figura 12(b). Para que o sinal de tensão na saída do multiplicador represente o produto entre os sinais de tensão, a magnitude da soma dos sinais de entrada deve ser inferior a algumas dezenas de milivolts. A proposta dos autores é que o multiplicador atenda satisfatoriamente a requisitos de baixa tensão e baixa potência, sendo seu desempenho analisado por meio de simulações de uma implementação na tecnologia 0,18  $\mu$ m, sendo adotada tensão de alimentação de 0,8 V. Não ficou claro se, nestas simulações, as três fontes de corrente de 200 nA são ideais ou se foram implementadas em tecnologia CMOS. Também não foi explicitado se os dois resistores de 470 k $\Omega$  fazem parte do circuito integrado. O comprimento de canal adotado para os transistores, canal N ou P, é de 0,5  $\mu$ m e as larguras variam de 0,5 a 4  $\mu$ m. Foi registrada uma potência muito baixa, de apenas 0,78  $\mu$ W. As excursões dos sinais admitidas na entrada e na saída são, respectivamente,  $\pm$ 25 mV e  $\pm$ 40 mV. A distorção harmônica total é de 1,3 % para a amplitude de 25 mV na entrada e a largura de banda com corte em 3 dB é de 650 kHz.

Figura 12 – Multiplicador analógico de quatro quadrantes no regime de sub-limiar: (a) núcleo; (b) gerador da tensão de referência.

Fonte: (BOONCHU, 2018)

### 2.2. Espelhos de Corrente em Tecnologia CMOS

Os espelhos de corrente são elementos fundamentais dos circuitos integrados ou sistemas VLSI<sup>5</sup> analógicos. Uma aplicação comum de espelho de corrente é a geração de corrente CC estáveis e previsíveis para polarizar outros circuitos. Quando utilizado com essa finalidade, um espelho de corrente também é conhecido como uma referência de corrente. Espelhos também são utilizados para injetar ou drenar sinais de corrente. Como tal, eles encontram aplicação como cargas ativas em uma variedade de CI's de processamento de sinais analógicos, como amplificadores operacionais (AMP OP), amplificadores de realimentação de corrente (CFA) e amplificadores operacionais de transcondutância (OTA). O espelhamento de corrente é possibilitado pelo elevado grau de casamento entre transistores fabricados em estreita proximidade uns dos outros no mesmo chip. A função de um espelho de corrente é receber uma corrente iin em um terminal de baixa resistência de entrada, de preferência zero, e entregar uma corrente i<sub>out</sub> a partir de um terminal de alta resistência de saída, de preferência infinita. O espelho de corrente é similar ao seguidor de corrente, buffer<sup>6</sup>, exceto pelo fato de que ambas as correntes fluem para dentro, ou para fora, do circuito. Por essa razão diz-se também que o espelho de corrente proporciona inversão de corrente. (FRANCO, 2016)

Para circuitos analógicos com aplicações de alto desempenho, a precisão e a largura de banda são os parâmetros mais importantes para determinar o desempenho do espelho de corrente.

Neste trabalho, o interesse pelo estudo de espelhos reside no fato de serem os elementos constituintes dos subtratores de corrente, que por sua vez são elementos imprescindíveis nos esquemas de cancelamento de multiplicadores com saída em corrente.

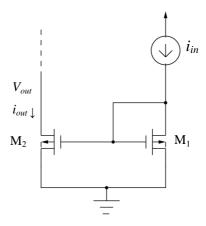

O espelho de corrente simples ou Widlar é ilustrado na Figura 13, na qual  $M_1$  é o transistor de entrada e  $M_2$ , o de saída. Graças ao fato de que as correntes de portas são nulas, um espelho de corrente a MOSFET não apresenta o erro sistemático que um TBJ apresenta devido à corrente de base.

\_

<sup>&</sup>lt;sup>5</sup> Very large-scale integration.

<sup>&</sup>lt;sup>6</sup> Amplificador de ganho unitário usado para isolar e conectar um estágio de alta impedância de entrada a uma carga de baixa impedância de saída.

Figura 13 – Espelho de Corrente Widlar.

No espelho Widlar,  $M_1$  opera em saturação (conexão diodo) e  $M_2$  deve operar em saturação, atendendo à condição:

$$V_{DS2} = V_{out} - V_{SS} > V_{DSSAT2} \tag{7}$$

em que  $V_{DS2}$  é a tensão dreno-fonte de  $M_2$ ,  $V_{out}$  é o potencial no terminal de saída (dreno de  $M_2$ ),  $V_{SS}$  é o potencial de substrato dos transistores canal N (o mais baixo potencial do circuito, que no caso da Figura 13 coincide com o terra) e  $V_{DSST2}$  é a tensão dreno-fonte no limiar de saturação.

Quando a corrente de entrada  $i_{in}$  é aplicada, o transistor  $M_1$  responde com uma tensão porta-fonte tal que se relaciona com  $i_{in}$  de acordo com a expressão:

$$i_{in} = \frac{k_1}{2} (V_{GS} - V_{th})^2 (1 + \lambda V_{GS})$$

(8)

em que  $V_{th}$  é a tensão de limiar,  $k_1$  é o parâmetro de transcondutância de  $M_1$  e  $\lambda$  modela o efeito Early, que reúne efeitos de canal curto diversos.

Mas o transistor  $M_2$  está submetido à mesma tensão  $V_{GS}$  que  $M_1$ , então  $M_2$  vai drenar a corrente,

$$i_{out} = \frac{k_2}{2} (V_{GS} - V_{th})^2 (1 + \lambda V_{out})$$

(9)

Como sabemos, o parâmetro de transcondutância de um MOSFET é k = k'(W/L), em que W e L são, respectivamente, a largura e o comprimento do canal do FET particular, e k' é o parâmetro de transcondutância do processo, comum a todos

FET's do mesmo tipo no chip. Tomando a razão  $i_{in}/i_{out}$  e simplificando, obtemos, sob a consideração  $\lambda V_{GS} \ll 1$ ,