# Universidade Federal da Bahia Programa de Pós-Graduação em Engenharia Elétrica – PPGEE

Análise e construção de aceleradores em hardware para o cálculo do menor caminho em planejamento de rotas de robôs

### **Linton Thiago Costa Esteves**

Tese de Doutorado do Programa de Pós-Graduação em Engenharia Elétrica (PPGEE)

#### **Linton Thiago Costa Esteves**

Análise e construção de aceleradores em hardware para o cálculo do menor caminho em planejamento de rotas de robôs

Tese apresentada ao Programa de Pós-Graduação em Engenharia Elétrica – PPGEE, como parte dos requisitos para obtenção do título de Doutor em Engenharia Elétrica. *VERSÃO REVISADA*

Área de Concentração: Processamento da Informação e Energia

Orientadores: Prof. Dr. Wagner Luiz Alves de Oliveira / Prof. Dr. Paulo César Machado de Abreu Farias

Universidade Federal da Bahia – Salvador Outubro de 2024

# ANÁLISE E CONSTRUÇÃO DE ACELERADORES EM HARDWARE PARA O CÁLCULO DO MENOR CAMINHO EM PLANEJAMENTO DE ROTAS DE ROBÔS

#### Linton Thiago Costa Esteves

TESE SUBMETIDA AO PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA (PPGEE) DA UNIVERSIDADE FEDERAL DA BAHIA COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE DOUTOR EM ENGENHARIA ELÉTRICA.

Aprovada por:

WAGNER LUIZ ALVES DE OLIVEIRA

Data: 27/11/2024 12:37:28-0300

Verifique em https://validar.iti.gov.br

Prof. Wagner Luiz Alves de Oliveira, D.Sc. (Orientador)

Documento assinado digitalmente

PAULO CESAR MACHADO DE ABREU FARIAS

Data: 27/11/2024 11:45:27-0300

Verifique em https://validar.iti.gov.br

Prof. Paulo César Machado de Abreu Farias, D.Sc. (Orientador)

Ocumento assinado digitalmente

ANFRANSERAI MORAIS DIAS

Data: 02/12/2024 15:27:29-0300

Verifique em https://validar.iti.gov.br

Prof. Anfranserai Morais Dias, D.Sc. - UEFS

Documento assinado digitalmente

EDWARD DAVID MORENO ORDONEZ

Data: 29/11/2024 16:36:53-0300

Verifique em https://validar.iti.gov.br

Prof. Edward David Moreno Ordonez, D.Sc. - UFS

Documento assinado digitalmente

NELSON ALVES FERREIRA NETO

Data: 27/11/2024 08:40:01-0300

Verifique em https://validar.iti.gov.br

Prof. Nelson Alves Ferreira Neto, D.Sc. - SENAI

Documento assinado digitalmente

TIAGO TRINDADE RIBEIRO

Data: 03/12/2024 07:32:54-0300

Verifique em https://validar.iti.gov.br

Prof. Tiago Trindade Ribeiro, D.Sc. - UFBA

SALVADOR, BA – BRASIL OUTUBRO DE 2024

### Ficha catalográfica elaborada pelo Sistema Universitário de Bibliotecas (SIBI/UFBA), com os dados fornecidos pelo(a) autor(a).

Thiago Costa Esteves, Linton

Análise e construção de aceleradores em hardware para o cálculo do menor caminho em planejamento de rotas de robôs / Linton Thiago Costa Esteves. -- Salvador, 2024.

110 f.

Orientador: Wagner Luiz Alves de Oliveira. Coorientador: Paulo César Machado de Abreu Farias.

Tese (Doutorado - Engenharia Elétrica) -- Universidade Federal da Bahia, UFBA, 2024.

1. Dijkstra. 2. Menor Caminho. 3. PRM. 4. FPGA. 5. Robótica. I. Luiz Alves de Oliveira, Wagner. II. César Machado de Abreu Farias, Paulo . III. Título.

#### **Linton Thiago Costa Esteves**

Analysis and construction of hardware accelerators for shortest path calculation in robot route planning

Doctoral dissertation submitted to the Post-Graduation Program in Electrical Engineering – PPGEE, in partial fulfillment of the requirements for the degree of the Doctorate Program in Electrical Engineering. *FINAL VERSION*

Concentration Area: Information Processing and Energy

Advisors: Prof. Dr. Wagner Luiz Alves de Oliveira / Prof. Dr. Paulo César Machado de Abreu Farias

Federal University of Bahia – Salvador October 2024

#### Meu amado filho,

Esta tese é dedicada a você, que me ensinou o poder do amor incondicional.

Que este trabalho, fruto de tanta dedicação, desafios e sacrifícios sirva como um exemplo de que, com esforço e determinação, qualquer objetivo pode ser alcançado. Cada momento de empenho foi motivado pelo desejo de construir um futuro melhor para você. Sua presença e amor foram minha maior fonte de força e inspiração.

Que você sempre se lembre de seguir seus sonhos com determinação, sabendo que, mesmo nos momentos mais difíceis, o amor e o esforço valem a pena.

Que esta tese seja um testemunho do quanto é possível alcançar com perseverança e paixão.

Com todo o meu amor,

Seu Pai.

### **AGRADECIMENTOS**

Gostaria de agradecer profundamente à minha esposa Samara Ribeiro, por seu amor, paciência e apoio incondicional. Sua compreensão e encorajamento foram fundamentais para que eu pudesse me dedicar a esta pesquisa. Sua presença e suporte emocional foram essenciais nos momentos mais desafiadores.

Também gostaria de expressar minha profunda gratidão ao meu orientador, Prof. Dr. Wagner Luiz Alves de Oliveira, por sua orientação, paciência e suporte ao longo de todo este projeto. Suas valiosas sugestões e incentivo constante foram fundamentais para a conclusão desta tese.

Agradeço também ao meu orientador, Prof. Dr. Paulo César Machado de Abreu Farias, por suas contribuições essenciais, conselhos valiosos e disponibilidade para discutir ideias e solucionar dúvidas. Seu conhecimento e apoio foram inestimáveis para o desenvolvimento desta pesquisa.

Gostaria ainda de agradecer à minha irmã Camila, por sua ajuda nas revisões de última hora. Sua dedicação e apoio foram essenciais.

Um agradecimento especial ao Instituto Federal Baiano, que me proporcionou o suporte necessário para a realização desta tese. O apoio recebido foi crucial para o sucesso deste trabalho.

"De tudo ficaram três coisas:

A certeza de que estamos começando,

A certeza de que é preciso continuar,

A certeza de que podemos ser interrompidos antes de terminar.

Façamos da interrupção um caminho novo.

Da queda, um passo de dança,

Do medo, uma escada,

Do sonho, uma ponte,

Da procura, um encontro."

(Fernando Sabino)

#### **RESUMO**

ESTEVES, L. Análise e construção de aceleradores em hardware para o cálculo do menor caminho em planejamento de rotas de robôs. 2024. 110 p. Tese (Doutorado em Engenharia Elétrica) – Programa de Pós-Graduação em Engenharia Elétrica, Universidade Federal da Bahia, Salvador – BA, 2024.

Este trabalho propõe uma análise e otimização para o cálculo do menor caminho no planejamento de rotas para robôs móveis. A solução proposta visa apresentar uma alternativa de alto desempenho que possa atender às restrições de tempo necessárias para processamento em robôs. Para isso, foi construída uma arquitetura focada em paralelismo a ser embarcada em hardware dedicado. Através da exploração de paralelismo, a solução visa apresentar, além de uma melhoria de desempenho, uma adaptação dinâmica às mudanças no grafo de possíveis movimentações a ser analisado, uma vez que arestas podem ser inseridas ou removidas de forma temporalmente aleatória conforme as mudanças no ambiente. Este trabalho demonstra a arquitetura desenvolvida juntamente com seus resultados. O grafo da aplicação é atualizado de forma eficiente através de uma matriz de obstáculos, resultando em uma melhoria notável de 120 vezes para grafos com 1.024 nós. Ao utilizar um dispositivo de baixo custo como o Cyclone IV E, é atingido desempenho cerca de 20 vezes superior a de uma aplicação equivalente em software para um grafo com 1024 nós.

Palavras-chave: Dijkstra, Menor Caminho, PRM, FPGA, Robótica.

#### **ABSTRACT**

ESTEVES, L. Analysis and construction of hardware accelerators for shortest path calculation in robot route planning. 2024. 110 p. Tese (Doutorado em Engenharia Elétrica) – Programa de Pós-Graduação em Engenharia Elétrica, Universidade Federal da Bahia, Salvador – BA, 2024.

This work proposes an analisys and optimization for the calculation of the shortest path in route planning for mobile robots. The suggested solution aims to present a high-performance alternative that can meet the time constraints necessary for robots processing. To do so, we propose an architecture focused on parallelism to be embedded in dedicated hardware. Through the exploitation of parallelism, the solution aims to present, in addition to a performance improvement, a dynamic adaptation to changes in the graph of possible movements to be analyzed, since edges could be inserted or deleted in a temporally random manner as the environment changes. This work demonstrates the architecture developed together with its results. This application graph updating process efficiently updates obstacle matrices, resulting in a remarkable 120-fold improvement for 1024-node graphs. When utilizing a cost-effective device like the Cyclone IV E, it achieves approximately 20 times the performance of an equivalent software applications.

**Keywords:** Dijkstra, PRM, Shortest Path, FPGA, Robotics.

# LISTA DE ILUSTRAÇÕES

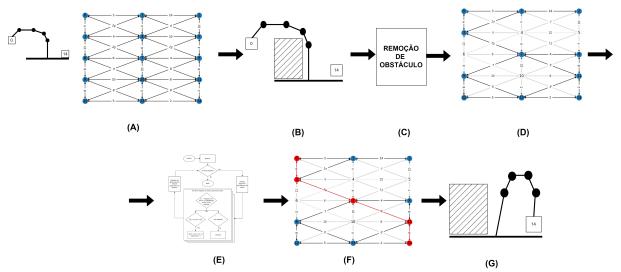

| Figura 1 –  | (A) Um robô e seu espaço de configuração representado em um grafo. (B)         |    |

|-------------|--------------------------------------------------------------------------------|----|

|             | Inserção de um obstáculo no ambiente. (C) Aplicação de técnica de remoção      |    |

|             | de obstáculos. (D) Espaço livre após remoção de obstáculos. (E) Usando um      |    |

|             | algoritmo de menor caminho. (F) Identificação do caminho que o robô deve       |    |

|             |                                                                                | 21 |

| Figura 2 –  | (A) Ambiente com obstáculos, inicio e objetivo, (B) um dos possíveis cami-     |    |

|             | nhos entre o início e o objetivo (Adaptado de Klancar et al. (2017))           | 25 |

| Figura 3 –  | Exemplo de grafo com 5 vértices e sete arcos (Extraído de Deo (2017))          | 26 |

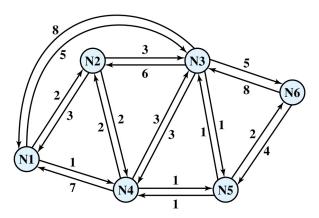

| Figura 4 –  | Exemplo de um grafo direcionado com 6 vértices (Extraído de Stallings (2007)). | 26 |

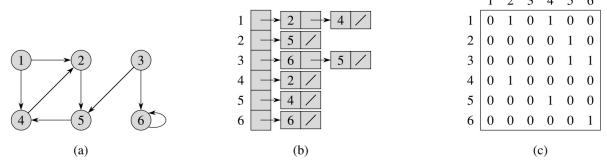

| Figura 5 –  | Representações de um grafo direcionado. (a) Dígrafo G com seis vértices e      |    |

|             | oito arcos. (b) Representação de G com listas de adjacência. (c) Representa-   |    |

|             | ção de G com matriz de adjacência (Extraído de Cormen et al. (2009))           | 27 |

| Figura 6 –  | Demonstração da aplicação de pesos em um campo potencial (Adaptado de          |    |

|             | Klancar <i>et al.</i> (2017))                                                  | 29 |

| Figura 7 –  | Evolução de um algoritmo RRT com 45 (A) e 2345(B) iterações (Extraído de       |    |

|             | LaValle (2006))                                                                | 29 |

| Figura 8 –  | Método PRM: a) fase de aprendizagem e b) fase de busca. (Extraído de           |    |

|             | Klancar <i>et al.</i> (2017))                                                  | 30 |

| Figura 9 –  | Fluxograma do algoritmo de Dijkstra                                            | 32 |

| Figura 10 – | Pseudocódigo do algoritmo de Dijkstra.                                         | 33 |

| Figura 11 – | Evolução do algoritmo de Dijkstra no grafo da Figura 4. (Extraído de Stal-     |    |

|             | lings (2007))                                                                  | 34 |

| Figura 12 – | Evolução do algoritmo A* (Extraído de Klancar <i>et al.</i> (2017))            | 36 |

| Figura 13 – | Comparação do A* (direita) com o Dijkstra (esquerda) (Extraído de Klancar      |    |

|             | et al. (2017))                                                                 | 37 |

| Figura 14 – | a) Discretização uniforme. b) Abordagem mais sofisticada ao aplicar uma        |    |

|             | maior resolução em regiões mais críticas. (Adaptado de Murray et al. (2016a)). | 39 |

| Figura 15 – |                                                                                | 43 |

| _           | -                                                                              | 45 |

|             |                                                                                | 45 |

| Figura 18 – Demonstração do grafo gerado com a terramenta construída. Os nós brancos      |     |

|-------------------------------------------------------------------------------------------|-----|

| são nós marcados como obstáculos e os em azul são os válidos que não fazem                |     |

| parte do menor caminho. O menor caminho encontrado entre os nós 0 e 29                    |     |

| está destacado em vermelho.                                                               | 53  |

| Figura 19 – Fluxograma do algoritmo de Dijkstra com a remoção de nós                      | 55  |

| Figura 20 – Estrutura da lista de adjacências com vizinhos ordenados de acordo com o      |     |

| custo do relacionamento.                                                                  | 56  |

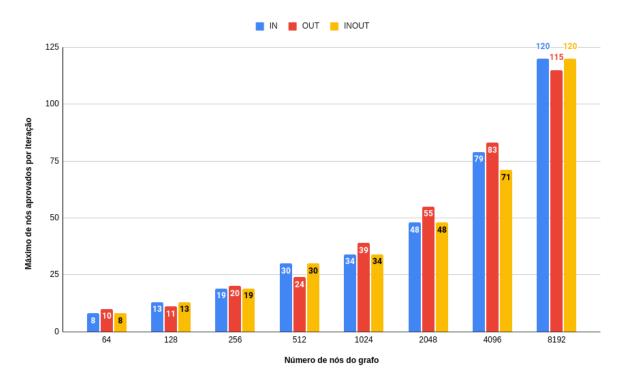

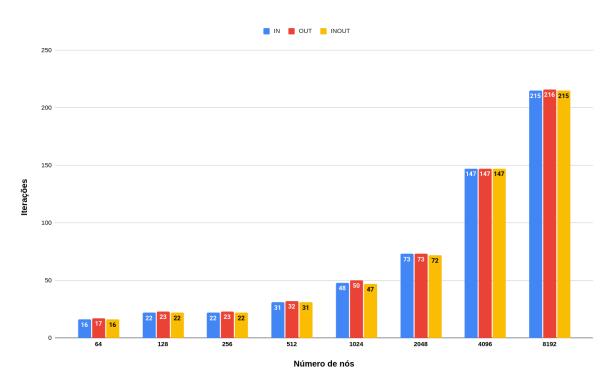

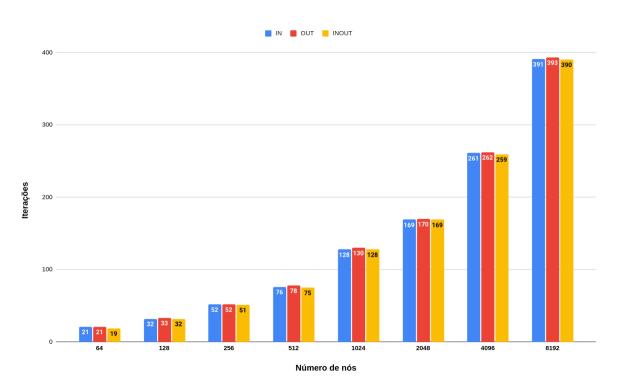

| Figura 21 – Comparação da quantidade máxima de nós aprovados por iteração para nós        |     |

| com até 8 relações                                                                        | 61  |

| Figura 22 – Comparação da quantidade máxima de nós aprovados por iteração para nós        |     |

| com até 4 relações.                                                                       | 62  |

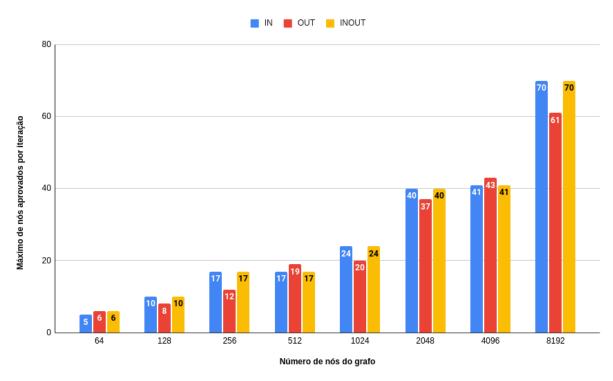

| Figura 23 – Comparação da média de nós aprovados por iteração para nós com até 8          |     |

| relações                                                                                  | 62  |

| Figura 24 – Comparação da média de nós aprovados por iteração para nós com até 4          |     |

| relações                                                                                  | 63  |

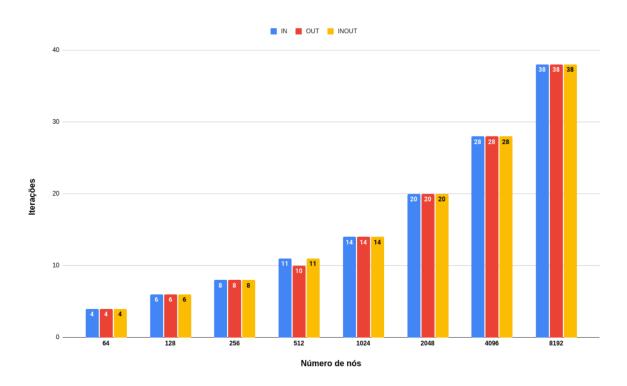

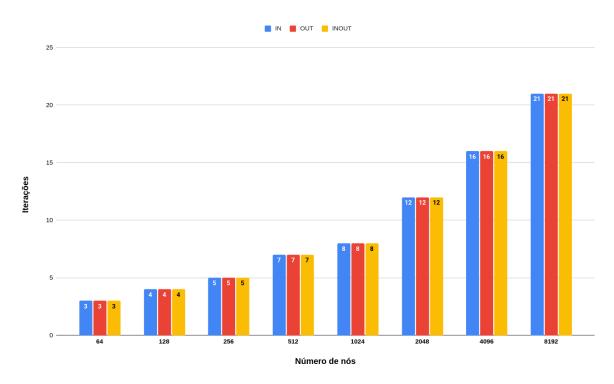

| Figura 25 – Comparação da quantidade total de iterações para nós com até 8 relações.      | 63  |

| Figura 26 – Comparação da quantidade total de iterações para nós com até 4 relações       | 64  |

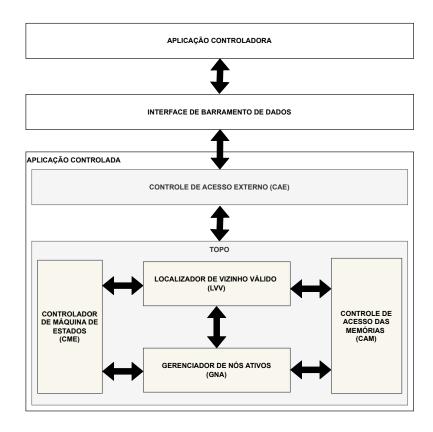

| Figura 27 – Arquitetura do topo do projeto                                                | 66  |

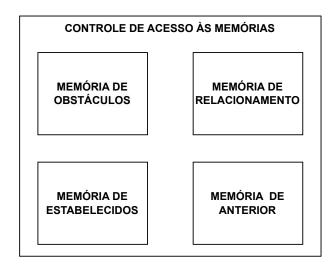

| Figura 28 – Controle de Acesso às Memórias                                                | 68  |

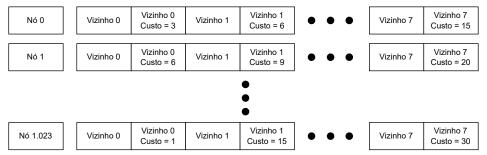

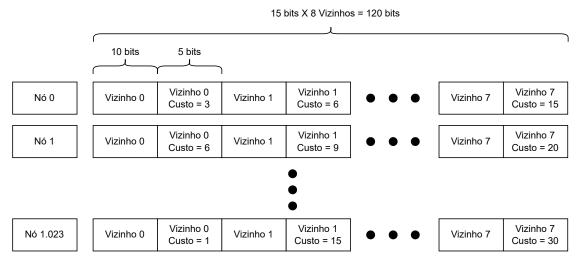

| Figura 29 – Lista de adjacências da <i>Memória de Relacionamentos</i> . Neste exemplo foi |     |

| criada uma lista com 1.023 nós (representação em 10 bits), cada um contendo               |     |

| até 8 vizinhos com custo máximo de 31 (5 bits). Cada entrada na lista será                |     |

| uma palavra de 120 bits                                                                   | 69  |

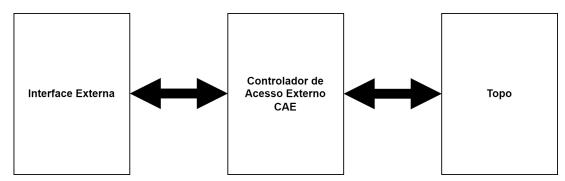

| Figura 30 – Interface externa com o <i>CAE</i>                                            | 71  |

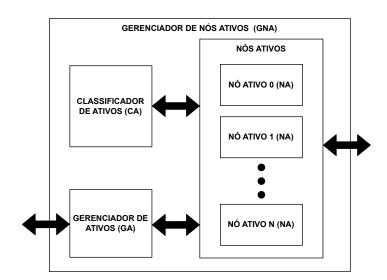

| Figura 31 – Gerenciador de Nós Ativos                                                     | 73  |

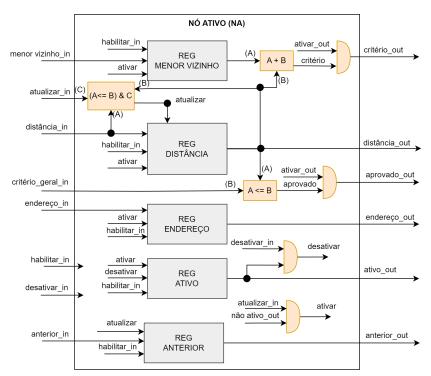

| Figura 32 – Nó Ativo                                                                      | 74  |

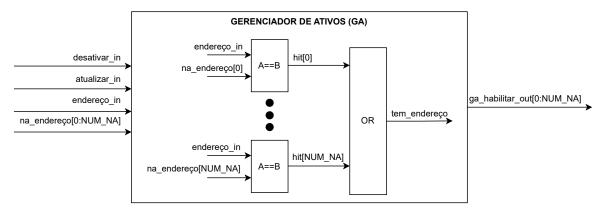

| Figura 33 – Gerenciador de Ativos                                                         | 74  |

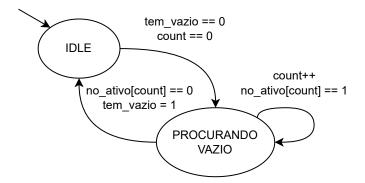

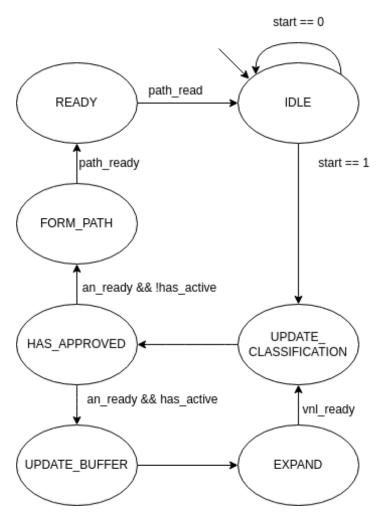

| Figura 34 – FSM do Gerenciador de Ativos                                                  | 75  |

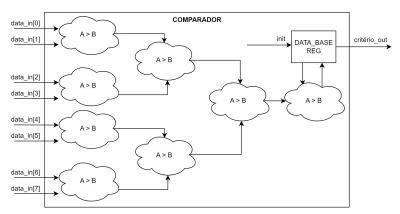

| Figura 35 – Bloco comparador do critério <i>OUT</i>                                       | 76  |

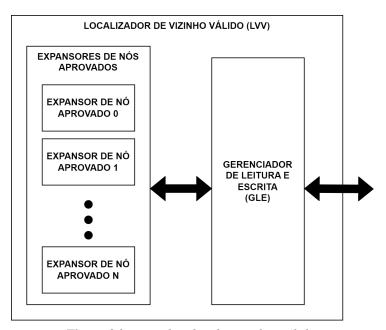

| Figura 36 – Localizador de Vizinho Válido                                                 | 77  |

| Figura 37 – Máquina de estados do <i>Localizador de Vizinho Válido</i>                    | 79  |

| Figura 38 – Protocolo de comunicação do <i>Gerenciador de Leitura e Escrita</i>           | 80  |

| Figura 39 – Fluxograma do processo de expansão de um nó                                   | 81  |

| Figura 40 – Máquina de estados do Expansor de Nó Aprovado                                 | 82  |

| Figura 41 – Máquina de estados finita do Controlador de Máquina de Estados                | 83  |

| Figura 42 – Fluxo do projeto em FPGA                                                      | 103 |

| Figura 43 – Projeto lógico                                                                | 105 |

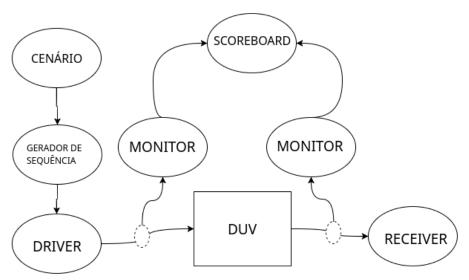

| Figura 44 – Ambiente de verificação.                                                      | 106 |

| Figura 45 – Projeto físico.                                                               | 107 |

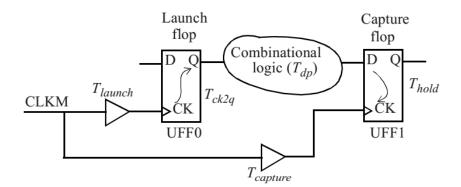

| Figura 46 – Caminho registrador para registrador (Extraído de Bhasker e Chadha (2009)). 108       |

|---------------------------------------------------------------------------------------------------|

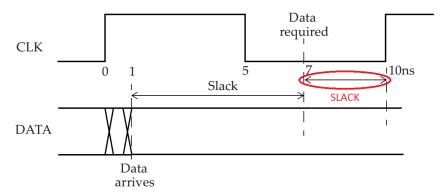

| Figura 47 – Análise de tempo de <i>slack</i> para <i>setup time</i> (Adaptada de Bhasker e Chadha |

| (2009))                                                                                           |

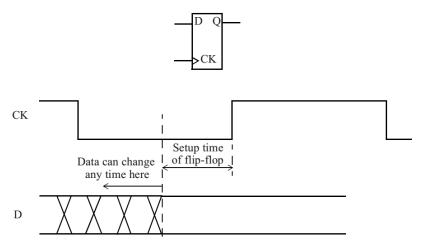

| Figura 48 – Setup time (Extraído de Bhasker e Chadha (2009))                                      |

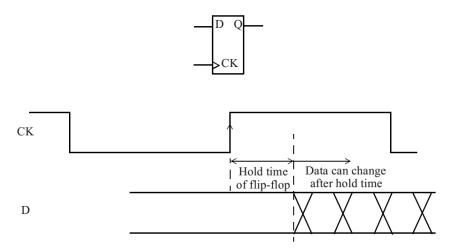

| Figura 49 – Análise de tempo de <i>hold time</i> (Extraído de Bhasker e Chadha (2009)) 110        |

## LISTA DE CÓDIGOS-FONTE

| 1 | Pseudocódigo do algoritmo de Dijkstra | _ | _ | <br>_ |  |  |  | _ |  | 3 | 3 |

|---|---------------------------------------|---|---|-------|--|--|--|---|--|---|---|

|   |                                       |   |   |       |  |  |  |   |  |   |   |

### LISTA DE TABELAS

| Tabela I – Aplicação do algoritmo de Dijkstra no grafo da Figura 4. (Adaptado de Stallings (2007)) | 34 |

|----------------------------------------------------------------------------------------------------|----|

| Tabela 2 – Tempo necessário em microssegundos para o planejamento de movimento                     |    |

| em diferentes abordagens. (Adaptado de Murray <i>et al.</i> (2016a))                               | 40 |

| Tabela 3 — Comparação dos trabalhos relacionados                                                   | 41 |

| Tabela 4 – Média de tempo de execução e média de nós processados. (Adaptado de                     | 11 |

| (VAIRA; KURASOVA, 2011))                                                                           | 47 |

| Tabela 5 – Resultados de simulação do critério <i>IN</i> com até 8 relações por nó                 | 58 |

| Tabela 6 – Resultados de simulação do critério <i>IN</i> com até 4 relações por nó                 | 58 |

| Tabela 7 – Resultados de simulação do critério <i>OUT</i> com até 8 relações por nó. (Fonte        |    |

| próprio autor)                                                                                     | 59 |

| Tabela 8 – Resultados de simulação do critério <i>OUT</i> com até 4 relações por nó                | 59 |

| Tabela 9 – Resultados de simulação do critério <i>INOUT</i> com até 8 relações por nó              | 60 |

| Tabela 10 – Resultados de simulação do critério <i>INOUT</i> com até 4 relações por nó             | 60 |

| Tabela 11 – Sinais do bloco <i>Controle de Acesso às Memórias</i> para um grafo com 1024 nós.      | 70 |

| Tabela 12 – Sinais do bloco <i>Controle de Acesso Externo</i> para um grafo com 1024 nós           | 72 |

| Tabela 13 – Sinais do bloco <i>Gerenciador de Nós Ativos</i> para um grafo com 1024 nós e 88       |    |

| Nó Ativo                                                                                           | 76 |

| Tabela 14 – Sinais de saída do bloco <i>Localizador de Vizinho Válido</i> para um grafo com        |    |

| 1024 nós                                                                                           | 78 |

| Tabela 15 – Sinais de saída do bloco Controlador de Máquina de Estados para um grafo               |    |

| com 1024 nós                                                                                       | 85 |

| Tabela 16 – Resultados com diferentes números de comparadores para um grafo com                    |    |

| 1.024 nós e até 8 relações                                                                         | 88 |

| Tabela 17 – Resultados com diferentes <i>Expansor de Nó Aprovado (ENA</i> ) para um grafo          |    |

| com 1.024 nós e até 8 relações                                                                     | 88 |

| Tabela 18 – Resultados de síntese com diferentes grafos para o FPGA EP4CE115F29C7                  | 89 |

| Tabela 19 – Dissipação de energia térmica de acordo com o tamanho do grafo em mW .                 | 89 |

| Tabela 20 – Resultados de transferências com diferentes tamanhos de barramento de                  |    |

| dados para um grafo com 1.024 nós e até 8 relações                                                 | 90 |

| Tabela 21 – Ganho de acordo com o tipo de transferência em um barramento de dados de               |    |

| 32 bits e tempo de processamento para diferentes tamanhos de grafos com                            |    |

| clock de 125 MHz                                                                                   | 90 |

| Tabela 22 – Resultados com diferentes quantidades de obstáculos   | 91 |

|-------------------------------------------------------------------|----|

| Tabela 23 – Resultados de síntese com diferentes famílias de FPGA | 91 |

| Tabela 24 – Comparação com modelos de referência                  | 92 |

| Tabela 25 – Comparação com outras soluções                        | 93 |

### LISTA DE ABREVIATURAS E SIGLAS

AMBA Advanced Microcontroller Bus Architecture

APSP menor caminho entre todos os pares (do inglês All-Pairs Shortest Path)

ASIC Circuitos Integrados de Aplicação Especifica (do inglês Application-Specific Inte-

grated Circuit)

BGL Boost Graph Library

CA Classificador de Ativos

CAE Controle de Acesso Externo

CAM Controle de Acesso às Memórias

CME Controlador de Máquina de Estados

CPU Unidade Central de Processamento (do inglês Central Processing Unit)

DOF grau de liberdade (do inglês *Degree of Freedom*)

DUT Design Under Test

DUV Design Under Verification

ENA Expansor de Nó Aprovado

FPGA Field Programmable Gate Array

FSM máquina de estados finita (do inglês Finite State Machine)

GA Gerenciador de Ativos

GLE Gerenciador de Leitura e Escrita

GMAE Gerenciador de Memórias com Acesso Externo

GNA Gerenciador de Nós Ativos

GPU Unidade de Processamento Gráfico (do inglês *Graphics Processing Unit*)

HPC Computação de alto desempenho (do inglês *High-Performance Computing*)

IE Interface Externa

LUT Look-Up Table

LVV Localizador de Vizinho Válido

MA Memória de Anteriores

ME Memória de Estabelecidos

MO Memória de Obstáculos

MPI Message Passing Interface

MR Memória de Relacionamentos

Mutex Mutual Exclusion

NA Nó Ativo

OpenCL Open Computing Language

OpenMP Open Multi-Processing

OSPF Open Shortest Path First

PCIe Peripheral Component Interconnect Express

PRM Probabilistic Roadmaps

RRT Rapidly exploring Random Tree

RTL Linguagem de Descrição de Hardware (do inglês *Register-Transfer Level*)

SDC Synopsys Design Constraints

SSSP problema do menor caminho a partir de uma fonte (do inglês Single Source Shortest

Path Problem)

STA Static Timing Analysis

UVM Metodologia de Verificação Universal (do inglês *Universal Verification Methodo-*

logy)

## SUMÁRIO

| 1     | INTRODUÇÃO                                        | 20        |

|-------|---------------------------------------------------|-----------|

| 1.1   | Objetivos Gerais                                  | 22        |

| 1.2   | Objetivos Específicos                             | 22        |

| 1.3   | Organização do documento                          | 23        |

| 2     | FUNDAMENTAÇÃO TEÓRICA                             | 24        |

| 2.1   | Planejamento de rotas                             | 24        |

| 2.2   | Utilização de grafos no planejamento de rotas     | 25        |

| 2.2.1 | Formas de representar um grafo                    | 27        |

| 2.3   | Mapa de navegação                                 | 28        |

| 2.4   | Algoritmos de menor caminho                       | 30        |

| 2.4.1 | Algoritmo Dijkstra                                | 31        |

| 2.4.2 | Algoritmo A*                                      | 34        |

| 3     | REVISÃO DA LITERATURA                             | 38        |

| 3.1   | Planejamento de rotas                             | 38        |

| 3.2   | Otimização do cálculo do menor caminho            | 41        |

| 3.2.1 | Particionamento do Grafo                          | 43        |

| 3.2.2 | Encontrando o menor caminho de forma bidirecional | 46        |

| 3.2.3 | Utilização de um critério para remoção dos nós    | 47        |

| 3.2.4 | O algoritmo de Dijkstra impaciente                | 48        |

| 4     | PROPOSTA PARA O ALGORITMO DE MENOR CAMINHO        | 50        |

| 4.1   | Construção de modelos de referência               | 52        |

| 4.2   | Especificação do algoritmo de menor caminho       | 53        |

| 4.2.1 | Análise dos critérios de remoção                  | <i>55</i> |

| 5     | RESULTADOS DA SIMULAÇÃO DO MODELO DE REFERÊNCIA   | 57        |

| 6     | ARQUITETURA DA PROPOSTA                           | 65        |

| 6.1   | Controle de Acesso às Memórias                    | 67        |

| 6.2   | Controle de Acesso Externo                        | 70        |

| 6.3   | Gerenciador de Nós Ativos                         | 72        |

| 6.4   | Localizador de Vizinho Válido                     | 76        |

| 6.5                | Controlador de Máquina de Estados             |

|--------------------|-----------------------------------------------|

| 7                  | AVALIAÇÃO DA ARQUITETURA                      |

| 7.1                | Encontrando a configuração ideal              |

| 7.2                | Resultados para diferentes tamanhos de grafos |

| 7.3                | Ganhos com a memória de obstáculos            |

| 7.4                | O efeito dos obstáculos                       |

| 7.5                | Resultados com diferentes FPGAs               |

| 7.6                | Comparações com modelos de referência         |

| 7.7                | Comparação com outras soluções                |

| 8                  | CONCLUSÃO                                     |

| 8.1                | Próximos passos                               |

| REFERÊN<br>APÊNDIC | CIAS                                          |

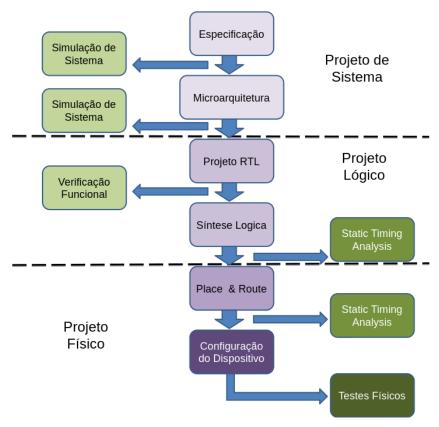

| APÊNDIC            | E B FLUXO DE PROJETO DIGITAL                  |

| B.1                | Projeto de Sistema                            |

| B.1.1              | <b>Especificação</b>                          |

| B.1.2              | Microarquitetura                              |

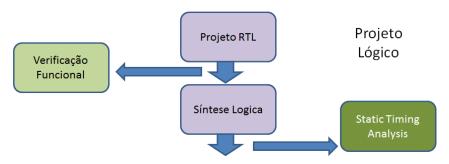

| B.2                | Projeto Lógico                                |

| B.2.1              | <b>Projeto RTL</b>                            |

| B.2.2              | <i>Síntese Lógica</i>                         |

| B.2.3              | Verificação Funcional                         |

| B.3                | Projeto Físico                                |

| B.3.1              | <i>Place and Route</i>                        |

| B.3.2              | Static Timing Analysis                        |

CAPÍTULO

1

### **INTRODUÇÃO**

O planejamento de caminhos é uma das atividades fundamentais na robótica, ele permite que um robô se desloque com segurança de um ponto de origem A para um ponto de destino B. Para realizar essa tarefa é necessário que o robô, através dos seus diversos sensores, mapeie o ambiente no qual está inserido, detectando obstáculos e possíveis caminhos livres. A partir desse mapeamento do ambiente, o robô passa então a ter à sua disposição diversas possibilidades diferentes de alcançar o destino.

De um modo geral, um caminho pode ser definido como uma sequência de passos entre o ponto inicial e todos os pontos que ligam o início ao fim do caminho. Para realizar cada um desses passos, o robô aloca uma quantidade de energia proporcional ao esforço necessário. Esse esforço, ou peso do deslocamento, pode variar de acordo com diversos fatores, como a posição atual do robô e a configuração do ambiente no qual ele está inserido no momento. Em uma ladeira, por exemplo, subir é mais difícil do que descer.

Desse modo, o esforço total de uma determinado caminho pode ser calculado como a soma do esforço de todos os passos intermediários entre a origem e o destino. Considerando isso, ao realizar o planejamento do caminho a ser seguido, é mais interessante que aquele com o menor esforço total seja utilizado, visto que um melhor caminho resultará em um menor custo energético e, provavelmente, menor tempo de execução.

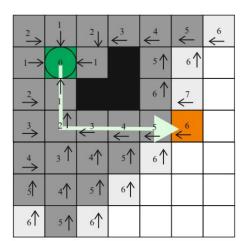

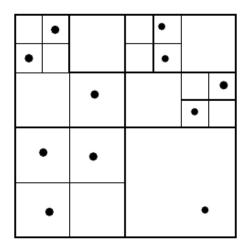

A construção do menor caminho está inserida em um contexto em que várias etapas devem ser realizadas para que um planejamento eficiente de caminhos possa ser realizado. Inicialmente, um grafo representando o espaço de configuração do robô é construído em uma etapa de pré-processamento (Figura 1A). Este grafo captura todas as posições de configuração possíveis e suas relações, fornecendo uma representação das capacidades de movimentação do robô.

Logo após, o algoritmo *Probabilistic Roadmaps* (PRM) realiza a amostragem das configurações válidas e as conecta através de caminhos livres de colisões. Durante essa etapa é

Figura 1 – (A) Um robô e seu espaço de configuração representado em um grafo. (B) Inserção de um obstáculo no ambiente. (C) Aplicação de técnica de remoção de obstáculos. (D) Espaço livre após remoção de obstáculos. (E) Usando um algoritmo de menor caminho. (F) Identificação do caminho que o robô deve seguir. (G) Aplicação pelo robô da sequência de configuração.

identificada a presença de obstáculos e o espaço livre disponível para a navegação do robô é construído. Quando obstáculos são introduzidos no ambiente durante a operação do robô (Figura 1B), o algoritmo PRM atualiza dinamicamente o grafo existente (Figura 1C), removendo os nós comprometidos devido ao obstáculo, objetivando criar caminhos livres que permitem o movimento contínuo do robô. Esta adaptação dinâmica garante uma navegação livre de obstáculos e otimiza o caminho do robô (Figura 1D).

Para determinar o caminho ideal entre os pontos de origem e destino, algoritmos de menor caminho, como o algoritmo de Dijkstra, são empregados (Figura 1E). O problema do menor caminho a partir de uma fonte (do inglês *Single Source Shortest Path Problem*) (SSSP) pretende encontrar o menor caminho entre um nó origem e um nó destino, considerando o esforço existente no processo de deslocamento do robô. Esses algoritmos consideram os relacionamentos e restrições no grafo atualizado dinamicamente. Ao analisar a estrutura do grafo e as mudanças no ambiente, são alcançadas soluções robustas e confiáveis de planejamento de caminhos. Isso permite que o robô navegue da configuração inicial até a configuração de destino de forma eficiente e segura (Figuras 1F e 1G). Ao otimizar o cálculo do menor caminho, o objetivo deste trabalho é atuar nas etapas E e F da Figura 1.

Neste contexto, este trabalho apresenta uma proposta que solucione o SSSP de forma rápida e eficiente, viabilizando sua utilização em aplicações que necessitam de um baixo tempo de processamento. Além disso, a solução deve realizar o cálculo do menor caminho considerando que o ambiente não é estático, ou seja, obstáculos podem surgir ou desaparecer durante a sua execução, necessitando assim de uma representação dinâmica do ambiente, com possíveis caminhos também dinâmicos. Tais requisitos exigem que a solução trabalhe de forma coordenada e otimizada com os outros componentes do processo, como sensores e algoritmos de mapeamento

do ambiente.

Quando se deseja realizar otimizações de determinados algoritmos, uma das alternativas que se destaca é a utilização de dispositivos do tipo *Field Programmable Gate Array* (FPGA). Aplicações com baixa intensidade operacional e com maior tratamento de valores escalares (em oposição à vetorização) dificultam a exploração do desempenho de pico oferecido por soluções baseadas em Unidade de Processamento Gráfico (do inglês *Graphics Processing Unit*) (GPU), abrindo caminho para uma melhor exploração de desempenho por FPGAs. Atrelado a isso, os FPGAs, por apresentarem uma arquitetura especializada para a aplicação, possuem uma melhor eficiência na utilização dos recursos e, consequentemente, apresentam um menor consumo energético.

Uma das principais distinções desta proposta está no processo de atualização do grafo (Figura 1F). Diferentemente das alternativas tradicionais que geram um novo grafo a cada iteração, esta proposta apenas atualiza uma matriz contendo obstáculos. Como resultado, há uma melhoria notável de 120 vezes no processo de atualização para grafos compreendendo 1.024 nós.

Para viabilizar o paralelismo, foi realizado um levantamento bibliográfico do estado da arte das soluções de busca do menor caminho. Como resultado dessa busca foi implementada uma solução utilizando um critério de seleção para remoção e atualização de nós em paralelo.

O projeto busca obter uma solução que não necessite de muitos recursos computacionais, resultando em um produto que possa ser empregado em dispositivos de baixo custo e consumo enérgico. Nesse sentido, como prova de conceito, foi utilizado um FPGA econômico como o Cyclone IV E, onde se atingiu um desempenho aproximadamente 12 vezes melhor em comparação com uma aplicação equivalente em software.

### 1.1 Objetivos Gerais

O objetivo deste trabalho é apresentar uma contribuição para a resolução do problema do menor caminho entre dois nós de um grafo direcionado com foco no baixo tempo de resposta. Considera-se que as arestas do grafo possam ser removidas ou adicionadas durante o processamento, conforme a inserção ou remoção de obstáculos no espaço de configuração do robô.

Como resultado se obtêm uma solução que pode ser integrada em um projeto de movimentação de Robôs, seja em um mesmo circuito integrado ou através da conexão com controlador localizado em um dispositivo externo.

### 1.2 Objetivos Específicos

Realizar levantamento bibliográfico sobre o estado da arte na busca do menor caminho;

- Definir um algoritmo que permita paralelismo para calcular o menor caminho entre dois pontos em um grafo direcionado;

- Desenvolver uma solução que possa ser utilizada na movimentação de robôs;

- Construir uma arquitetura para essa solução;

- Testar e validar a arquitetura construída, obtendo resultados positivos.

### 1.3 Organização do documento

Este trabalho está organizado conforme descrito na sequência.

No Capítulo 2 é apresentada a fundamentação teórica necessária para a construção desta proposta. Nele são expostas técnicas utilizadas no planejamento de rotas, formas de representação das possíveis posições de movimentação do robô e alguns algoritmos de menor caminho.

O Capítulo 3 discorre sobre o ambiente científico em que a proposta está inserida, apresentando alguns trabalhos relacionados com o projeto e que serviram como norteadores para o desenvolvimento da solução. São exploradas também técnicas de otimização relatadas na literatura.

As contribuições desta proposta ao planejamento de rotas de robôs móveis são apresentadas no Capítulo 4 através da proposição de uma arquitetura. Nesse capítulo são expostas também as motivações e justificativas da proposta.

Em seguida, no Capítulo 5, são mostrados alguns resultados de simulações do algoritmo utilizado.

A partir dos resultados obtidos em simulação e da construção do modelo de referência, no Capítulo 6 é apresentada a microarquitetura do projeto que implementa a proposta. Os resultados de síntese e simulação da Linguagem de Descrição de Hardware (do inglês *Register-Transfer Level*) (RTL) construída a partir da arquitetura proposta são discutidos no Capítulo 7.

No Capítulo 8 são apresentadas as considerações finais sobre o que foi desenvolvido e os resultados obtidos, além da discussão de perspectivas futuras para a extensão da proposta.

Por fim, o Apêndice B aborda o fluxo de projeto digital com enfoque no desenvolvimento em FPGA que foi utilizado para a confecção desta proposta .

CAPÍTIIIO

2

### **FUNDAMENTAÇÃO TEÓRICA**

Neste capítulo são abordados conceitos importantes utilizados durante a análise e elaboração da proposta. Inicialmente serão descritos os fundamentos teóricos necessários ao planejamento de rotas para robôs móveis e à utilização de grafos para mapear as opções de movimentação de um robô. Por fim, são apresentados alguns algoritmos que calculam o menor caminho entre dois nós de um grafo.

### 2.1 Planejamento de rotas

Da mesma forma que um motorista de ônibus precisa construir um mapa mental da rodovia que está trafegando, identificando rotas possíveis e obstáculos, um robô necessita também mapear o ambiente no qual está inserido. Desse modo, considerando seu grau de liberdade (do inglês *Degree of Freedom*) (DOF), ele busca primeiramente identificar como pode se movimentar, ou seja, quais são suas posições possíveis em um cenário livre de obstáculos. Após esse conhecimento, posições ocupadas por obstáculos são removidas e então se obtém o real espaço livre para movimentação.

Desta maneira, o conjunto de todas as posições possíveis que um robô pode apresentar em um espaço com n dimensões é denominado espaço de configuração (Q). Nesse espaço, cada estado possível do robô é representado por uma posição de configuração (q). Posições que coincidem com algum tipo de obstáculo que possa comprometer ou até mesmo impedir a movimentação do robô fazem parte do conjunto de obstáculos  $(Q_{obst})$ . Ao subtrair do espaço de configuração todas as configurações comprometidas pelos obstáculos, obtém-se o conjunto do espaço livre  $(Q_{livre} = Q - Q_{obst})$ , que é a região responsável pela definição das posições transitáveis de um robô móvel (KLANCAR et~al., 2017).

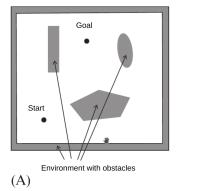

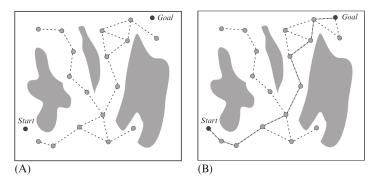

O planejamento de rotas consiste na tarefa de encontrar um caminho contínuo que levará o robô de uma configuração de início até a de destino através do conjunto do espaço livre (ver

Figura 2). Como existem vários caminhos possíveis até o destino, os seguintes critérios podem ser utilizados para identificar um caminho ótimo (KLANCAR *et al.*, 2017):

Figura 2 – (A) Ambiente com obstáculos, inicio e objetivo, (B) um dos possíveis caminhos entre o início e o objetivo (Adaptado de Klancar *et al.* (2017)).

(B)

- 1. O tamanho do caminho deve ser o menor;

- 2. Deve ser aquele em que o robô consegue atravessar no menor intervalo de tempo;

- 3. Deve estar o mais longe possível dos obstáculos;

- 4. Deve ser suave, sem transições bruscas;

- 5. Deve considerar limitações de movimento.

### 2.2 Utilização de grafos no planejamento de rotas

Para realizar o planejamento de caminhos, é necessário representar computacionalmente o espaço de configuração com seus obstáculos e espaço livre. Em aplicações onde a área de movimentação do robô está limitada a um plano 2D, é comum a utilização de uma grade como método de representação. No entanto, robôs que possuem uma quantidade maior de articulações necessitam ser representados por estruturas mais complexas, como os grafos, devido à heterogeneidade de suas relações. Essas estruturas permitem uma maior flexibilidade de relacionamentos entre as posições de configuração.

Um grafo de transição de estados para um determinado robô pode ser formado reduzindo o espaço livre a um determinado número de configurações intermediárias e suas transições. Cada uma das configurações representa um nó do grafo, e as conexões são simbolizadas por linhas ou arestas, identificando ações necessárias para a movimentação do sistema entre os estados ou nós.

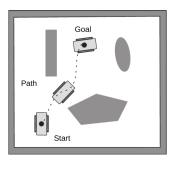

Um grafo G = (V, E) é formado por um conjunto de vértices ou nós  $V = v_1, v_2,...,v_n$  e um conjunto de arestas ou arcos  $E = e_1, e_2,...,e_m$ . Cada aresta é formada por um par  $(v_i, v_j)$ , onde  $v_i$  e  $v_j \in V$  (DEO, 2017). Em alguns casos, as arestas possuem um terceiro componente  $c_{ij}$  que define seu peso ou custo. Grafos que possuem esse componente são denominados grafos

ponderados (WEISS, 2012; MEHLHORN, 2012). Arestas cujo par possui o mesmo vértice ( $v_i$ ,  $v_i$ ) são denominadas laços (ver aresta  $e_1$  da Figura 3). É possível também a existência de duas arestas diferentes formadas por um mesmo par (ver arestas  $e_5$  e  $e_4$  da Figura 3), que nesse caso são chamadas de arestas paralelas.

Figura 3 – Exemplo de grafo com 5 vértices e sete arcos (Extraído de Deo (2017)).

Grafos que não possuem nem arestas paralelas nem laços são denominados grafos simples (DEO, 2017). Quando uma aresta é formada por um par ordenado, obtém-se um grafo direcionado ou dígrafo, cujo sentido do arco é fixo (ver Figura 4) (WEISS, 2012; PAPADIMITRIOU; STEIGLITZ, 1998).

Figura 4 – Exemplo de um grafo direcionado com 6 vértices (Extraído de Stallings (2007)).

Um caminho em um grafo é formado por uma sequência de vértices  $v_1, v_2, v_3, ..., v_N$ , onde  $(v_i, v_{i+1}) \in V$  para  $1 \le i < N$ . O tamanho de um caminho é mensurado de acordo com a quantidade de arestas presentes no mesmo. O custo de um caminho  $v_1, v_2, v_3, ..., v_N$  é calculado a partir dos seus pesos, sendo definido por  $\sum_{i=1}^{N-1} c_{i,i+1}$ . Em um grafo podem existir caminhos simples, compostos por vértices distintos, com exceção dos vértices iniciais e finais que podem ser os mesmos (WEISS, 2012).

Grafos também podem ser classificados de acordo com as suas conexões. Nesse contexto, encontram-se os dígrafos fortemente conexos, aqueles que, para cada vértice, existe um caminho que se conecta com todos os outros. Quando cada par de vértices possuir uma aresta, obtém-se um grafo completo (WEISS, 2012).

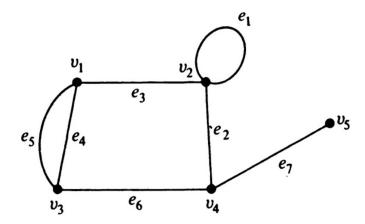

#### 2.2.1 Formas de representar um grafo

Comumente os grafos podem ser representados como uma matriz de adjacência ou como listas de adjacência. Na figura 5, vemos um dígrafo (a) representado como listas de adjacência (b) e matriz de adjacência (c).

Figura 5 – Representações de um grafo direcionado. (a) Dígrafo G com seis vértices e oito arcos. (b) Representação de G com listas de adjacência. (c) Representação de G com matriz de adjacência (Extraído de Cormen *et al.* (2009)).

A matriz de adjacência é formada através de uma matriz booleana  $A_G = (a_{ij})_{1 \leq i,j \leq n}$  de dimensões  $|V| \ge |V|$ . Os arcos existentes em um grafo direcionado são identificados na matriz de acordo com a equação 2.1. Nesse tipo de abordagem, os requisitos de armazenamento são de  $\Theta(n^2)$  (MEHLHORN, 2012). A utilização da matriz de adjacência é uma boa escolha quando se utilizam grafos densos,  $|E| = \Theta(V^2)$ .

$$a_{ij} = \begin{cases} 1 & \text{se } (i,j) \in E \\ 0 & \text{se } (i,j) \notin E \end{cases}$$

(2.1)

Uma matriz de adjacência pode ser utilizada para armazenar o peso dos arcos em grafos com pesos. Nessa situação, o peso  $c_{ij}$  de um arco (i, j) pode ser armazenado na linha i e coluna j da matriz de adjacência, juntamente com a identificação da ligação entre os vértices (CORMEN et al., 2009). Pode-se também definir um valor muito pequeno ou muito grande de peso, quando não existir a ligação entre os vértices, ou o valor do peso quando a ligação existir (WEISS, 2012).

Em situações em que o grafo não é denso, ou seja, é esparso, o método de representação mais recomendado é a lista de adjacência (Adj) de |V|, que permite a criação de uma lista para cada vértice de V. A lista de adjacência representando o vértice  $u \in V$ , por exemplo, aponta para todos os nós vizinhos a u no grafo. Nessa abordagem, as listas são normalmente representadas

de forma não ordenada e necessitam de um armazenamento com  $\Theta(V+E)$  dimensões, sendo E a soma do tamanho de todas as listas adjacentes (CORMEN *et al.*, 2009).

Listas de adjacência podem ser adaptadas para permitir a representação de grafos com pesos. Nessa situação, o peso  $c_{ij}$  de um arco (i,j) pode ser armazenado nas listas de adjacência dos nós i e j juntamente com seus pares. Uma das desvantagens da utilização de listas de adjacência é devido a uma maior complexidade em identificar se uma aresta (u,v) está presente no grafo. Para isso, é necessário investigar na lista de adjacência de um dos vértices (Adj[u]) ou Adj[v] se o outro par está presente (CORMEN *et al.*, 2009).

A partir das informações expostas, é importante ressaltar dois pontos: a maioria dos grafos utilizados em aplicações são esparsos, ou seja,  $|E| \leq |V|^2$ ; a escolha da representação pode ter uma influência expressiva no desempenho do algoritmo (MEHLHORN, 2012). Como apresentado em (MEHLHORN, 2012) muitos problemas que podem ser resolvidos em tempo linear, O(|V|+|E|), utilizando listas de adjacência, podem apresentar um tempo de execução de  $\theta(|V|^2)$  quando a matriz de adjacência é utilizada.

### 2.3 Mapa de navegação

De um modo geral, o planejamento de rotas pode ser dividido em duas fases: i) uma fase inicial de planejamento, que realiza a construção de um mapa do ambiente; e ii) uma fase de consulta, que utiliza os resultados da fase de planejamento para criar um caminho entre dois pontos. Vale ressaltar que a fase de planejamento é consideravelmente mais custosa (ROBOTICS, 2011).

A fase de planejamento gera como resultado um mapa de navegação formado a partir do mapeamento das conexões possíveis entre os nós presentes no espaço livre. Ele é construído de acordo com a geometria do ambiente no qual o robô está inserido, sendo seu principal desafio encontrar a quantidade mínima de caminhos que possibilitem ao robô alcançar todas as configurações contidas no conjunto do espaço livre.

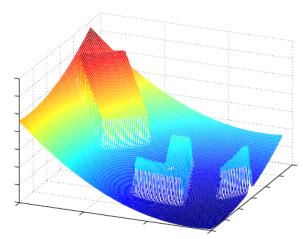

Para sua construção, diferentes técnicas podem ser utilizadas. Os campos potenciais (ver Figura 6), por exemplo, criam pesos imaginários para representar o ambiente. O destino apresenta o menor peso, sendo que quanto mais distante do destino um ponto está, maior será o peso aplicado, além disso, obstáculos também possuem pesos maiores. Dessa forma, o robô deve seguir o gradiente negativo a fim de alcançar o objetivo.

Outra técnica utilizada é a baseada em amostras, na qual pontos aleatórios são coletados e métodos de detecção de colisão são aplicados visando identificar se esses são pontos pertencentes ao espaço livre. A partir do conjunto desses pontos, um caminho do início até o destino pode ser formado. Nessa abordagem não é necessário calcular o espaço livre, etapa que geralmente consome grande quantidade de recursos computacionais em robôs com maiores graus

Figura 6 – Demonstração da aplicação de pesos em um campo potencial (Adaptado de Klancar *et al.* (2017)).

de liberdade. Uma variante desse método é o *Rapidly exploring Random Tree* (RRT), que busca o caminho a partir de um ponto inicial até um ponto destino, adicionando a cada iteração uma nova conexão próxima ao ponto atual selecionado aleatoriamente (ver Figura 7).

Figura 7 – Evolução de um algoritmo RRT com 45 (A) e 2345(B) iterações (Extraído de LaValle (2006)).

Apesar da fase de consulta ser consideravelmente mais rápida que a fase de planejamento, caso o objetivo mude, a fase de planejamento deve ser executada novamente. Além disso, em um cenário que necessite solicitar diversos pares origem e destino  $(q_i,q_d)$  para um conjunto de robôs e obstáculos fixos, as técnicas apresentadas anteriormente devem ser reprocessadas diversas vezes, possivelmente até repetindo os mesmos pares, gerando assim um retrabalho.

Desse modo, a disparidade nos custos de planejamento e consulta levou ao desenvolvimento de métodos de mapa de navegação nos quais a busca pudesse incluir diversas posições de início e objetivo (ROBOTICS, 2011). Assim, em vez de tratar cada par individualmente, se investe em um pré-processamento mais completo, de modo a simplificar o processo de buscas posteriores ao se incluir diversos pontos na análise.

Nesse contexto, primeiramente introduzidas por (KAVRAKI PETR SVESTKA; OVER-

MARS, 1996), surgem as PRM como um método para realizar a construção de um mapa de navegação quando se possuem diversos pontos de início e destino. Essa técnica realiza também as fases de pré-processamento e busca. A fase de pré-processamento (ver Figura 8a), consiste na construção do mapa de navegação de modo a viabilizar a resolução rápida de buscas entre nós presentes na região do espaço livre. A fase de busca (ver Figura 8b), realizada após o pré-processamento, consiste em conectar dois pares  $q_i$  e  $q_d$  ao grafo e, através de um algoritmo de busca do menor caminho, formar o caminho ótimo entre esses pares (LAVALLE, 2006).

É importante ressaltar que o processo de reconstrução do mapa de navegação é realizado sempre que ocorre uma mudança na configuração dos obstáculos do ambiente, e exclusivamente nesse tipo de situação. Em termos de consumo computacional, o processo de detecção de colisões na fase de aprendizagem é o que mais utiliza recursos.

Figura 8 – Método PRM: a) fase de aprendizagem e b) fase de busca. (Extraído de Klancar et al. (2017)).

### 2.4 Algoritmos de menor caminho

Como apresentado em (DEO, 2017) a utilização de algoritmos de busca do menor caminho é um dos temas mais abordados na teoria dos grafos. Existem diversas implementações possíveis para esse tipo de problema, cada uma com suas peculiaridades e focadas em resolver problemas específicos através da utilização de soluções customizadas para cada problema. De um modo geral, esses algoritmos podem ser divididos em cinco grupos (DEO, 2017):

- 1. Menor caminho entre dois nós específicos;

- 2. Menor caminho de um vértice para todos os outros;

- 3. Menor caminho entre todos os pares de nós;

- 4. Menor caminho entre vértices específicos que passam por determinados vértices;

- 5. Menor caminho entre diversos vértices.

Como o objetivo desta proposta é o desenvolvimento de algoritmos de menor caminho para aplicações com robôs móveis, nas quais se deseja deslocar o robô de um nó i para um

nó *j* no grafo, os três últimos grupos não serão discutidos nesta tese. Além disso, em algumas situações, o primeiro grupo é igual ao segundo, pois, durante o processo de busca do menor caminho entre dois vértices, é possível que seja necessário encontrar o menor caminho entre todos os outros vértices, Dessa forma, será suficiente discutir apenas o primeiro grupo (WEISS, 2012).

O problema de encontrar o menor caminho entre dois nós específicos s e t em um dígrafo G com n vértices pode ser representado como uma matriz de adjacência  $D = [d_{ij}]$  com dimensão n x n, onde  $d_{ij}$  representa o peso do arco, sendo:  $d_{ij} \ge 0$  o custo do movimento do vértice i para j;  $d_{ii} = 0$ ; e  $d_{ij} = \infty$  quando não existir arco entre i e j. Nesse tipo de problema, a desigualdade triangular não precisa ser satisfeita, ou seja,  $d_{ij} + d_{jk}$  pode ser menor do que  $d_{ik}$ . Desta forma, nem sempre o arco direto  $d_{ik}$  entre dois vértices será o menor caminho.

Os algoritmos de busca em grafos podem ser classificados como informados ou não informados. Os algoritmos não informados são aqueles que não utilizam informações além da definição do problema. Eles realizam buscas sistemáticas no grafo e não distinguem nós mais promissores dos menos promissores. Já os algoritmos de busca informados possuem informações adicionais sobre os nós e, sendo assim, conseguem identificar nós mais promissores, gerando uma busca mais eficiente. Estes algoritmos também podem ser classificados como completos ou incompletos. Eles são completos quando conseguem achar uma solução, se ela existir, e incompletos quando, mesmo existindo uma solução, podem não encontrá-la (KLANCAR *et al.*, 2017).

Nas seções a seguir, a título de comparação e melhor entendimento, dois dos principais algoritmos utilizados na busca do menor caminho em um grafo serão expostos, sendo eles: o algoritmo de Dijkstra e o A\*.

#### 2.4.1 Algoritmo Dijkstra

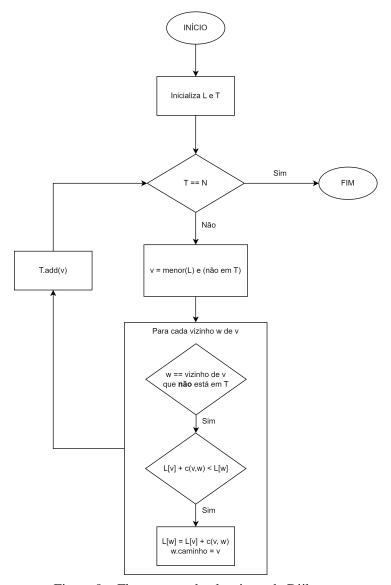

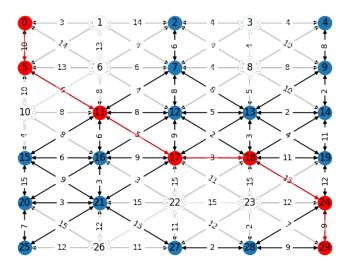

O algoritmo de Dijkstra (DIJKSTRA *et al.*, 1959) foi definido em (STALLINGS, 2007) como uma busca do menor caminho a partir de um fonte para todos os outros nós. Caso todos os pesos das conexões entre os nós do grafo possuam um valor maior do que zero, o algoritmo de Dijkstra se apresenta como completo e ótimo. Nesse algoritmo, o tamanho do caminho analisado aumenta gradativamente a cada iteração. Na iteração k, o menor caminho para os k nós mais próximos da fonte são determinados e agrupados em um conjunto T. Na iteração k+1, o nó que não está em T e que possui o menor caminho para a fonte é adicionado a T. À medida que cada nó é adicionado em T, o seu caminho para a fonte é definido. Na Figura 9 é mostrado o fluxograma do algoritmo, considerando-se que:

- N = conjunto de nós no grafo;

- s = fonte;

- T =conjunto de nós analisados até o momento;

- c(i,j) = custo do nó i para o nó j, sendo c(i,i) = 0,  $c(i,j) = \infty$  se os nós não estão diretamente conectados e  $c(i,j) \ge 0$  se o nó possui uma conexão direta; e

- L(n) = custo do menor caminho entre a fonte s e o nó n na iteração atual. Ao final do algoritmo será o menor caminho possível entre esses dois nós.

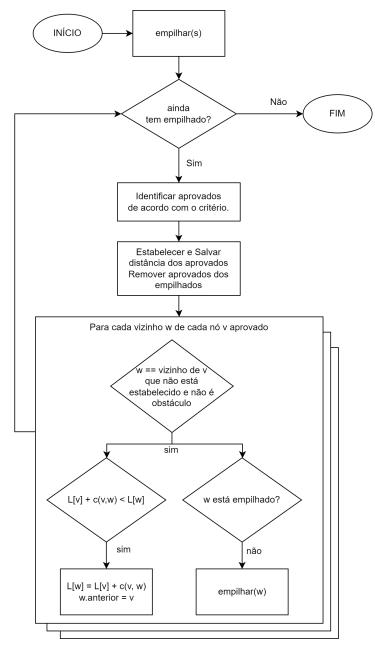

Figura 9 – Fluxograma do algoritmo de Dijkstra.

O algoritmo pode ser dividido em três passos: 1) Inicializar; 2) Coletar próximo nó; e 3) Atualizar os menores caminhos. Os passos 2 e 3 são repetidos até T=N.

O primeiro passo inicializa o conjunto T apenas com a fonte  $(T = \{s\})$  e inicializa o custo para os vizinhos da fonte (ver Equação 2.2). Após as inicializações, se inicia o segundo passo, onde é encontrado e incorporado a T um nó vizinho que não está em T e que possui a menor distância até a fonte (ver Equação 2.3). Ao escolher sempre o vértice com menor custo até

o momento, pode-se ter certeza de que não existe caminho algum menor que o atual, visto que o algoritmo evolui sempre coletando o vértice com menor distância até a fonte (LEE; HUBBARD, 2015). Nesse momento, é também incorporado o arco que incide neste nó e um nó em T que contribui para o caminho.

$$L(n) = c(s, n) \text{ para n } \neq s \tag{2.2}$$

procure

$$x \notin T$$

sendo que  $L(x) = \min_{j \notin T} L(j)$  (2.3)

O último passo - atualizar os menores caminhos - expresso de acordo com a equação 2.4, atualiza o caminho de *s* para *n* quando encontrado um valor menor do que o atualmente armazenado. Satisfeita essa condição, o caminho de *s* para *n* é modificado para o caminho de *s* para *x* concatenado com o arco de *x* para *n*. Quando todos os nós forem analisados o algoritmo é finalizado.

$$L(n) = \min[L(n), L(x) + c(x, n)] \text{ para todo } n \notin T$$

(2.4)

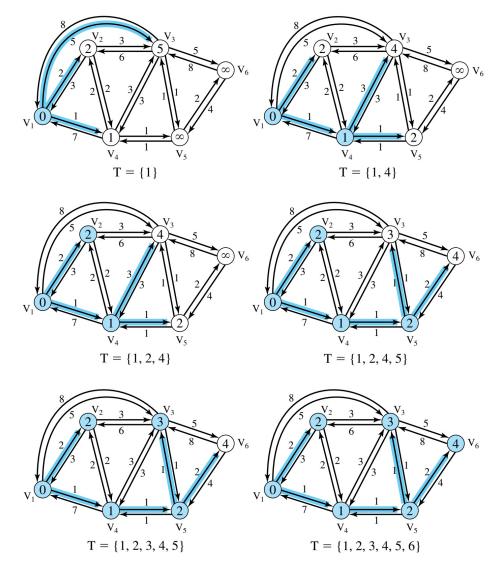

Na Figura 10 é mostrado o pseudocódigo de uma possível implementação do algoritmo de Dijkstra de acordo com o que foi apresentado nesta seção. Na Tabela 1 e na Figura 11 vemos a evolução do algoritmo Dijkstra no dígrafo da Figura 4, considerando o vértice *N*1 como fonte.

```

Código-fonte 1 – Pseudocódigo do algoritmo de Dijkstra

1 dijkstra(s, N):

# Passo 1

3

para cada Vertice n em N:

4

L[n] = c(s,n)

5

s.distancia = 0

6

T = \{s\}

7

enquanto (T é diferente de N): # Até buscar todos os nós

8

# Passo 2

9

Vertice v = (menor(L)) e (não em T) # vertice com a

menor distância L[x]

10

# e que não faz

parte de T;

11

# Passo 3

12

para cada w em vizinhos (v):

13

se (w não está em T):

14

se(L[v] + c(v,w) < L[w]):

15

L[w] = L[v] + c(v,w) \# atualiza w

w.caminho = v # atualiza o caminho de w

16

T. adicionar(v)

17

```

Figura 10 – Pseudocódigo do algoritmo de Dijkstra.

| Iteração | T                  | L(2) | caminho | L(3) | caminho | L(4) | caminho | L(5)     | caminho | L(6)     | caminho |

|----------|--------------------|------|---------|------|---------|------|---------|----------|---------|----------|---------|

| 1        | {1}                | 2    | 1-2     | 5    | 1-3     | 1    | 1-4     | INFINITO | -       | INFINITO | -       |

| 2        | {1,4}              | 2    | 1-2     | 4    | 1-4-3   | 1    | 1-4     | 2        | 1-4-5   | INFINITO | -       |

| 3        | {1, 2, 4}          | 2    | 1-2     | 4    | 1-4-3   | 1    | 1-4     | 2        | 1-4-5   | INFINITO | -       |

| 4        | {1, 2, 4, 5}       | 2    | 1-2     | 3    | 1-4-5-3 | 1    | 1-4     | 2        | 1-4-5   | 4        | 1-4-5-6 |

| 5        | {1, 2, 3, 4, 5}    | 2    | 1-2     | 3    | 1-4-5-3 | 1    | 1-4     | 2        | 1-4-5   | 4        | 1-4-5-6 |

| 6        | {1, 2, 3, 4, 5, 6} | 2    | 1-2     | 3    | 1-4-5-3 | 1    | 1-4     | 2        | 1-4-5   | 4        | 1-4-5-6 |

Tabela 1 – Aplicação do algoritmo de Dijkstra no grafo da Figura 4. (Adaptado de Stallings (2007)).

Figura 11 – Evolução do algoritmo de Dijkstra no grafo da Figura 4. (Extraído de Stallings (2007)).

### 2.4.2 Algoritmo A\*

O algoritmo A\* (pronunciado A Estrela), proposto por (HART; NILSSON; RAPHAEL, 1968), pertence à categoria dos algoritmos informados, visto que utiliza informação adicional ou função heurística h(n) sobre o grafo durante sua análise. A informação adicional utilizada indica o custo estimado do caminho do nó atual para o destino, localizado na área do grafo ainda não explorada. Essa característica permite distinguir quais nós são mais promissores, viabilizando uma identificação mais eficiente da solução. Por esse motivo, o  $A^*$  é bastante eficaz na análise

de menor caminho entre dois nós específicos, sendo primariamente utilizado em robótica para análise em *grids* (SIEGWART; NOURBAKHSH; SCARAMUZZA, 2011).

Durante a execução do algoritmo, o custo até o destino (*custo-total*) é calculado para cada nó analisado, sendo composto pela soma do custo da fonte até o nó atual (*custo-aqui*) com o custo estimado até o destino (*custo-destino*).

O algoritmo é iniciado com uma lista de nós abertos contendo apenas o fonte, que possui *custo-aqui* igual a zero, e uma lista (vazia) com os nós fechados. Sua execução pode ser dividida em cinco etapas (KLANCAR *et al.*, 2017):

- 1. Seleção do primeiro nó da lista de nós abertos (nó atual). Essa lista é ordenada de forma crescente de acordo com o *custo-total*;

- 2. Para todos os nós que podem ser alcançados a partir do nó atual são calculados o *custo-destino*, o *custo-aqui* e o *custo-total*;

- 3. São armazenados os valores do *custo-aqui*, do custo da conexão com o nó atual, do *custo-destino* e do *custo-total* para os nós vizinhos que ainda não possuem esses valores. Os nós que já possuem valores armazenados tem seus valores atualizados quando menores valores forem encontrados;

- 4. Nós cujo valor foi calculado pela primeira vez são adicionados à lista dos nós abertos. Os nós que já se encontravam na lista aberta e foram atualizados são mantidos nesta lista. Os nós que estavam na lista de nós fechados e foram atualizados são movidos para a lista aberta. O nó atual é movido para a lista de nós fechados;

- Caso ainda existam nós na lista aberta, essa lista é ordenada e o passo 1 é novamente realizado. O algoritmo é finalizado quando o nó destino é adicionado à lista dos nós fechados.

O algoritmo A\* é completo e sempre encontra o caminho ótimo no grafo quando se utiliza uma função heurística ótima, que define o *custo-destino* como menor ou igual ao *custo-destino* real. Um dos pontos negativos desse método é o alto uso de memória (KLANCAR *et al.*, 2017).

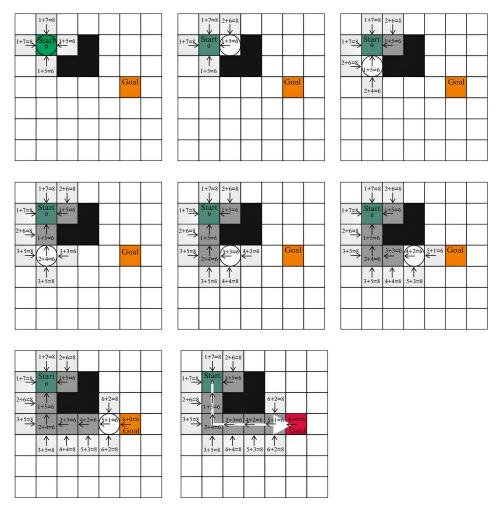

Na Figura 12, é exibido um exemplo da evolução do algoritmo A\*. O nó atual é marcado com um círculo, os nós inseridos na lista de nós abertos recebem a cor cinza, a lista fechada é marcado por cinza escuro e os obstáculos são marcados com preto. A direção do nó pai é definida por uma seta e cada nó visitado possui o custo do caminho. Na figura foi utilizada a distância Manhattan¹ como função de custo .

Distância entre dois pontos medidos ao longo de eixos em ângulos retos (BLACK, 1998)

Figura 12 – Evolução do algoritmo A\* (Extraído de Klancar et al. (2017)).

Uma peculiaridade é que se todos os *custos-destino* forem definidos como zero, o A\* funciona igual ao algoritmo Dijkstra. Na Figura 13 é mostrada uma comparação de desempenho entre os dois algoritmos. Na imagem é possível identificar que o algoritmo A\* apresenta uma melhor eficiência, pois para encontrar a menor distância entre dois nós, analisa uma quantidade menor de nós quando comparado ao algoritmo de Dijkstra. Por outro lado, devido à adoção de uma função heurística, sua utilização pode acaber sendo inviabilizada a depender da aplicação. Assim, seu uso é mais difundido em aplicações que utilizam grade, uma vez que nesse modelo o cálculo é simplificado quando comparado com aqueles que possuem uma estrutura mais heterogênea.

Figura 13 – Comparação do A\* (direita) com o Dijkstra (esquerda) (Extraído de Klancar *et al.* (2017)).

CAPÍTULO

3

## **REVISÃO DA LITERATURA**

Neste capítulo são apresentados os principais trabalhos relacionados com esta pesquisa, alguns dos quais contribuíram na construção da proposta e outros que surgiram como referencial teórico. Os trabalhos são agrupados por tema e suas relações com este estudo são também exploradas.

Inicialmente é apresentado o problema do planejamento de rotas com a utilização de PRM, demonstrando os resultados existentes, bem como pontos que podem ser melhorados. Por fim, são apresentados diversos estudos sobre otimização do cálculo do menor caminho.

## 3.1 Planejamento de rotas

Uma das atividades mais críticas e fundamentais na área de robótica é o planejamento de rotas. Apesar de atualmente existirem diversas formas de se resolver esse problema, a complexidade das soluções tende a aumentar conforme são incluídos mais graus de liberdade no robô. Atualmente, apesar de existirem robôs com alto nível de liberdade de movimento, muitas vezes não é possível empregar todo o seu potencial devido à limitação dos algoritmos utilizados (LIU *et al.*, 2021).

A utilização de técnicas de paralelismo para melhorar o desempenho nesse tipo de aplicação já se mostrou acertada, como demonstrado, por exemplo, em (CABODI *et al.*, 2019) - uma abordagem paralela para resolver RRT em problemas de tempo real.

Trabalhos como (LIU et al., 2023) aplicam uma variante da técnica RRT\* que adiciona uma operação de religação (do inglês rewiring) para melhorar a qualidade das soluções alcançadas. Além disso, eles usam técnicas de compressão de dados para reduzir o impacto das transferências de informações em uma plataforma heterogênea de CPU/GPU. No entanto, apesar dos resultados favoráveis, como seu tempo de processamento é da ordem de segundos, eles não são adequados para aplicações em tempo real.

Em (HORTELANO *et al.*, 2023), a utilização de GPU produz uma notável aceleração de 5× em média em comparação com implementações C++ brutas para cálculos de previsão de movimento. Além disso, para robôs com mais de seis graus de liberdade, muitas soluções que oferecem tempos de resposta na ordem de centenas de milissegundos são implementadas em GPUs, como mostrado por (PAN; MANOCHA, 2012) e (PAN; LAUTERBACH; MANOCHA, 2010).

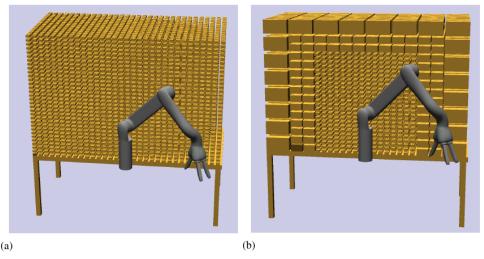

Como alternativa, a utilização de um FPGA já foi explorada assertivamente em alguns trabalhos como em (ATAY; BAYAZIT, 2006), onde se constrói um planejador de rotas e detector de colisões em FPGA com resultado 25 vezes mais rápido do que o obtido em uma CPU.

Em (MURRAY et al., 2016a) e em (MURRAY et al., 2016b) é apresentada uma proposta de solução para o problema de planejamento de caminhos também com a utilização de um hardware dedicado como o FPGA. A técnica utilizada é aplicada em um robô Kinova Jaco2. Esses trabalhos exibiram uma melhora no desempenho em três ordens de magnitude e redução do consumo de energia em mais de uma ordem quando comparado com outras pesquisas, assim apresentando valores promissores, ao se considerar que, além de reduzir significativamente o tempo de resposta, também alcançam uma redução do consumo de energia. Esse último é um aspecto crítico quando se consideram aplicações que utilizam robôs autônomos alimentados por baterias.

Para alcançar esse ganho, foram empregadas diversas técnicas de otimização, como a utilização de uma discretização não uniforme do ambiente, aplicando maior resolução em áreas que necessitam maior precisão (ver Figura 14). Essa estratégia reduziu em 27% o uso de espaço no FPGA. Também foram utilizadas ferramentas adicionais para minimizar a lógica a ser sintetizada, fazendo uma análise prévia à síntese com a ferramenta *espresso*, o que possibilitou reduzir a lógica necessária em 25%.

Figura 14 – a) Discretização uniforme. b) Abordagem mais sofisticada ao aplicar uma maior resolução em regiões mais críticas. (Adaptado de Murray *et al.* (2016a)).

Os autores utilizaram a construção de um PRM como base para o desenvolvimento da

solução. Trabalhos recentes como (SAKAMOTO; HARADA; WAN, 2020) e (FRANCIS et al., 2020) confirmaram as vantagens da utilização de PRMs na redução do tempo de processamento necessário para o planejamento de rotas. Na etapa de pré-processamento do PRM, realizada apenas uma vez, o *rodmap* é construído considerando apenas as colisões permanentes no ambiente e as auto-colisões do robô. Sequencialmente, o espaço de configuração é discretizado e conjuntos dos vértices que colidem com cada arco são identificados e armazenados. Por fim, as arestas são representadas como circuitos lógicos sintetizáveis.

A fase de consulta, realizada a cada novo planejamento, utiliza os dados coletados dos sensores para popular uma grade de ocupação, utilizando o mesmo nível de discretização em que o mapa de navegação foi construído. As colisões são encontradas ao analisarem-se os vértices presentes na grade de ocupação, e então, o mapa de navegação é atualizado. Por fim, com um novo mapa de navegação, o algoritmo de menor caminho é aplicado e, caso exista, uma rota livre de obstáculos a ser utilizada pelo robô é gerada.

Como resultado, o processo de construção do mapa de navegação e de obtenção do menor caminho com a utilização de FPGAs, utilizando um *clock* com frequência de 125 MHz, pôde ser realizado em 650 microssegundos. No entanto, apesar de uma melhora significativa de desempenho no processo de criação do *rodmap*, o resultado final foi comprometido pelo algoritmo de menor caminho. Desse modo, dos 650 microssegundos totais necessários ao processamento, 425 eram utilizados apenas pelo algoritmo de menor caminho. Além disso, por não ter sido implementado em FPGA, o resultado do PRM precisa ser exportado e processado na CPU. Essa necessidade, além de acrescentar um custo de comunicação, também promove uma redução de eficiência, pois não utiliza um hardware especializado no cálculo do menor caminho.

O resultado comparativo de desempenho desse trabalho pode ser visualizado na Tabela 2, onde se encontram: a abordagem em FPGA, apresentando um tempo de processamento de 650 microssegundos; os resultados de uma técnica que se utiliza de conjuntos *hash* pré-computados em Unidade Central de Processamento (do inglês *Central Processing Unit*) (CPU) e GPU com 10.000 e 1.600 microssegundos, respectivamente; e, por fim, os resultados de uma implementação em CPU com a utilização de PRM e RRT, apresentando 815.000 e 756.000 microssegundos, respectivamente.

Tabela 2 – Tempo necessário em microssegundos para o planejamento de movimento em diferentes abordagens. (Adaptado de Murray *et al.* (2016a)).

| Hardware Dedicado | Conjun | tos Hash Pré computados | Abordagem via Software(CPU) |         |  |

|-------------------|--------|-------------------------|-----------------------------|---------|--|

| FPGA              | CPU    | GPU                     | PRM                         | RRT     |  |

| 650               | 10.000 | 1.600                   | 815.000                     | 756.000 |  |

Os principais trabalhos citados nesta seção, juntamente com suas contribuições, podem ser vistos na Tabela 3.

| Técnica                      | Referência                              | Vantagens                                   | Tipo de Hardware |  |

|------------------------------|-----------------------------------------|---------------------------------------------|------------------|--|

| DDT-                         | (CARODI - 1 2010)                       | Permite soluções otimizadas                 | CDU              |  |

| RRT* em paralelo             | (CABODI et al., 2019)                   | para problemas computacionalmente complexos | CPU              |  |

|                              |                                         | Melhora a qualidade da solução e reduz      |                  |  |

| RRT* com Rewiring            | (LIU et al., 2023)                      | a sobrecarga de transferência de dados      | CPU/GPU          |  |

| 1411 2011116111118           | (====================================== | (até 10 vezes                               |                  |  |

|                              |                                         | sobre o algoritmo RRT*)                     |                  |  |

| Previsão de movimento        | (HORTELANO et al., 2023)                | Aceleração de 5 vezes em comparação         | GPU              |  |

| com aceleração em GPU        | (HORTEEL HVO et al., 2023)              | com implementações em C++                   | GI C             |  |

| Previsão de movimento        | (PAN; MANOCHA, 2012)                    | Tempo de resposta em milissegundos          | GPU              |  |

| para robôs com alto DoF      | (FAIN, MANOCHA, 2012)                   | Tempo de resposta em minissegundos          | GPU              |  |

| Planejamento de rota e       |                                         | Atimas valosidada 25v mais rémida           |                  |  |

| detecção de colisão baseados | (ATAY; BAYAZIT, 2006)                   | Atinge velocidade 25x mais rápida           | FPGA             |  |

| em FPGA                      |                                         | em comparação com a CPU                     |                  |  |

| Planejamento de caminho      | (MIIDDAY et al. 2016a)                  | Oferece desempenho significativo            | FPGA             |  |

| baseado em PRM com FPGA      | (MURRAY <i>et al.</i> , 2016a)          | (melhoria de 3 ordens de magnitude)         | ITUA             |  |

Tabela 3 – Comparação dos trabalhos relacionados.

#### 3.2 Otimização do cálculo do menor caminho

A evolução da capacidade de processamento nos diversos dispositivos envolvidos na movimentação do robô, viabilizou uma melhora significativa das suas aplicabilidades nos últimos anos. Do mesmo modo, por ser um método crucial na atividade de planejamento de rotas, a identificação do menor caminho também precisou evoluir, se adequando às novas necessidades para que resultados melhores pudessem ser obtidos.

Na área de algoritmos e processamento de dados, o problema do menor caminho é um dos mais antigos e fundamentais. Com o surgimento de novos ramos da tecnologia, como a robótica, sua aplicabilidade aumentou ainda mais e novos estudos passaram a ser desenvolvidos. Dentre as soluções utilizadas para a resolução desse problema, a que mais se destaca é o algoritmo de Dijkstra. Sua característica de sempre encontrar o menor caminho ótimo, quando houver, fez com que essa técnica pudesse ser explorada por décadas. Com o passar dos anos, diversas implementações e técnicas de paralelismo foram desenvolvidas com o intuito de aprimorar seu desempenho.

Como apresentado na seção 3.1, alguns estudos, apesar de apresentarem resultados promissores, poderiam obter resultados ainda melhores, caso optassem por melhores técnicas de cálculo de menor caminho. Nesse contexto, a solução adequada para o menor caminho deveria apresentar, além de uma melhora de desempenho, uma adaptação dinâmica à mudança no grafo a ser analisado, uma vez que arestas podem ser inseridas ou excluídas de modo temporalmente aleatório conforme as mudanças no ambiente.

Desse modo, ficou evidente a necessidade de uma nova abordagem para o tratamento do menor caminho, levando em conta essas condições especiais, permitindo assim atender demandas semelhantes que possam surgir em contextos diferentes. Assim, foi realizado um estudo sobre o estado da arte desse tipo de algoritmo, priorizando o desempenho e as possibilidades de exploração de paralelismo.

Por ser um método bastante utilizado, existem diversos trabalhos que buscam melhorar o desempenho desse tipo de algoritmo. Trabalhos recentes, como (PRASAD; KRISHNAMURTHY; KIM, 2018), propõem soluções de melhoria com a utilização de CPUs. Nesse caso, foi possível atingir um desempenho de até 51% utilizando uma estratégia com multiprocessadores para um grafo com 10<sup>8</sup> nós.

Em (JASIKA *et al.*, 2012) é exposto um estudo sobre os ganhos na paralelização do algoritmo base de Dijkstra com a utilização de *Open Multi-Processing* (OpenMP) e *Open Computing Language* (OpenCL) aplicados a CPUs. Apesar de resultados melhores na alternativa paralelizada, o estudo utiliza a estrutura base do algoritmo que, por ser essencialmente sequencial, prejudica o desempenho da paralelização, Na média, os testes obtiveram uma melhora de 10% no desempenho.

Existem também estudos que exploram a natureza paralela das placas gráficas, como (THOUTI; SATHE, 2013). A partir dos trabalhos realizados por (HARISH; NARAYANAN, 2007) e (BULUÇ; GILBERT; BUDAK, 2010), em que técnicas de busca do menor caminho são exploradas, (THOUTI; SATHE, 2013) desenvolveu uma solução para GPU utilizando *Message Passing Interface* (MPI) e OpenCL. Essa solução obteve um ganho de desempenho entre 10 e 15 vezes quando comparada aos resultados obtidos de modo sequencial em CPU.

Há também trabalhos que realizam otimizações com a utilização de hardware dedicado, como os FPGAs. Em (TOMMISKA; SKYTTÄ, 2001), por exemplo, foi desenvolvida uma solução em FPGA que apresentou para uma aplicação com 64 nós, um desempenho 67 vezes melhor (aproximadamente) do que a versão em processadores.

Uma arquitetura dedicada em FPGA para resolver o problema de construção de tabela de roteamento em redes *Open Shortest Path First* (OSPF) foi proposta por (ABDUL; ALWAN; AL-EBADI, 2012). O estudo obtém uma melhoria de desempenho de até 76x em relação à implementação padrão do Dijkstra em uma CPU para um grafo com 128 nós. No entanto, a complexidade da arquitetura limitou a solução para até 128 nós no dispositivo escolhido.

O trabalho conduzido por (CHIRILA *et al.*, 2022) introduz uma técnica de algoritmo híbrido - de acordo com (BADR; MOUSSA, 2020), um algoritmo  $O(n^3)$  - projetado especificamente para abordar problemas de menor caminho entre todos os pares (do inglês *All-Pairs Shortest Path*) (APSP) em grafos com mais de 4.096 nós. O estudo apresenta resultados favoráveis quando comparado a soluções similares. Contudo, é importante notar que o problema APSP acarreta maior complexidade comparado ao problema SSSP. Isto indica que um projeto dedicado exclusivamente ao problema SSSP pode potencialmente alcançar ganhos e otimizações ainda maiores.

Como demonstrado, o algoritmo de Dijkstra vem sendo constantemente testado e aprimorado. Nas seções a seguir, serão expostas quatro técnicas diferentes encontradas na literatura que possibilitam, com suas peculiaridades, um ganho de desempenho na análise do menor

caminho. As técnicas que serão apresentadas contribuíram para um melhor entendimento das possibilidades de melhoria existentes, bem como das suas limitações. Os conhecimentos aqui levantados, como será possível observar nos próximos capítulos, formaram o alicerce para a construção de uma nova proposta de solução.

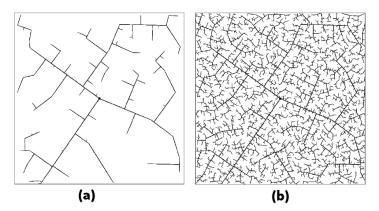

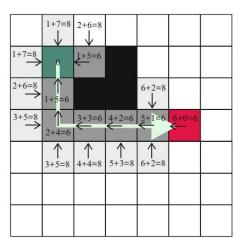

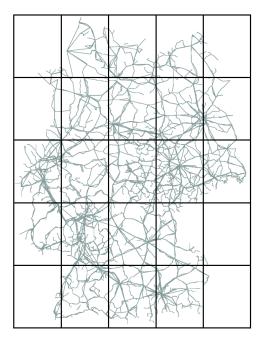

#### 3.2.1 Particionamento do Grafo

Uma solução para viabilizar o paralelismo através do particionamento do grafo é apresentada por (SCHÜTZ, 2005) (Ver Figura 15). O autor explora a característica estática do grafo ao realizar um pré-processamento visando a aceleração da análise. Essa técnica pode ser utilizada em grafos estáticos devido ao pré-processamento *offline* necessário. O método consegue identificar e ignorar arestas que não levam ao nó destino, reduzindo a quantidade de nós visitados para menos de 0,2%. Para realizar isso, divide os nós do grafo em regiões e, durante o pré-processamento, identifica as regiões que compõem o menor caminho.

Figura 15 – Um grid 5x5 das estradas da Alemanha (Extraído de Schütz (2005)).

O autor destaca que podem ocorrer problemas quando se combinam técnicas de otimização em grafos com mais de um menor caminho e sugere, como alternativa para eliminar esse problema, a inclusão de valores fracionários pequenos aos pesos do grafo. Ele aborda também a utilização de filas de Fibonacci para a lista de prioridade dos algoritmos de Dijkstra, pois elas apresentam um pior caso de  $O(m + n \log n)$ , sendo m o número de bordas e n o número de nós.

Vale destacar que um sub-caminho de um menor caminho também é um menor caminho, ou seja: se  $s-n_1-...-n_k-t$  é o menor caminho de s a t então  $n_i-...-n_k-t$  é o menor caminho de  $n_i$  até t. Então, ao calcular o menor caminho entre todos os pares de nós é possível identificar quais nós fazem parte do menor caminho até o destino. Com o objetivo de reduzir o

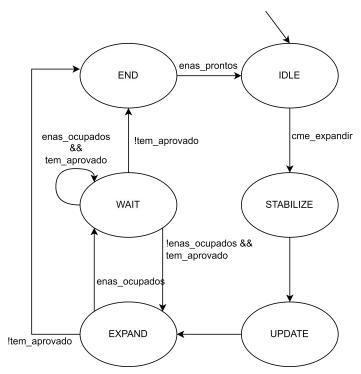

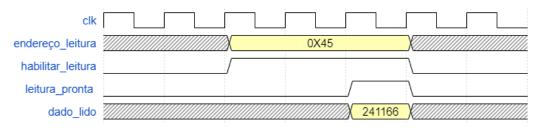

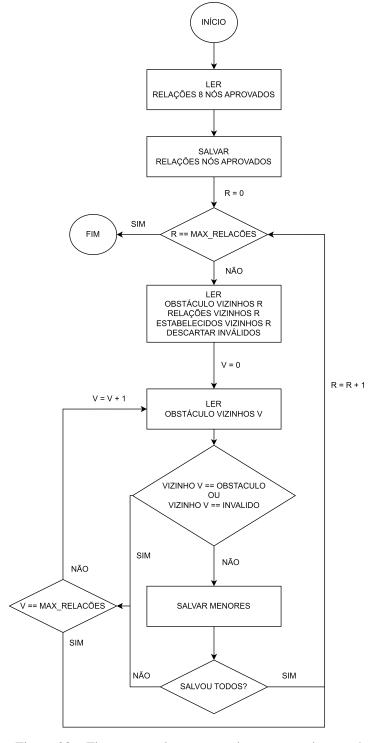

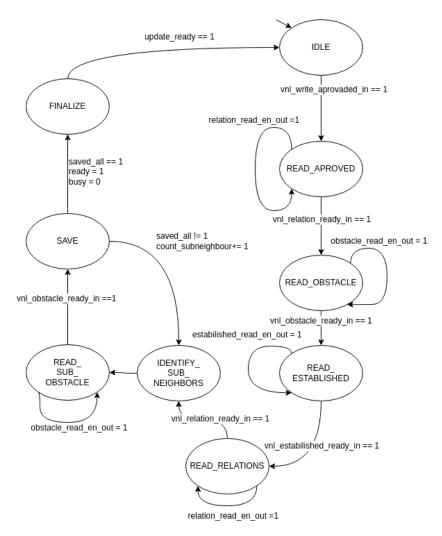

custo computacional dessa operação, utiliza-se uma técnica de particionamento do grafo, a qual possibilita a identificação dos nós que não fazem parte do menor caminho até o destino. Essa técnica consiste em dividir o grafo em partições e, com o auxílio de um vetor de bits, mapear, para cada nó, em quais regiões esse nó possui um menor caminho até o destino.