## SERVIÇO PÚBLICO FEDERAL MINISTÉRIO DA EDUCAÇÃO UNIVERSIDADE FEDERAL DA BAHIA ESCOLA POLITÉCNICA DA UFBA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Volker Kible

## SOFTWARE-DEFINED RF REFLECTION COEFFICIENT MEASUREMENT BLOCK BASED ON UNDER-SAMPLING DOWN-CONVERSION

## Universidade Federal da Bahia Departamento de Engenharia Elétrica Programa de Pós-Graduação em Engenharia Elétrica

### SOFTWARE-DEFINED RF REFLECTION COEFFICIENT MEASUREMENT BLOCK BASED ON UNDER-SAMPLING DOWN-CONVERSION

#### Volker Kible

TESE SUBMETIDA AO

PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

DA UNIVERSIDADE FEDERAL DA BAHIA

COMO PARTE DOS REQUISITOS NECESSÁRIOS

PARA OBTENÇÃO DO GRAU DE

DOUTOR EM ENGENHARIA ELÉTRICA.

Área de Concentração: Processamento de Sinais Linha de Pesquisa: Microeletrônica em RF

Orientador: Prof. Dr. Robson Nunes de Lima – UFBA

> Salvador, Bahia, Brasil Maio de 2021

#### K46 Kible, Volker

Software-defined RF reflection coefficient measurement block based on under-sampling down-conversion / Volker Kible. – Salvador, 2021.

123 p.: il. color.

Orientador: Prof. Dr. Robson Nunes de Lima.

Tese (doutorado) – Universidade Federal da Bahia. Escola Politécnica, 2021.

1. Coeficiente de reflexão. 2. Refletômetro. 3. Algoritmos. I. Lima, Robson Nunes de. II. Universidade Federal da Bahia. III. Título.

CDD: 511.5

# SOFTWARE-DEFINED RF REFLECTION COEFFICIENT MEASUREMENT BLOCK BASED ON UNDER-SAMPLING DOWN-CONVERSION

#### Volker Kible

Tese de Doutorado aprovada em 25 de junho de 2021 pela banca examinadora composta pelos seguintes membros:

| Roba | ou Nuier de Lima                                                           |

|------|----------------------------------------------------------------------------|

|      | Prof. Dr. Robson Nunes de Lima<br>Orientador e Presidente da Sessão – UFBA |

|      |                                                                            |

|      | Marican O. Percira                                                         |

|      | Prof. Dr. Maicon Deivid Pereira                                            |

|      | Membro Interno – UFBA                                                      |

|      |                                                                            |

|      |                                                                            |

|      | 0 / / 7                                                                    |

|      | Bereste hite                                                               |

|      | Prof. Dr. Bernardo Rego Barros de Almeida Leite                            |

|      | Membro Externo – UFPR                                                      |

|      | Memoro Externo OTTR                                                        |

|      |                                                                            |

|      |                                                                            |

|      | T/Q = CQ                                                                   |

|      | Farico Jerommo Smoes Sla<br>Prof. Dr. Fabrício Gerônimo Simões Silva       |

|      | Prof. Dr. Fábrício Gerônimo Simões Silva                                   |

|      | Membro Externo – IFBA                                                      |

|      |                                                                            |

|      |                                                                            |

Prof. Dr. Paulo Márcio Moreira e Silva Membro Externo – UNIFEI

## **Table of Contents**

| 1 | Introd | luction                                                           | 15 |

|---|--------|-------------------------------------------------------------------|----|

|   | 1.1 T  | neme and Justification                                            | 15 |

|   | 1.1.1  | Objectives                                                        | 17 |

|   | 1.2 Te | ext organization                                                  | 18 |

| 2 | Litera | ture Research and Theoretic Foundation                            | 19 |

|   | 2.1 Re | eflection Coefficient Measurement Techniques                      | 19 |

|   | 2.1.1  | Polar Approach                                                    | 19 |

|   | 2.1.2  | Cartesian Approach                                                | 20 |

|   | 2.1.3  | Superhet Cartesian Approach                                       | 20 |

|   | 2.1.4  | New Software Defined Approach proposed in this Thesis             | 21 |

|   | 2.2 D  | rectional Couplers                                                | 21 |

|   | 2.2.1  | Lumped Inductors and Capacitors                                   | 22 |

|   | 2.2.2  | Coupled Inductors (Transformers) and Capacitors                   | 22 |

|   | 2.2.3  | Two Transformer Approach                                          | 22 |

|   | 2.3 In | jection Locking Frequency Dividers and their Digital Counterparts | 23 |

|   | 2.3.1  | Injection Locking Frequency Dividers                              | 23 |

|   | 2.3.2  | D Type Flip-Flop as Frequency Divider                             | 23 |

|   | 2.3.3  | Digital Counters                                                  | 24 |

|   | 2.4 Pl | nase-Locked Loop for Frequency Synthesis                          | 24 |

|   | 2.4.1  | Integer-N                                                         | 24 |

|   | 2.4.2  | Fractional-N                                                      | 25 |

|   | 2.4.3  | Loop Analysis                                                     | 25 |

|   | 2.5 A  | nalog-to-Digital Converter (ADC)                                  | 27 |

|   | 2.5.1  | The Quantizer                                                     | 27 |

|   | 2.5.2  | The sample and hold (S&H) or track and hold (T&H) block           | 29 |

|   | 2.6 U  | nder-Sampling Down-Conversion                                     | 29 |

|   | 2.6.1  | Sampling Effects: Aliasing                                        | 29 |

|   | 2.6.2  | Under-Sampling                                                    | 30 |

|   | 2.6.3  | Under-Sampling Down-Conversion                                    | 31 |

|   | 2.7 Fa | st Fourier Transform (FFT)                                        | 31 |

|   | 2.7.1  | Frequency Bins                                                    | 32 |

|   | 2.7.2  | Radix-2, Radix-4, Radix-8                                         | 32 |

| 3 | Princi | ple of Operation                                                  | 33 |

|   | 3.1 Sy | rstem Block Diagram                                               | 33 |

|   | 3.2 D  | rectional Coupler                                                 | 34 |

|   | 3.3 Pı | e-Divider Block                                                   | 34 |

|   | 3.4 In | teger-N PLL Frequency Synthesizer                                 | 35 |

|   | 3.4 | 4.1   | Calculation of Good PLL Counter Values                               | 37 |

|---|-----|-------|----------------------------------------------------------------------|----|

|   | 3.4 | 4.2   | Loop Filter                                                          | 39 |

|   | 3.5 | Fas   | st Analog-to-Digital Converter (ADC)                                 | 40 |

|   | 3.6 | Sys   | tem Processor                                                        | 41 |

|   | 3.7 | Mie   | crocontroller Software                                               | 42 |

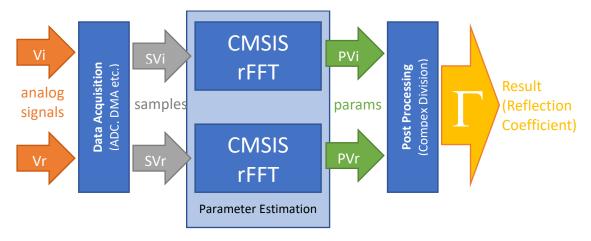

|   | 3.7 | 7.1   | Real Fast-Fourier Transform                                          | 42 |

|   | 3.7 | 7.2   | Reflection Coefficient Calculation                                   | 43 |

|   | 3.8 | Pei   | rsonal Computer software                                             | 43 |

| 4 | Sir | mula  | tions                                                                | 45 |

|   | 4.1 | Tes   | st of Sensitivity of FFT to Frequency Variation                      | 45 |

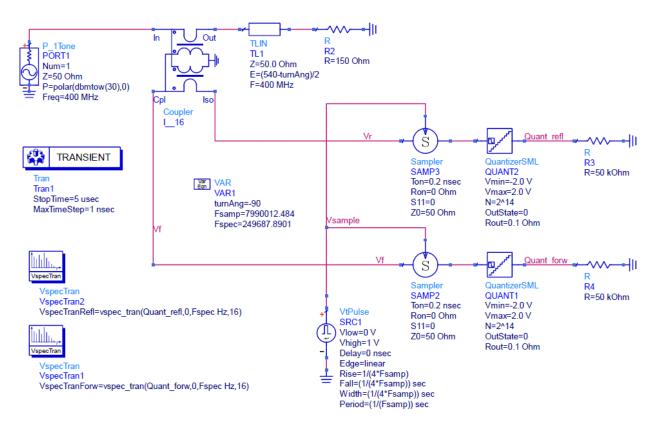

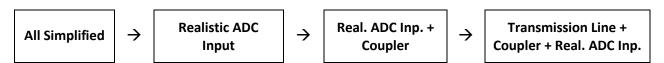

|   | 4.2 | Cha   | aracterization of a Simplified Model of the System using ADSADD      | 47 |

|   | 4.2 | 2.1   | Statistics over ADS Simulation Results                               | 49 |

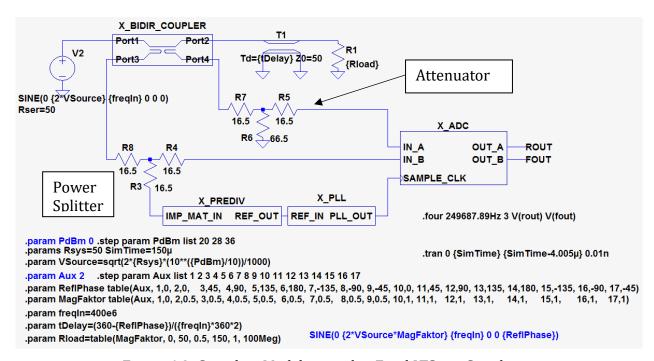

|   | 4.3 | Cha   | aracterization of a More Complete Model using LTSpice                | 50 |

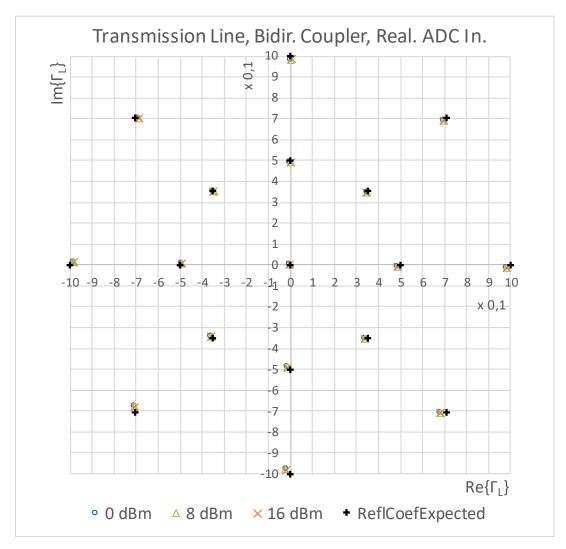

|   | 4.3 | 3.1   | Statistics over LTSpice Simulation Results                           | 56 |

|   | 4.3 | 3.2   | Simulations with Random Noise                                        | 57 |

|   | 4.4 | Co    | nclusion of Simulations                                              | 60 |

| 5 | De  | esign | and Implementation                                                   | 61 |

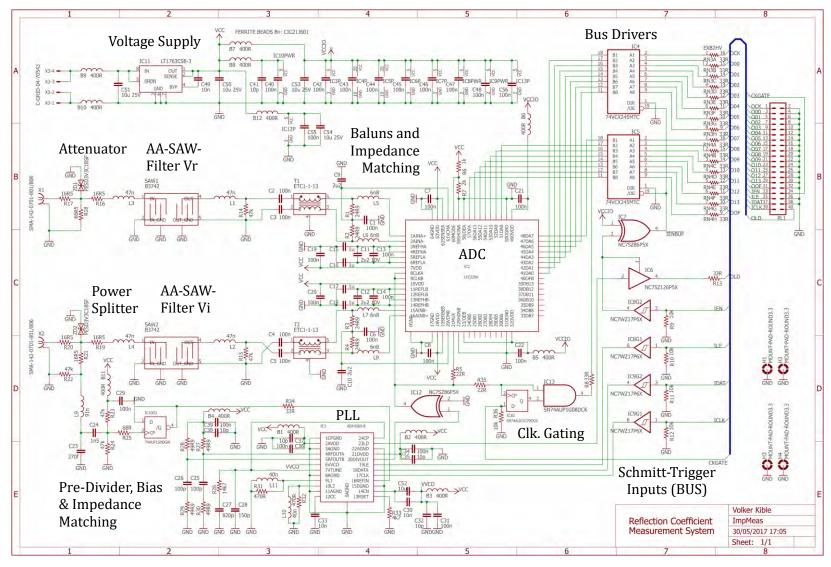

|   | 5.1 | Ele   | ectronics                                                            | 61 |

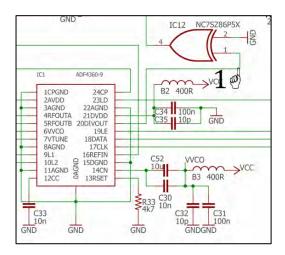

|   | 5.1 | 1.1   | Schematic                                                            | 61 |

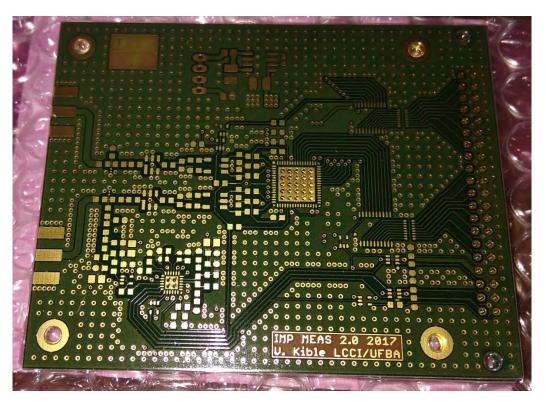

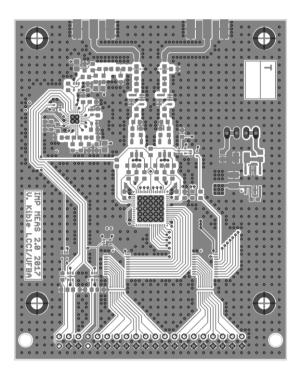

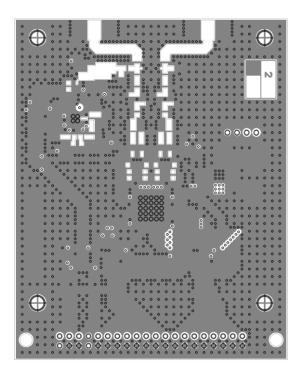

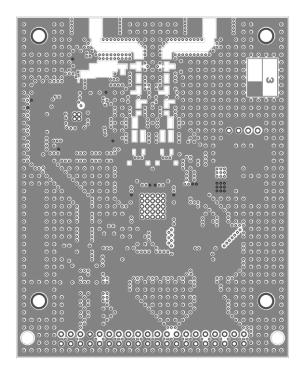

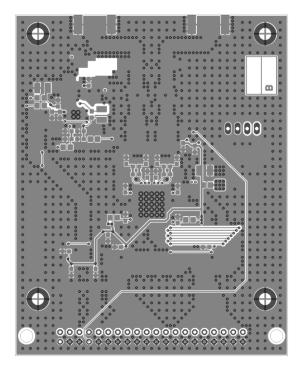

|   | 5.1 | 1.2   | Printed Circuit Board Layout                                         | 66 |

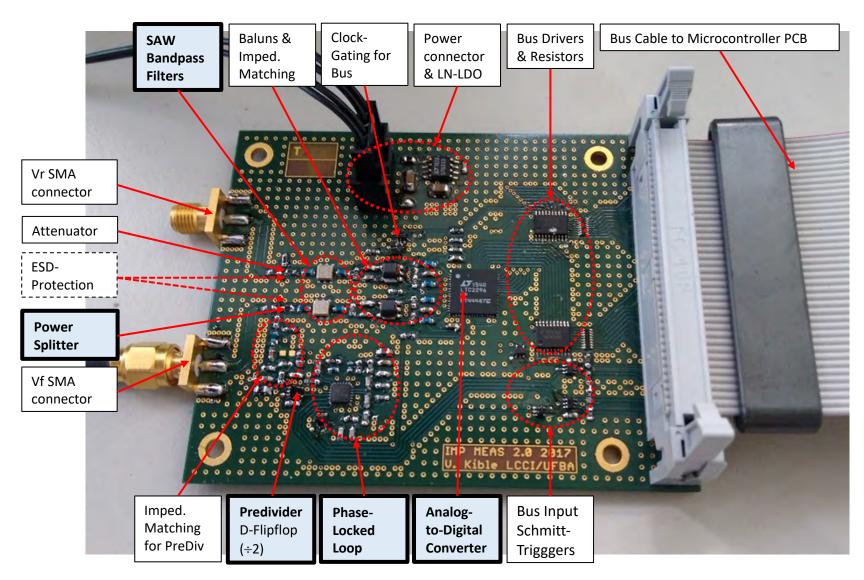

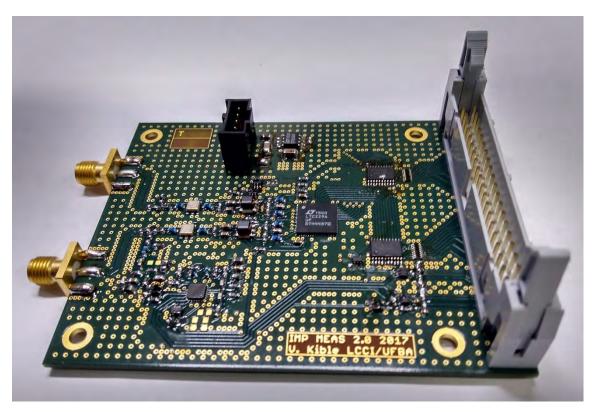

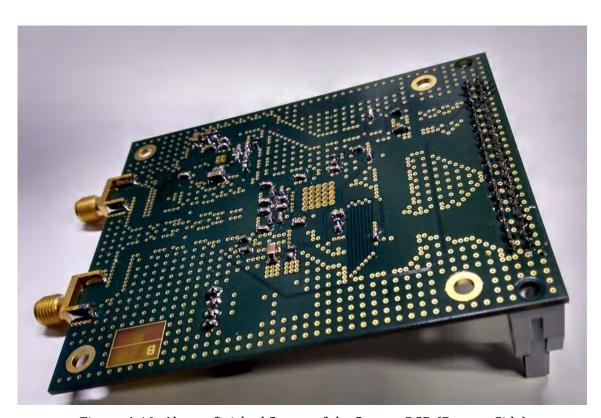

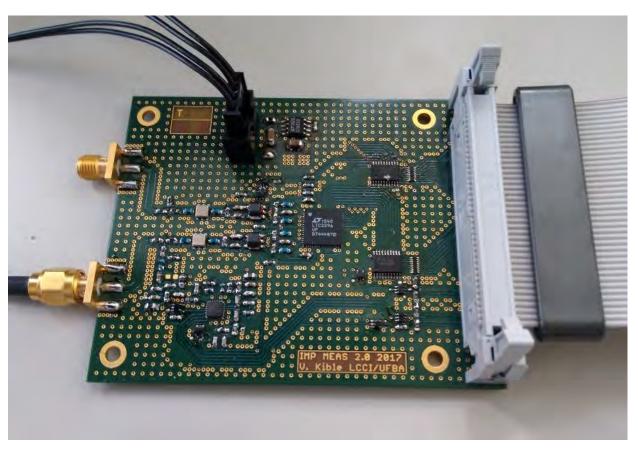

|   | 5.1 | 1.3   | Populated Board                                                      | 69 |

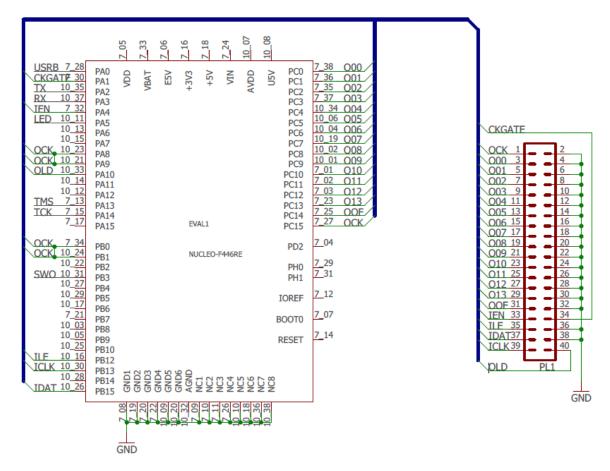

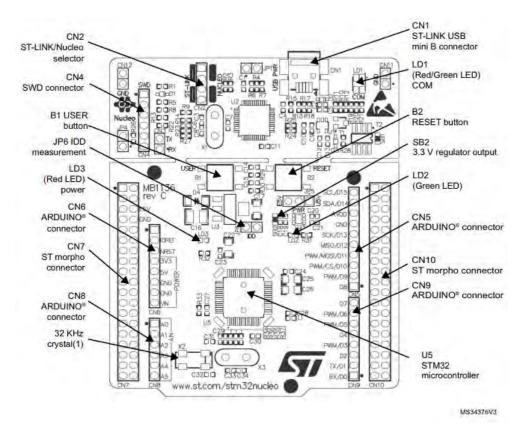

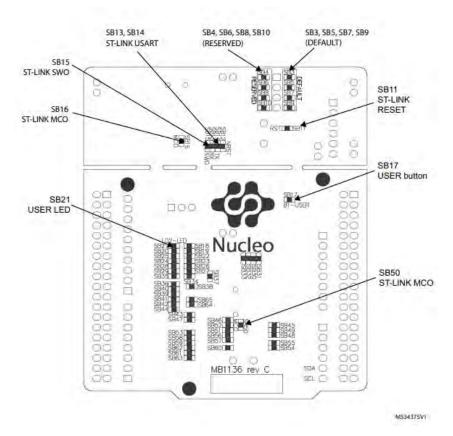

|   | 5.1 | 1.4   | Modification of the Microcontroller Board                            | 71 |

|   | 5.2 | Sof   | tware                                                                | 72 |

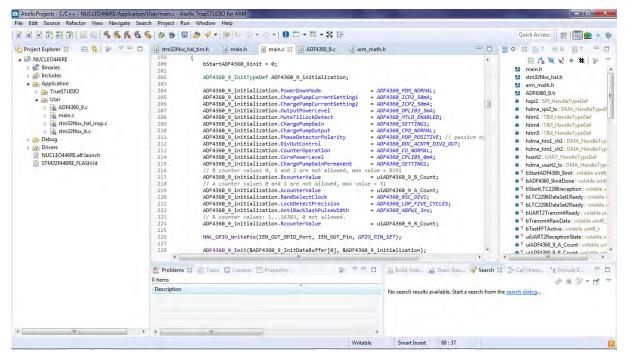

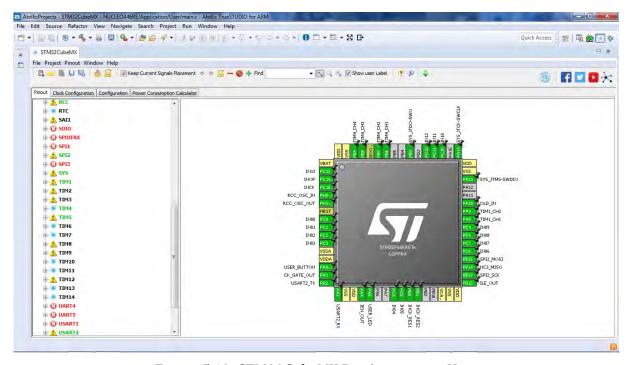

|   | 5.2 | 2.1   | Microcontroller Software                                             | 73 |

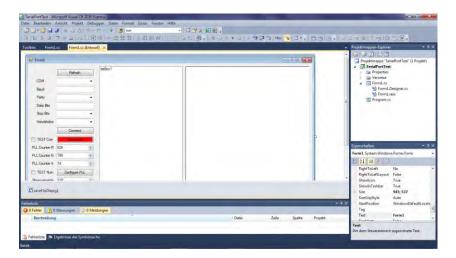

|   | 5.2 | 2.2   | Personal Computer Software                                           | 80 |

| 6 | Ch  | ıarac | terization                                                           | 85 |

|   | 6.1 | Tes   | st of PLL and output Frequency                                       | 85 |

|   | 6.1 | 1.1   | Test Setup                                                           | 85 |

|   | 6.1 | 1.2   | Test Execution                                                       | 86 |

|   | 6.1 | 1.3   | Test Results                                                         |    |

|   | 6.2 | Tes   | st of Forward Channel of ADC and Measurement Chain                   |    |

|   | 6.2 | 2.1   | Test Execution                                                       |    |

|   | 6.2 |       | Test Results                                                         |    |

|   | 6.3 | Me    | asurements with known Impedances                                     | 87 |

|   | 6.3 | 3.1   | Measurement Setup                                                    |    |

|   | 6.3 | 3.2   | Measurement Results                                                  |    |

|   | 6.3 |       | Analysis and Discussion                                              |    |

| 7 | Op  |       | zed Algorithm for UHF Software Defined Reflectometer                 |    |

|   | 7.1 | Im    | plementation and Selection of Algorithms for Optical Ranging Sensors | 93 |

|    | 7.1.1     | Implemented Algorithms            | 94  |

|----|-----------|-----------------------------------|-----|

|    | 7.1.2     | Test Scheme                       | 94  |

|    | 7.1.3     | Results                           | 95  |

| 8  | Founda    | ation for Closing the Loop        | 97  |

|    | 8.1 Va    | riable Impedance Matching Network | 97  |

|    | 8.2 Co    | mplex Control Algorithm Theory    | 97  |

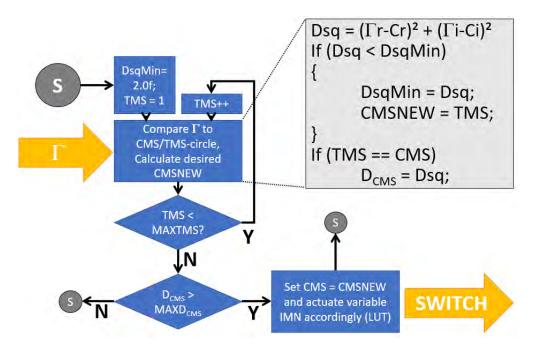

|    | 8.2.1     | Previous Algorithm                | 97  |

|    | 8.2.2     | Proposed Solution                 | 98  |

| 9  | Conclu    | sion                              | 101 |

| Re | ferences. |                                   | 103 |

| A  | Appen     | dix                               | 111 |

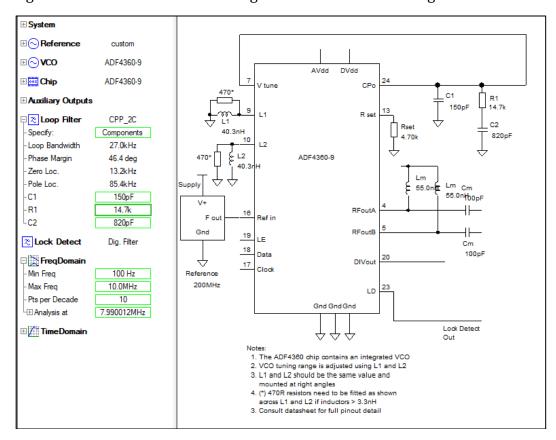

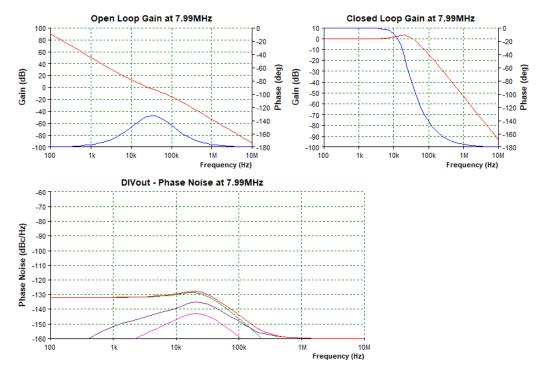

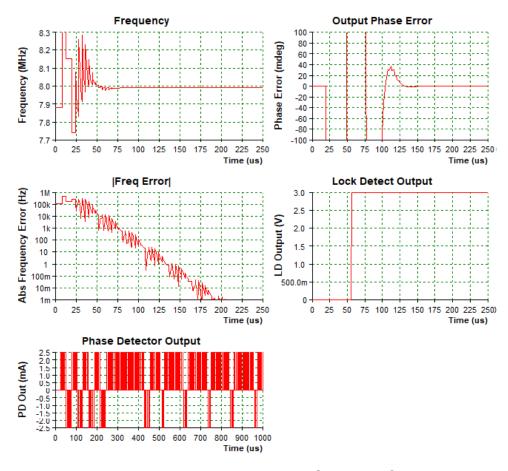

|    | A.1 AD    | IsimPLL Outputs for ADF4360-9     | 111 |

|    | A.1.1     | Schematic                         | 111 |

|    | A.1.2     | Simulation Results                | 111 |

|    | A.2 As:   | sembly Documentation              | 115 |

|    | A.2.1     | Case                              | 115 |

|    | A.2.2     | Power Supply                      | 115 |

|    | A.2.3     | Integrated Circuits               | 116 |

|    | A.2.4     | Remaining SMD and THT Components  | 117 |

|    | A.2.5     | Conclusion of Assembly            | 118 |

|    | A.3 Ma    | tlab Script for SOL Correction    | 121 |

|    | A.4 Pu    | blications                        |     |

|    | A.4.1     | As Author                         | 123 |

|    | A.4.2     | As Co-Author                      | 123 |

## **List of Figures**

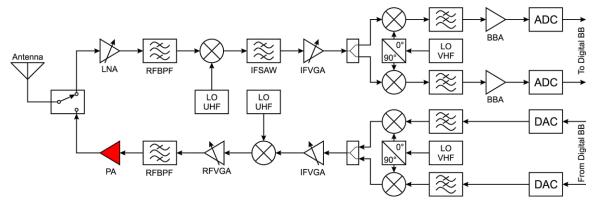

| Figure 1.1: A Typical Digital Transceiver (Superheterodyne)                        | 16 |

|------------------------------------------------------------------------------------|----|

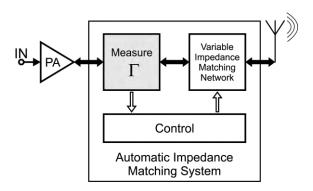

| Figure 1.2: An Automatic Impedance Matching System                                 | 16 |

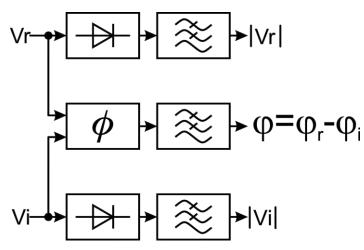

| Figure 2.1: Polar Approach                                                         | 19 |

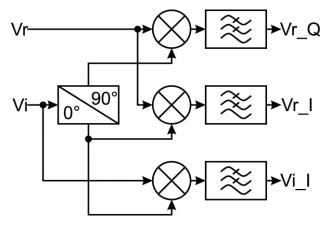

| Figure 2.2: Cartesian Approach                                                     |    |

| Figure 2.3: Directional Coupler using Coupled Inductors and Capacitors [25]        | 22 |

| Figure 2.4: Directional Coupler using two Transformers                             | 22 |

| Figure 2.5: Divide-by-3 Injection Locking Frequency Divider                        | 23 |

| Figure 2.6: Integer-N PLL Frequency Synthesizer                                    | 25 |

| Figure 2.7: Common loop filter topology                                            | 25 |

| Figure 2.8: Aliasing for Under-Sampling                                            | 30 |

| Figure 2.9: Under-Sampled Signals with Different PhasePhase                        | 31 |

| Figure 3.1: System Block Diagram                                                   | 33 |

| Figure 3.2: Impedance Matching & Bias Circuit before Pre-Divider                   | 35 |

| Figure 3.3: ADF4360-9 Functional Block Diagram [38][38]                            | 36 |

| Figure 3.4: Diagram of VCO sensitivity from [38]                                   | 39 |

| Figure 3.5: Functional Block Diagram LTC2296C (1 channel of 2) [39]                | 40 |

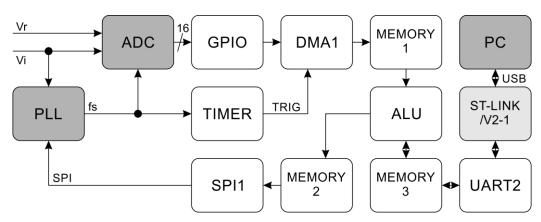

| Figure 3.6: Involved microcontroller modules (white) and connected hardware (grey) | 42 |

| Figure 4.1: Model for the simplified ADS simulations of the whole system           | 48 |

| Figure 4.2: Model of Pre-Divider including Input Impedance Matching                | 50 |

| Figure 4.3: Model of the PLL (Adjusted to Calculated Values)                       |    |

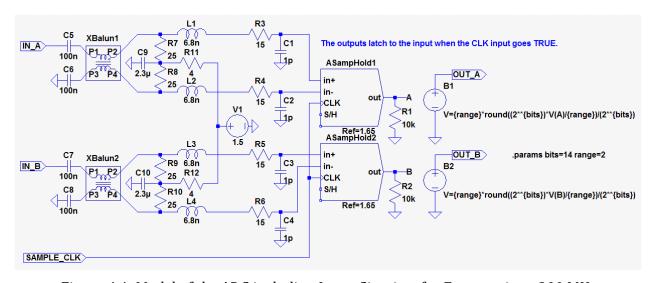

| Figure 4.4: Model of the ADC including Input Circuitry for Frequencies > 300 MHz   | 51 |

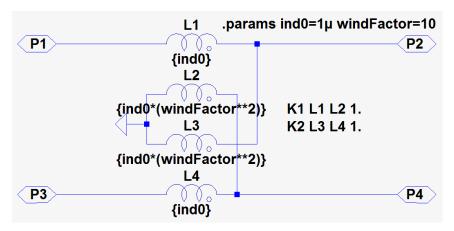

| Figure 4.5: Model of single Directional Coupler for Bidirectional Coupler Model    |    |

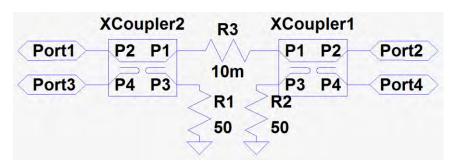

| Figure 4.6: The Bidirectional Coupler Model built using two single Couplers        |    |

| Figure 4.7: Flow-Chart of Simulation Configurations                                |    |

| Figure 4.8: Complete Model as used in Final LTSpice Simulation                     |    |

| Figure 4.9: Simulation Results of Complete System using LTSpice                    |    |

| Figure 5.1: Schematic of Measurement System                                        |    |

| Figure 5.2: Schematic of NUCLEO-Adapter                                            |    |

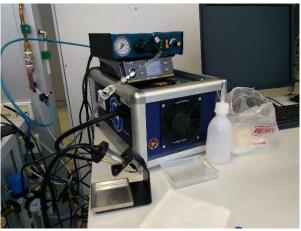

| Figure 5.3: Photo of System PCB                                                    |    |

| Figure 5.4: Layout top layer (TOP)                                                 |    |

| Figure 5.5: Layout upper inner layer (L2)                                          |    |

| Figure 5.6: Layout lower inner layer (L3)                                          |    |

| Figure 5.7: Layout bottom layer (BOT)                                              |    |

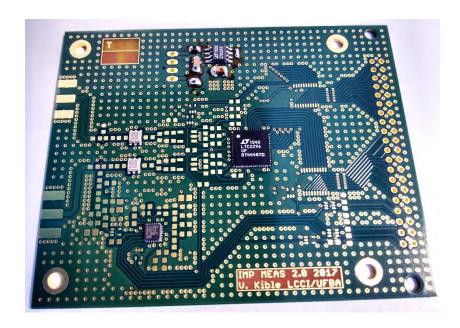

| Figure 5.8: Populated System PCB                                                   |    |

| Figure 5.9: Nucleo 64 Top Layout [43]                                              |    |

| Figure 5.10: Nucleo 64 Bottom Layout [43]                                          |    |

| Figure 5.11: Atollic TrueSTUDIO Code Editor                                        |    |

| Figure 5.12: STM32CubeMX Pin Assignment View                                       |    |

| Figure 5.13: Data Flow Diagram of Microcontroller Software                         |    |

| Figure 5.14: Microsoft Visual Studio C# 2010 (GUI Editor)                          |    |

| Figure 5.15: PC Software GUI in Mode "TEST Num"                                    |    |

| Figure 5.16: Save File Dialog of PC Software                                       |    |

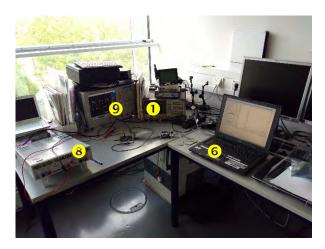

| Figure 6.1: Test Setup - Overview                                                  |    |

| Figure 6.2: Test Setup - Closeup                                                   |    |

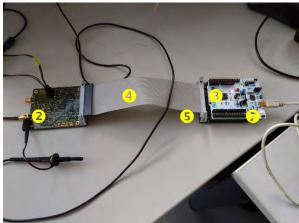

| Figure 6.3: Block Diagram of Test Setup 1                                          |    |

| Figure 6.4: Measurement Point for PLL Output                                       |    |

| Figure 6.5: Block Diagram Test Setup 2                                             |    |

| Figure 6.6: Measurement Setup for Reflection Coefficient Measurements              | 88 |

| Figure 6.7: Chart of Measured Reflection Coefficients                              |    |

| righte 6.1: Alliomatic impedance Matching System                                   | 97 |

| Figure 8.2: Flow-Chart of Proposed Complex Control Algorithm         | 99  |

|----------------------------------------------------------------------|-----|

| Figure A.1: Schematic of the PLL Circuit                             | 111 |

| Figure A.2: Frequency Domain Simulation Results                      | 113 |

| Figure A.3: Time Domain Simulation Results                           | 113 |

| Figure A.4: Cases for the RF Part of the System                      | 115 |

| Figure A.5: System PCBs with Power Supply Circuit Populated          | 116 |

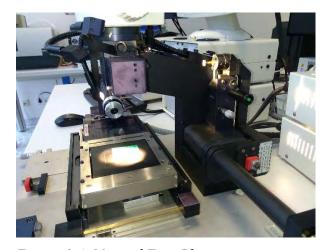

| Figure A.6: Manual Fine-Placer                                       | 116 |

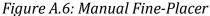

| Figure A.7: Semi-Automatic Dispenser                                 | 116 |

| Figure A.8: Result of soldering the ICs onto the first system PCBPCB | 117 |

| Figure A.9: Almost finished Status of the System PCB (Top Side)      | 118 |

| Figure A.10: Almost finished Status of the System PCB (Bottom Side)  | 118 |

| Figure A.11: Completed System PCB (during Test)                      | 119 |

|                                                                      |     |

## **List of Tables**

| Table 3.1: Max. frequency vs. load capacitance of 74AUP1G80 at 3.0 to 3.6 V supply | 34 |

|------------------------------------------------------------------------------------|----|

| Table 3.2: Chosen values for ADF4360-9 frequency synthesizer and effect            | 37 |

| Table 3.3: Some Values for fs and $C_R$ depending on N and W for fi=400 MHz        | 39 |

| Table 4.1: Example for output of FFT test (here for 0.1% frequency deviation)      | 46 |

| Table 4.2: Overview of FFT test results                                            | 47 |

| Table 4.3: Results of ADS-Simulations of whole simplified System                   | 48 |

| Table 4.4: Statistics of ADS-Simulations                                           | 50 |

| Table 4.5: Simulation Results of Complete System using LTSpice                     | 54 |

| Table 4.6: Statistics of System Simulations using LTSpice                          | 57 |

| Table 4.7: Statistics of Erroneous Random Noise Simulations using LTSpice          | 59 |

| Table 5.1: rFFT Output Assignment                                                  | 78 |

| Table 6.1: Complete Measurement Results including SOL-Correction                   | 89 |

| Table 6.2: Performance Comparison                                                  | 92 |

| Table 7.1: Criteria and weights for evaluation of algorithms                       |    |

| Table 8.1: Square matrix of matching circles                                       |    |

## **Acknowledgements**

Special thanks I would like to express towards my wife Karolinne Brito Kible and my son Benjamin as well as my parents Dieter and Rose Kible for their patience and helping me to keep my spirits up.

My deepest gratitude goes to my advisor Prof. Dr. Robson Nunes de Lima for his help and persistence, also over the distance of an ocean.

Furthermore, I would like to thank Prof. Dr. André Zimmermann, André Bülau and Florian Janek from Hahn-Schickard Stuttgart for their practical support in writing scientific papers and in placing and soldering some difficult components as well as help using the institute's equipment and Mohamed Elkeshti for his contribution to chapter 7 under my supervision. I also would like to express my gratitude to the staff of the Programa de Pósgraduação em Engenharia Elétrica (PPGEE) of the UFBA for their help with concluding this work.

Finally, I would like to thank the FUNDAÇÃO DE AMPARO À PESQUISA DO ESTADO DA BAHIA (FAPESB) for their financial support during the beginning of the work.

### **Abstract**

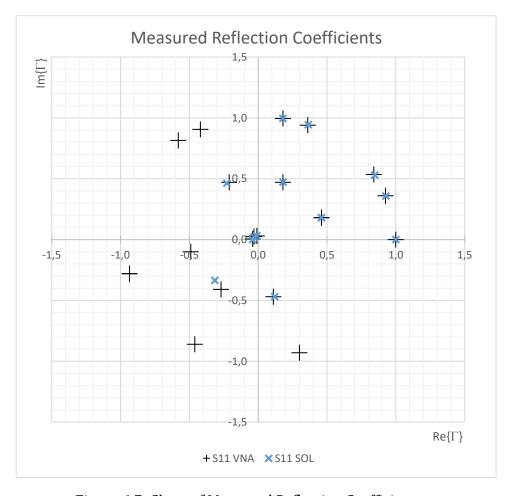

In general, there are two principles to determine the reflection coefficient: one is based on interferometry, as used by the six-port reflectometer. Another method is based on the separation of reflected and incident waves and calculating their ratio. This method relies on directional couplers or similar devices and is used in most vector network analyzers. Based on this principle, a simplified reflectometer for measuring the load impedance of a power amplifier, was developed. This reflectometer measures the reflection coefficient at radiofrequencies. An interesting strategy to reduce non-idealities and size of a reflectometer system is to carry out different processing steps for the software domain. The challenging in this case are the processing requirements for real-time analysis of the radiofrequency signals. To counteract the processing requirements, sampling effects in the inevitable analog-to-digital converter are exploited.

Physical and mathematical constraints for software-defined reflectometers based on under-sampling down-conversion and their design theory are defined. Then the validity of the concept and design theory were proven by computer simulations and automated measurements against known references. The reflection coefficient measurement errors on a discrete printed circuit board setup at 400 MHz were below 2% using under-sampling down-conversion. This is a particularly promising result when compared with similar systems. Under severe mismatch conditions, the under-sampling scheme failed, but these cases present a high standard deviation and are thus easily recognizable. Responsible for the failure of the under-sampling are harmonics generated at the output of the unprotected power amplifier. Various promising remedies for the under-sampling failure are outlined. However, as the system is planned to be part of an automatic impedance matching system, extreme mismatch conditions should normally not occur.

Our study shows that a software-defined reflectometer for radiofrequency (300 MHz to 3 GHz), based on standard hardware components and implementable in integrated circuit technology, for dynamic impedance matching purposes, is feasible.

## Resumo

Em geral, existem dois princípios a partir dos quais é possível determinar o coeficiente de reflexão: um é baseado na interferometria, como no refletômetro de seis portas. O outro método é baseado na separação das ondas refletidas e incidentes. Este método se baseia em acopladores direcionais ou dispositivos semelhantes e é usado na maioria dos analisadores vetoriais de rede. Com base nesse princípio, foi desenvolvido um refletômetro simplificado para medir a impedância de carga de um amplificador de potência. Esse refletômetro mede o coeficiente de reflexão em radiofrequências. Uma estratégia interessante para reduzir as não-idealidades e tamanho do sistema é realizar diferentes etapas de processamento em software. O desafio, nesse caso, são os requisitos de processamento para análise em tempo real dos sinais de radiofrequência. Para balancear tais requisitos, os efeitos de amostragem no conversor analógico-digital podem ser utilizados.

Restrições físicas e matemáticas para refletômetros definidos por *software* com base na conversão de subamostragem e sua teoria de projeto são definidas. Em seguida, realizaram-se simulações em computador e medições automatizadas para comprovar o conceito e a teoria do projeto, comparando os resultados com referências conhecidas. Os erros de medição do coeficiente de reflexão, em uma configuração discreta a 400 MHz, foram inferiores a 2% usando subamostragem de conversão descendente. Esses resultados são promissores quando comparados com sistemas semelhantes. Em condições de forte desadaptação, o esquema de subamostragem falhou, mas esses casos apresentam um desvio padrão alto e, portanto, são facilmente reconhecíveis. Tais falhas da subamostragem são causadas pelos harmônicos gerados na saída do amplificador de potência desprotegido. Várias soluções promissoras para a falha de subamostragem são apresentadas. No entanto, como o sistema é planejado para fazer parte de um sistema automático de adaptação de impedância, condições extremas de desadaptação não devem ocorrer normalmente.

Nosso estudo mostra que um refletômetro definido por software para radiofrequência (300 MHz a 3 GHz), baseado em componentes de hardware padrão e implementado em tecnologia de circuito integrado, para fins de adaptação dinâmica de impedância, é viável.

## 1 Introduction

## 1.1 Theme and Justification

Mobile RF telecommunication systems are of central importance for the modern society. Amongst others, they are used in the fields of consumer electronics, military, medical technology, and industrial automation, and will gain even higher pervasion with current developments such as the internet of things and industry 4.0 [1].

Such systems use antennas for converting the internal transmission line bound RF signals to electromagnetic radiation traveling between devices. These antennas are often hidden inside the case of the mobile devices and thus can be in direct proximity to the users' bodies, a condition which can frequently be observed in cellular phones. It is known that the electric properties of the antenna, especially its input impedance, depend on the surrounding materials. Because these are generally unknown and often varying, the input impedance can also not be assumed as constant. The proximity of a user head or hand [2], [3] can alter the antenna input impedance significantly, possibly leading to a varying impedance mismatch between the antenna and adjacent building blocks of the digital transceiver.

Digital transceivers are the heart of modern RF telecommunication systems. They comprise of various building blocks as shown in Figure 1.1. The building blocks adjacent to the antenna are the low noise amplifier (LNA) in the reception path and the power amplifier (PA) in the transmission path. While the effect of varying antenna input impedance on the LNA is generally a reduction of input power and can be compensated in the following intermediate frequency variable gain amplifier (IFVGA), the effect on the power amplifier (PA) can be more severe.

For the PA, the varying antenna input impedance results in a changing load reflection coefficient. More exactly, the load reflection coefficient can change in phase and magnitude. Ideally, the magnitude would be zero. Increasing magnitudes of the load reflection coefficient imply that an increasing amount of the transmission power is reflected back to the PA. To bridge transmission distances of few kilometers as usual in mobile communications, the output power of the PA must be high compared to the other parts of the system (except in ultra-low transmission power devices). As a total reflection of the output power back to the PA can occur, the signal amplitude at the PA output can get very high. This can cause degradation of the PA's properties such as linearity or efficiency and can in extreme cases even damage the PA if not protected [4].

Figure 1.1: A Typical Digital Transceiver (Superheterodyne)

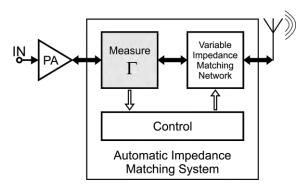

So, it is of crucial interest to find countermeasures against the effects of a change of antenna input impedance. There exist various approaches, from dissipating the reflected power and automatic gain control of the PA [5], out-phasing amplifiers [6], hybrids [7] and distributed active transformers [8] to variable impedance matching networks [4], [9]-[11].

Approaches other than the variable impedance matching networks have in common that they can reduce the susceptibility of the PA output to the impedance variation by some factor, but the mismatch and its effects still occur.

Variable impedance matching networks offer the possibility to dynamically match the varying antenna input impedance to the PA output impedance and thus keep the load reflection coefficient close to the ideal zero. For this operation, the current antenna input impedance must be monitored continuously. The combination of a reflection coefficient measurement block, the control block, often incorporating software, and the variable impedance matching network is called an automatic impedance matching system, as shown in Figure 1.2.

Figure 1.2: An Automatic Impedance Matching System

This work will focus on the reflection coefficient measurement block of such an automatic impedance matching system. Compared to the variable impedance matching network and the control block [12]-[13], relatively few research activities are ongoing in this field, making it interesting for contribution. Furthermore, such a measurement block can be used not only in an automatic impedance matching system, but also in instrumentation, for example for measuring the humidity content in material samples via interaction with RF waves [14]. For this purpose, only an RF signal source and an antenna

which couples the RF waves into the material sample, for example a slotted hollow wave guide [15], are needed besides the measurement block.

In [16], the use of injection locking and quadrature amplitude demodulation for measuring the load impedance was explored. Research on possibilities to correct shortcomings of this method such as offset problems, non-idealities of the mixers and others gave rise to a completely new approach: A software defined reflection coefficient measurement block based on under-sampling down-conversion.

The new approach is expected to consume less power because less circuitry is involved. The involved digital or mixed signal circuitry, such as the analog to digital converter, would be necessary in any case. Analog circuitry is replaced by computations in the digital domain with their inherent exactness. This comes at the cost of raised requirements at the analog to digital converter, especially its sample and hold circuitry. The necessary sample clock can be derived from the UHF local oscillator or from the transmit signal itself, guaranteeing a fixed frequency relationship.

By means of using a non-zero intermediate frequency in the digital domain, the effects of nonidealities of the remaining analog circuitry such as offsets are avoided. Under-sampling down-conversion is used to limit the complexity of the analog to digital converter and digital signal processing requirements, by reducing the necessary sample clock frequency (in the lower MHz range instead of UHF) and avoiding other analog blocks.

As already stated in [16], the system frequency was chosen to be in the range of 400 MHz (low UHF). This frequency is sufficiently high to get high frequency effects (it allows for extrapolation into the middle and higher UHF range), but also so low that the wavelength is big enough (in the 0.7 m range) to make it challenging to integrate wave guide structures. Also, antenna mismatch occurs often in the MICS band (Medical Implant Communication Service, 402 to 405 MHz, limited to 25  $\mu$ W output power to minimize interference), as the devices that operate in this band are frequently worn close to the body or implanted. There is an ISM band (Industrial, Scientific and Medical, 433.050 to 434.790 MHz) in this frequency range as well. This band allows higher output powers and license free operation, but it is only defined for region 1 (Europe, Africa and Middle East).

#### 1.1.1 Objectives

The proposition of this work consists in the study and the conception of improved RF reflection coefficient measurement systems. To this end, the use of under-sampling down-conversion in the inevitable analog to digital converter and software-defined reflection coefficient measurement will be investigated.

Specific objectives will be:

- Design and implementation of a software defined RF reflection coefficient measurement system based on under-sampling down-conversion for 400 MHz UHF in discrete technology, with software-defined part using standard Fast-Fourier-Transform (FFT) together with complex division.

- Characterization and evaluation of the system with simulations and measurements.

Due to limitations in the availability of integrated circuit (IC) design software in the second half of the doctorate studies, the third objective was changed from IC design to elaboration of design considerations of the software-defined part of the system including analysis of different signal processing algorithms and a possible matching algorithm.

## 1.2 Text organization

This text is organized in nine chapters. The second chapter will focus on the theory behind the used techniques for the reflectometer and the according literature review. Chapter three focuses on the principle of operation of the system which was designed to proof the feasibility of the new approach, and chapter four presents computer simulation results of the whole system and some of its parts. The fifth chapter then reports details on the design and implementation process of the system, while measurement results after short-open-load (SOL) compensation are presented in chapter six. Chapter seven describes design considerations for the software defined part of the system, and chapter eight the outline of an improved complex control algorithm for an automatic impedance matching system. And finally, chapter nine presents the conclusion.

## 2 Literature Research and Theoretic Foundation

## 2.1 Reflection Coefficient Measurement Techniques

The reflection coefficient  $\Gamma$  is the complex division of the reflected signal  $V_r$  by the incident signal  $V_i$ :  $\Gamma = V_r/V_i$ . Thus, the straight forward first step to measure the reflection coefficient is generally to separate the incident and the reflected signal. This can be done by a circulator or by a directional coupler. After separating the two signals, the phase and amplitude relationship between both must be analyzed to allow the complex division. The most direct approach to do this is the Polar one.

#### 2.1.1 Polar Approach

The phase between the reflected and the incident signal can be measured using a phase detector such as a digital XOR gate or phase-frequency-detector (PFD), a Gilbert cell or a passive mixer, that outputs an analog signal proportional to the phase between the two signals (after filtering). For this operation, the amplitude information must be removed from both waves, to make sure the phase detector only measures the phase. This can be done with the help of limiters. This system was described in [17]. For the complete reflection coefficient information, the amplitudes of incident and reflected wave also must be measured, what can be done with diode power detectors. This system was described in [18]. In total, three analog signals must be measured: The phase between reflected and incident signal, the reflected amplitude, and the incident amplitude.

The disadvantage of the diode power detectors is, due to their nonlinear nature, they require some sort of linearization technique in the following circuitry or software, what makes the system more complex. A block diagram of this topology can be found in Figure 2.1. Here,  $V_r$  is the reflected signal,  $V_i$  is the incident signal, and  $\phi$  is the phase between both signals.

Figure 2.1: Polar Approach

#### 2.1.2 Cartesian Approach

Instead of using diode power detectors, it is possible to use in total three mixers (active or passive), two for the reflected wave and one for the incident wave. This way the phase detector also becomes unnecessary. Additional circuitry is necessary to generate 0° and 90° phase shifted signals with removed amplitude information from the incident signal. For the reflected wave, one mixer is fed with the 0° signal and one mixer is fed with the 90° signal, resulting in linear quadrature amplitude (IQ) demodulation [19]. This means an Vr\_I inphase (the real component of the wave) and a Vr\_Q quadrature DC-signal (the imaginary component of the wave) are generated. So, the vector of the wave is known in a Cartesian coordinate system, effectively preserving the amplitude and the phase in respect to the incident signal. Finally, the amplitude of the incident signal must be measured, possibly also with in-phase amplitude demodulation (resulting in Vi\_I), this way avoiding diode power detectors and their nonlinearities.

This results in three analog signals that must be measured, like in the Polar case, if the  $0^{\circ}$  signal is synchronous with the  $V_i$  signal

However, in some cases the  $0^{\circ}$  signal is not completely synchronous to  $V_i$ , for example if a quadrature injection locking oscillator is used to generate the  $0^{\circ}$  and  $90^{\circ}$  signals [16]. This results in a slowly varying phase shift between  $V_i$  and the  $0^{\circ}$  signal. Nevertheless, the  $0^{\circ}$  and the  $90^{\circ}$  signal have the correct, fixed phase relationship required for the IQ-demodulation. In this case a fourth mixer can be added, using the  $90^{\circ}$  signal also for the incident wave and allowing the removal of the variable phase shift from the final reflection coefficient result.

As these techniques convert the RF signal directly to DC, they suffer from problems with small amplitudes and large offsets of the mixers. A block diagram of this topology can be found in Figure 2.2.

Figure 2.2: Cartesian Approach

#### 2.1.3 Superhet Cartesian Approach

In reference [19], a second approach is described, removing problems with small amplitudes and large offsets of the mixers as seen in the normal Cartesian approach. Basically, the conversion of the signal is not done to DC but to an intermediate frequency (IF), allowing amplification and filtering of the IF more easily while preserving the phase and amplitude information. Afterwards, the IF is quadrature demodulated in a second step,

allowing for much higher amplitudes and so much lower influence of the offset error. This approach is known as Superheterodyne or Superhet. Unluckily it adds a lot of complexity to the system, and still converts the signals to DC in the analog domain in the end, making them sensitive to analog errors and inaccuracies.

#### 2.1.4 New Software Defined Approach proposed in this Thesis

Instead, the two RF signals can be analyzed directly, moving all complexity of the system into the digital domain. The down-conversion to IF can be done directly by under-sampling down-conversion (explained in the subsection of the same name) in the Analog-to-Digital Converter (ADC), removing effectively all mixers from the circuit. Then the IF is analyzed by software, for example incorporating a Fast Fourier Transform (FFT), thus removing all offset and possibly modulation errors completely. This technique should present the best possible performance for such a measurement system.

However, such a software defined system may have limitations in its bandwidth in the case of strong under-sampling or presents high requirements for the digital signal processing due to the high signal frequencies in the case of weak or no under-sampling. Here, reducing the signal processing requirements seemed more important than large bandwidth, therefore relatively strong under-sampling was adopted. In this case, high bandwidth modulated signals may produce erroneous outputs, not only due to problems with synchronizing the sample clock to the input signal.

The sampling clock of the ADC must have a defined relation to the RF frequency. This can be achieved with a (partly analog) Phase-Locked Loop (PLL) frequency synthesizer or with a Direct Digital Synthesis (DDS) circuit. As DDS for RF are still expensive and produce spurs, we will assume that a PLL is used (described in the subsection "PLL for frequency synthesis").

For all approaches mentioned above, a device to separate the signal incident to the antenna from the signal reflected from the antenna is necessary. This function can be fulfilled by a (quasi-) circulator or by a (bi-) directional coupler. Couplers have advantages of low main-line loss (at the PA output) and better isolation between main-line and the measurement branch of the system.

## 2.2 Directional Couplers

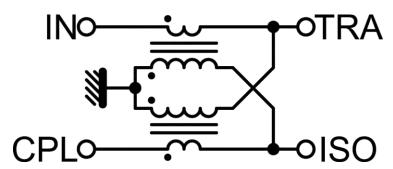

Directional couplers direct power from the main input port (IN) to the main output port (TRA) and vice-versa, also see Figure 2.4 in section 2.2.3. The attenuation in the main path can be low, often considerably below 4dB [16]. The important property of the directional coupler is that it directs a portion of the incident signal to a third port called "coupled" (CPL) and a portion of the reflected signal to a fourth port, often called "isolated" (ISO), making them available for measurement. The magnitude of the signals at the CPL and ISO ports is often considerably smaller than the one of the signals at the IN and TRA ports. Commercially available are coupling values between 3dB and 50dB [16]. A common coupling value of 15dB means that the signal at the CPL port is 15dB lower than the incident signal at the IN port.

It is possible to integrate directional couplers on a monolithic chip. For frequencies in the range around 30 GHz, these couplers are based on parallel coupled transmission lines on the chip [20]. For frequencies in the UHF-range (300 MHz to 3 GHz), these transmission lines would get long (the typical length is a quarter of the wavelength), so that they are frequently replaced by lumped inductors, coupled inductors or transformers and capacitors for integration. Often the used technology is one specialized in producing high quality passives, such as Integrated Passive Device (IPD) technology, Silicon On Insulator (SOI) or Low Temperature Cofired Ceramic (LTCC).

#### 2.2.1 Lumped Inductors and Capacitors

There exist various topologies, with capacitors as central element [21], or with inductors as central element [22]. There instead of the Pi-topology to replace the transmission lines with lumped components, the T-topology can also be used [23]

#### 2.2.2 Coupled Inductors (Transformers) and Capacitors

Interleaved Transformers have been used [24] as well as coupled synthesized co-planar waveguides (Figure 2.3) [25]. However, on low impedance or lossy substrates coupled inductors are difficult to achieve.

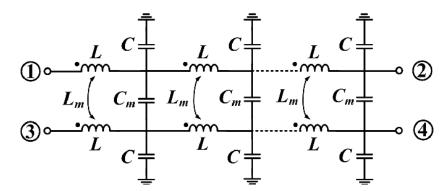

Figure 2.3: Directional Coupler using Coupled Inductors and Capacitors [25]

#### 2.2.3 Two Transformer Approach

The two-transformer approach is widely used for low frequency directional couplers in wire-wound discrete technology. A theoretical treatment of the matter can be found in [26]. However, at least for high impedance / low loss substrates, an integration of this topology for higher frequencies should also be possible. A simplified schematic of this approach is shown in Figure 2.4.

Figure 2.4: Directional Coupler using two Transformers

# 2.3 Injection Locking Frequency Dividers and their Digital Counterparts

The elaborated system described in chapter 3 uses the main-line frequency as a source of the sampling clock for the ADC, so that the signal frequency and the sample clock have a fixed relationship, what is necessary for the function of the under-sampling down-conversion process. The main-line frequency is converted to the sampling frequency using a PLL circuit that will be described later. However, the used PLL circuit has a limited input frequency range. Therefore, it is necessary to divide the RF before feeding it into the frequency synthesis integrated circuit. Frequency dividers will be discussed in this subsection.

#### 2.3.1 Injection Locking Frequency Dividers

Injection locking (IL) is a nonlinear effect in any oscillator (mechanical, optical, and electronic). An oscillator locks (synchronizes) to an injected (fed in) signal from an external source, if the signal has sufficient amplitude and is inside a frequency range (lock range) around the natural frequency of the oscillator.

By adequate construction of the oscillator and input point of the injected signal, it is also possible to lock the oscillator to low integer fractions n (n=2, 3, ...) of its natural frequency. This operation results in a divide-by-n frequency divider.

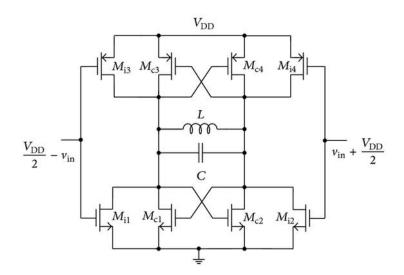

An example schematic of a divide-by-3 IL frequency divider is shown in Figure 2.5 [27].

Figure 2.5: Divide-by-3 Injection Locking Frequency Divider

#### 2.3.2 D Type Flip-Flop as Frequency Divider

A D-type flip-flop is a simple digital one-bit memory [28]. Typical implementations store the state of the data (D) input on the rising edge of the clock (CLK) input. There can be two

outputs, the positive Q-output, and the negated /Q-output. However, often only one of these is used. For using the flip-flop as frequency divider, it is practical to connect /Q with D. So on every positive CLK-edge the state of the flip-flop is inverted. This results in a signal of half frequency of CLK at the /Q-output. In other words, it is a divide-by-two frequency divider.

#### 2.3.3 Digital Counters

For higher division ratios, typically digital counters are used [29]. They comprise of flip-flops and combinatory logic. The counter adds one to the digital number stored in its flip-flops on every rising edge of the clock input. When the value stored in a digital register is reached, the counter is reset and the output toggles. This way, the division factor is determined by an (within the limits of the register) arbitrary integer number. The size of the register (and counter) in bits sets the absolute lower limit of the output frequency of the divider.

In the system of section 3, the output signal of the frequency divider is fed into the frequency synthesis circuit, that is described in the following subsection.

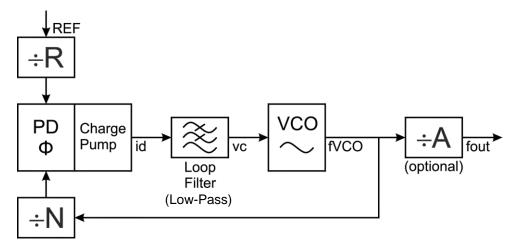

## 2.4 Phase-Locked Loop for Frequency Synthesis

The simplest implementation of a phase-locked loop comprises of phase detector (PD), a loop filter and voltage-controlled oscillator (VCO). The output frequency of the VCO ( $f_{VCO}$ ) is fed into one of the two inputs of the PD. The other input (REF) is connected to a reference frequency. The PD is often a digital circuit such as a phase-frequency-detector (PFD) with a charge pump (CP) that outputs positive or negative current pulses ( $i_d$ ) of a duration proportional to the phase difference between its input signals. These current pulses must be converted to a DC-voltage ( $v_c$ ) that can be fed into the VCO. This function is fulfilled by the loop filter that also serves to stabilize the feedback loop. The output frequency of the VCO thus is controlled by the phase difference between itself and a reference signal. This results in a VCO output of the same frequency and with zero phase difference to the REF input. Adding a frequency divider at the REF input (frequently named R-divider), the output frequency can be divided down in integer steps [30], also see Figure 2.6 in the next section.

#### 2.4.1 Integer-N

The system becomes more interesting by adding a frequency divider into the feedback from VCO to PD. Then the frequency can not only be divided, but also multiplied by an integer factor. This divider is normally named N-divider [30]. The output frequency thus is described by equation (1):

$$f_{VCO} = \frac{N}{R} \cdot f_{REF} \tag{1}$$

The crucial advantage of this approach is that it produces no spurious frequency components at the output (spurs). However, for a fine adjustability of the output frequency, a high division ratio R is necessary, reducing the frequency at the PD significantly. This produces higher phase noise and slower adjustment of the loop to a change in input phase

or frequency because the loop filter needs to have a lower cut-off frequency and thus slower step response. A block diagram of such a system can be found in Figure 2.6. It includes an A divider for the output signal f<sub>out</sub> for additional frequency flexibility.

Figure 2.6: Integer-N PLL Frequency Synthesizer

#### 2.4.2 Fractional-N

By switching the N divider between several different values continuously, a fractional multiplication factor can be achieved. While achieving a fine adjustment step size, this makes much higher frequencies at the PD possible, thus making the loop faster and reducing phase noise. The disadvantage of this approach is that it produces spurs at the output due to the continuous switching operation. This problem can be reduced by applying the  $\Sigma\Delta$  modulation technique to the switching operation [30].

#### 2.4.3 Loop Analysis

The PFD has a transfer function as in equation (2), with the reference phase  $\theta_{REF}$  and the output phase  $\theta_{OUT}$  of the PLL, the conversion factor  $K_{PFD}$  and the output current  $i_d$  of the PFD:

$$i_d = K_{PFD}(\theta_{REF} - \theta_{OUT}) \tag{2}$$

With (3), including the charge pump current  $I_{CP}$ :

$$K_{PFD} = \frac{I_{CP}}{2\pi} \tag{3}$$

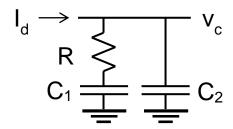

The loop filter can be active or passive. For high frequencies, generally a passive filter is used. The most common topology, consisting of the capacitors  $C_1$  and  $C_2$  and the resistor R, is shown in Figure 2.7.

Figure 2.7: Common loop filter topology

The capacitor  $C_2$  is typically chosen so that its impedance is much higher than the impedance of R and  $C_1$  together at the PD-frequency. A typical value is  $C_2=C_1/10$ . This means that  $C_2$  can be neglected for the analysis of the loop behavior.

The simplified transfer function of the loop filter is shown in equation (4):

$$F(s) = \frac{sC_1R+1}{sC_1} \tag{4}$$

The transfer function of the VCO with the N-divider is (5), with the output phase  $\theta_{VCO}$ , the control voltage  $v_c$  and the conversion factor  $K_{VCO}$  of the VCO as well as a loop division factor N:

$$\frac{\theta_{VCO}}{v_C} = \frac{1}{N} \frac{K_{VCO}}{s} \tag{5}$$

The general PLL closed loop gain is (6):

$$\frac{\theta_{VCO}}{\theta_{REF}} = \frac{KF(s)}{s + KF(s)} \tag{6}$$

With (7):

$$K = \frac{K_{PFD}K_{VCO}}{N} \tag{7}$$

In its general form, the overall feedback loop transfer function becomes (8) for this loop filter, using (4) and a general second order transfer function:

$$\frac{\theta_{VCO}}{\theta_{REF}} = \frac{\omega_n^2 \left(\frac{2\zeta}{\omega_n} s + 1\right)}{s^2 + 2\zeta \omega_n s + \omega_n^2} \tag{8}$$

With the natural frequency  $\omega_n$  (9) and damping factor  $\zeta$  (10):

$$\omega_n = \sqrt{\frac{K_{PFD}K_{VCO}}{NC_1}} \tag{9}$$

$$\zeta = \frac{R}{2} \sqrt{\frac{K_{PFD} K_{VCOC_1}}{N}} \tag{10}$$

The filter components can be calculated as in (11) to (14):

$$C_1 = \frac{K_{PFD}K_{VCO}}{N\omega_n^2} \tag{11}$$

$$R = \zeta \frac{2N\omega_n}{K_{PFD}K_{VCO}}$$

(12)

$$|X_{C2}| = 10|X_{C1} + R| (13)$$

With the reactances  $X_{C1}$  and  $X_{C2}$  at the natural frequency as follows in (14):

$$X_{Ca} = \frac{1}{j\omega_n C_a} \text{ with } a = 1, 2.$$

(14)

The 3dB bandwidth  $\omega_{3dB}$  of the PLL is then (15):

$$\omega_{3dB} = \omega_n \cdot \sqrt{1 + 2\zeta^2 + \sqrt{4\zeta^4 + 4\zeta^2 + 2}}$$

(15)

This equation can be approximated with (16) and (17):

For

$$\zeta > 1.5$$

$\omega_{3dB} = \omega_n \cdot 2\zeta$  (16)

For

$$\zeta < 1.5$$

$$\omega_{3dB} = \omega_n \cdot \left(1 + \zeta \cdot \sqrt{2}\right) \tag{17}$$

Typical values for  $\zeta$  are between 0.3 and 5, often used is 0.707.

The condition for loop stability is as in (18) [30], with phase detector frequency ω<sub>PD</sub>:

$$\frac{\omega_{PD}}{\omega_n} \ge 2\pi\zeta \tag{18}$$

For  $\zeta$ =0.707, this means that this ratio must be bigger than 4.4. Often used is a ratio of 10.

These considerations should be sufficient to calculate the components of the loop filter for the application. All other necessary equations can be found in the datasheet of the integer-N PLL frequency synthesizer Analog Devices ADF4360-9 that was chosen to be used for the system (see chapter 3.4).

The central principle of the planned system is based on using the output frequency of the frequency synthesis circuit as sample frequency for the analog-to-digital converter (ADC). The ADC performs under-sampling on the two RF signals, this way down-converting them to a low intermediate frequency (IF) in the digital domain.

## 2.5 Analog-to-Digital Converter (ADC)

Generally, an ADC consists of two main blocks: the sample and hold (or track and hold) block and the quantizer. The information here is a summary of [31], chapter 17.3, therefore no single references are given.

#### 2.5.1 The Quantizer

The quantizer converts the continuously valued (but often discrete time) input signal into discrete digital values. This leads to quantization noise because the signal now is made from steps rather than smooth transitions. The quantization noise content of the digital signal is lower when more discrete steps are used, however the quantization into a larger number of discrete values (represented by a higher number of bits) comes at the cost of lower conversion speed or higher circuit complexity or both. So, a reasonable trade-off must be found.

For one bit (above or below a certain level), the quantization function is fulfilled by an electronic comparator. For higher bit numbers (or more discrete digital values), there are various topologies, each with certain advantages and disadvantages:

#### Flash-ADC

Mainly consists of a high number of comparators according to the number of levels to be distinguished. Necessary are 2<sup>b</sup>-1 comparators for a given number of resulting bits "b". For 8 bits, this means 255 comparators are used, what results in a comparably large integrated circuit. On the other hand, this topology is extremely fast (several giga-samples per second / GSps) The outputs of the comparators are merged to the desired digital number by means of a logic network.

#### Pipelined ADC

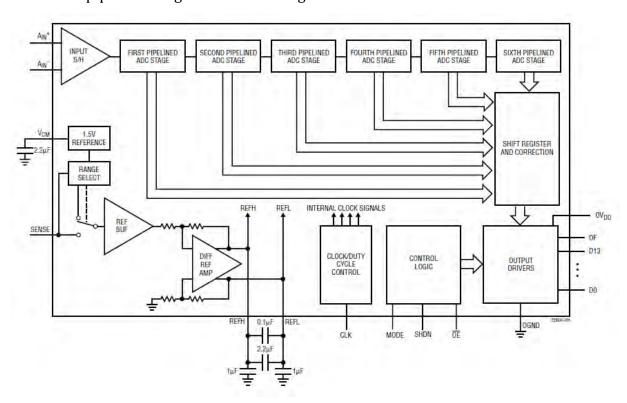

Here smaller flash-ADCs and digital-to-analog converters (DACs) are used in sequence to reduce the number of required comparators considerably. The first stage does a rough estimate, and the second stage refines this estimate. Also, three or more stages are possible. This way, a 10 bit ADC composed of two 5 bit stages just needs  $2\square(2^5-1) = 2^6-2 = 62$  comparators instead of 1023. Disadvantages are a lower (but still high in the order of many MSps) conversion speed and possible challenges with the linearity of the circuit. An according topology is used by the ADC utilized in this work (see section 3.5, especially Figure 3.5).

#### Successive Approximation Register ADC

It is also possible to use just one comparator together with a DAC and a memory device that stores the last state of the conversion. Then the comparison level of the comparator is varied according to a bisection method: First the whole conversion range is divided in two and the MSB is generated. Then according to the MSB, either the upper or the lower half is again divided in two and checked, generating the second bit, and so forth until the desired number of bits is reached. This requires exactly the same number of conversion cycles as the number of desired bits, thus it is still relatively fast (up to some MSps) and allows higher numbers of bits with much lower circuit complexity than the preceding architectures.

#### Delta-Sigma ADC ( $\Delta\Sigma$ )

For highest resolutions (number of bits up to 24 and beyond), it is common practice to use noise shaping. With the according circuitry, it is possible to shift noise into higher frequency bands of the digital signal where it can be removed using a digital filter. This way, the noise content of the signal of interest is reduced considerably. Unfortunately, the digital filter also reduces the data rate. Even though high sample rates (some MSps) are used, the effective data rate can be only some few Sps at the highest resolution.

An advantage is that the resolution and the data rate can be traded off against each other by adjusting the digital filter, to achieve an optimum compromise for each application. The quantizer here is often just one-bit and combined with an analog summation and integration circuit and a one-bit DAC. The final resolution is achieved only by the digital filtering. However, this scheme relies on massive over-sampling instead of under-sampling and is thus less interesting for this work.

For even lower conversion speeds, there are simpler topologies for ADCs achieving similar resolutions as the  $\Delta\Sigma$  and avoiding the digital filter. These are mostly based transferring the level of the signal into an integration time (producing a slope, thus the name "Single-Slope" and "Dual-Slope") and measuring this level dependent time by means of a clocked counter, or in newer setups a Time-to-Digital Converter (TDC). The latter allows a better trade-off between conversion time and resolution, but still the conversion times tend to be longer than on a  $\Delta\Sigma$ . The main advantage is the lower complexity.

#### 2.5.2 The sample and hold (S&H) or track and hold (T&H) block

This is an analog device which either opens the input only for a short period of time and keeps its output constant at the last input value during the remaining time of a conversion cycle (S&H), or the output follows the input for half the cycle and stays constant at the last value for the remaining cycle (T&H). Usually, an electronic sample switch and a capacitor to hold the signal at its last value, as well as buffer amplifiers are used for these means.

Either way, the conversion to a digital value takes place during the constant output phase. This has the effect of converting the continuous time input into a discrete time (clocked) output signal as input for the quantizer, leading to sampling effects as utilized in this work and described in section 2.6.

## 2.6 Under-Sampling Down-Conversion

To understand the concept of under-sampling down-conversion, we will first consider general aliasing effects that occur in sampled systems.

#### 2.6.1 Sampling Effects: Aliasing

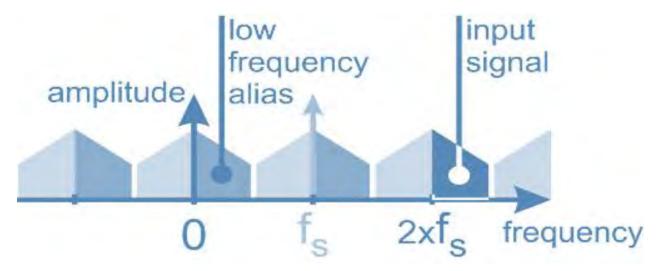

A periodic sampling scheme always produces aliases. These are artifacts that are spaced symmetrically around integer multiples of the sampling frequency [32].

Generally, a signal can only be reconstructed from samples if the sampling frequency is more than two times the bandwidth of the signal, because otherwise the aliases overlap in the frequency domain. For a low pass signal (baseband, centered at the frequency zero), this means that the sampling frequency must be at least two times the highest frequency of the signal. However, for band pass filtered signals, a much lower sample frequency can be sufficient to reconstruct the signal completely, as shown in Figure 2.8.

The alias frequencies of an input frequency  $f_i$  sampled at the sample frequency  $f_s$  appear at  $f_{alias}$ , with N being any integer number (in theory, the aliases also appear at negative frequencies), as described by equation (19) [32]:

$$f_{alias}(N) = |f_i - f_s N| \tag{19}$$

The lowest alias frequency is for the following N (20):

$$N = FLOOR\left(\frac{f_i}{f_s}\right) \tag{20}$$

Figure 2.8: Aliasing for Under-Sampling

#### 2.6.2 Under-Sampling

Under-sampling means that 2fi > fs.

The following conditions (21) and (22) [34] must be fulfilled by the sample frequency to prevent overlap of the aliases:

$$\frac{2f_H}{n} \le f_S \le \frac{2f_L}{n-1} \tag{21}$$

$$1 \le n \le \text{FLOOR}\left(\frac{f_H}{f_H - f_L}\right) \tag{22}$$

With f<sub>H</sub> and f<sub>L</sub> being the upper and the lower limit of the frequency band, respectively.

The signal to noise ratio in dB of any fast ADC is as in (23) [34] (using the number of bits b of the ADC):

$$SNR_{ADC} = 6.02b + 1.76 + 10\log_{10}\left(\frac{f_s}{2f_H}\right)$$

(23)

If  $f_s$  is lower than  $2 \cdot f_H$ , the SNR is reduced. This can also be expressed as a reduction in effective number of bits (ENOB) of the ADC, as shown in equation (24) [34].

$$ENOB = \frac{SNR - 1.76}{6.02} \tag{24}$$

For  $f_s/(2f_H)$  = 1/100, the effective number of bits is reduced by 3.33 compared to Nyquist sampling.

As can be seen from (23) and (24), strong under-sampling reduces the SNR and the ENOB considerably, and raises the low-noise and high-speed requirements on the ADC and the PLL. A trade-off between the acceptable noise level or the required number of bits and the digital processing speed requirements is necessary.

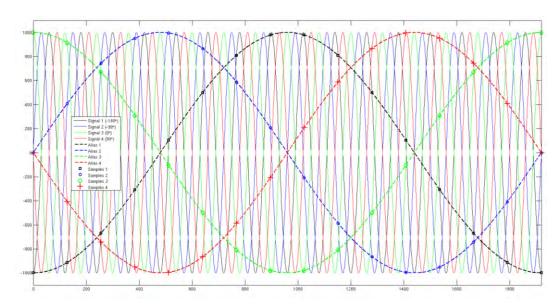

The phase relationship between different signals sampled synchronously is preserved in this operation, as is shown in Figure 2.9. The thin lines are the input signals, the marked points are the samples, and the dashed thicker lines are the low-frequency aliases of the input signals. All graphs of the same color belong together. In the inverted aliases (consider Figure 2.8), the phase is inverted, what can easily be corrected in software.

Figure 2.9: Under-Sampled Signals with Different Phase

#### Example 1:

Applying (19) and (20) to the carrier frequency  $f_i$  of 400 MHz and  $f_s$  of 7.99 MHz and 15.96 MHz, N becomes 50 and 25, and  $f_{alias}$  becomes 0.5 MHz and 1.0 MHz, respectively.

#### 2.6.3 Under-Sampling Down-Conversion

As can be seen from the above example 1, the carrier frequency of 400 MHz is aliased to a much lower frequency in the digital domain. This is equivalent to a mixing operation known as down-conversion. The advantage is that for this operation, only the sampling operation of the ADC is already enough, additional mixers are not required. The disadvantage is that the sampling circuitry of the ADC must have enough bandwidth for the highest signal frequency  $f_H$ , not only for  $f_{alias}$ . This means the bandwidth of the S&H device of the ADC must be more than 400 MHz for the example. This makes the ADC more complex and thus expensive.

## 2.7 Fast Fourier Transform (FFT)

The Fourier Series describes any continuous time periodic signal by a series of sine and cosine functions and their harmonics as well as exponentials [32]. Aperiodic continuous time signals are described accordingly by the Fourier Transform, mathematically transforming the time-domain signals into the frequency domain. However, the signal in the digital domain is now discrete time, discrete valued. Such signals can be transformed into the frequency domain by applying the Discrete Fourier Transform (DFT). There exist various algorithms exploiting properties of subsets of digital signals (such as defined signal lengths and the like) to gain great advantages in computation speed, all together known as Fast Fourier Transform (FFT).

#### 2.7.1 Frequency Bins

As stated above, the FFT breaks down a discrete time signal into a defined set of sine and cosine functions (discrete frequencies). Effectively, as the frequencies of these functions are already defined relative to the record length of the discrete time signal, the transform only calculates the amplitudes for these functions. For each calculated signal frequency (called frequency bin) there exists an amplitude for a sine and for a cosine function, together forming the complex amplitude at this frequency. Phase shifts in the signal contents are depicted in Cartesian form in the complex amplitude, however the Polar form can be derived using the arc tangent function (ATAN2 in most computational systems) for the phase and the square root of the sum of squares of the two complex amplitude components for the magnitude according to the usual way of converting Cartesian into Polar form of complex variables.

#### 2.7.2 Radix-2, Radix-4, Radix-8

The most well-known FFT algorithm (Cooley–Tukey algorithm) is Radix-2, this means that the input data must have a record length of  $2^n$  points for the algorithm to work, n being a positive integer number. The algorithm then uses a divide-and-conquer approach to reduce the number of necessary computations. Accordingly, additional speed can be gained for signals with  $4^n$  (Radix-4) or  $8^n$  (Radix-8) points, allowing for breaking down the signal even more effectively [35]. Other algorithms such as split radix and many more are known and can be found in the respective literature.

## 3 Principle of Operation

## 3.1 System Block Diagram

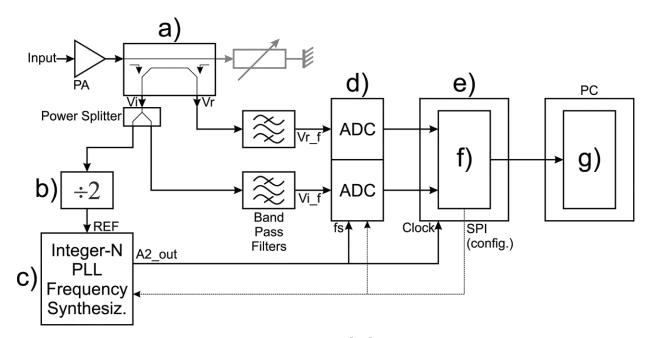

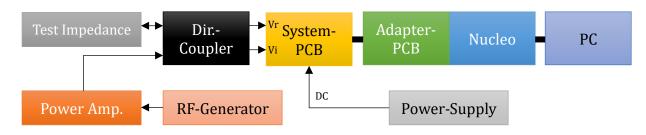

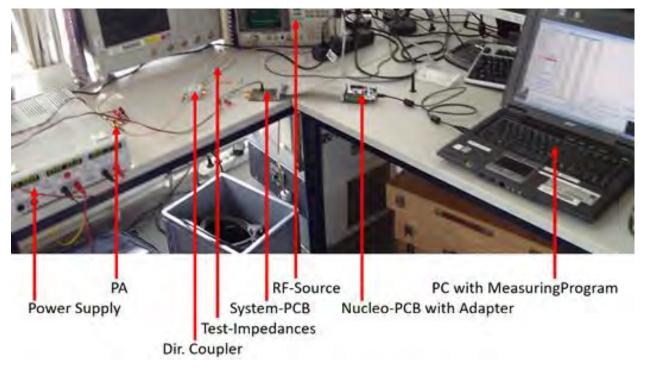

The measurement system comprises of the following blocks, as shown in the block diagram in Figure 3.1:

- a) Directional Coupler

- b) Pre-Divider

- c) Integer-N PLL Frequency Synthesizer

- d) Fast Under-Sampling-Capable Analog-to-Digital Converter (ADC)

- e) System Processor

- f) Microcontroller Software

- g) Personal Computer Software

Not shown are impedance matching networks.

Figure 3.1: System Block Diagram

The incident signal  $V_i$  as obtained by the directional coupler a) is distributed to two different blocks via a resistive power splitter.

One of the two following blocks is the frequency pre-divider b) which divides the V<sub>i</sub>-frequency by two for adjusting it to the input range of the integer-N PLL frequency synthesizer c). The output frequency of the PLL is then used as sample clock for the fast under-sampling-capable analog-to-digital converter (ADC) d) and as data transmission clock for the parallel synchronous data link to the system processor e).

The second portion of  $V_i$  is fed into one of two anti-aliasing band-pass filters and from there into one ADC input. Also, the reflected signal  $V_r$  from the directional coupler is fed into the second anti-aliasing band-pass filter and into the second ADC input. The converted data from the ADC is transferred to the system processor via a parallel synchronous data link.

The system processor microcontroller software f) then analyzes the digital signals and calculates the reflection coefficient. Finally, the results can be fetched by the personal computer (PC) software g) via an USB link.

The PC software also configures the PLL via the system processor and a serial peripheral interface to the PLL chip.

The Power Amplifier (PA) and the directional coupler a) are necessary for the operation of the system but not included in the system board. This allows the operation with different PA and coupler devices and thus makes testing different configurations simple. Similarly, the system controller was not placed on the system board. Instead, a ready-made microcontroller development board was used and connected to it by means of an adapter board and a ribbon cable. This saved development time and makes the system more flexible.

## 3.2 Directional Coupler

For a discrete setup in the 400 MHz UHF range, various bi-directional couplers can be used. An example is the Mini-Circuits SMA bi-directional coupler ZFBDC20-62HP-S [36]. The advantages of this device are its bi-directionality and the comparably low main-line loss (0.25dB at 400 MHz), as well as a coupling factor of about 20dB at 400 MHz. However, as stated before, different couplers can be attached to the system board for testing, what can be interesting for following projects where micro-couplers can be developed.

### 3.3 Pre-Divider Block

The Pre-Divider has the purpose of adjusting the relatively high input frequency of the incident wave signal to the capabilities of the input of the Analog Devices ADF4360-9 integer-N PLL frequency synthesizer (please refer to section 3.4).

An all-digital 74AUP1G80 D-type flip-flop [37] was used due to its high operation frequency capability, its Schmitt-Trigger inputs, and its CMOS nature and case size both of which simplified the application into the system.

This device has the maximum frequency  $f_{max}$  ratings depending on the load capacitance  $C_L$  as shown in Table 3.1. This load capacitance is assumed to be connected from the output of 74AUP1G80 to ground.

Table 3.1: Max. frequency vs. load capacitance of 74AUP1G80 at 3.0 to 3.6 V supply

| C <sub>L</sub> (pF) | f <sub>max</sub> (MHz) |

|---------------------|------------------------|

| 5                   | 619                    |

| 10                  | 550                    |

| 15                  | 481                    |

| 30                  | 309                    |

The D input of the 74AUP1G80 has an input capacitance of 1.5 pF, the REF\_in capacitance of the ADF4360-9 frequency synthesizer is 5 pF maximum. Therefore, with a total load capacitance around 6.5 pF, the Pre-Divider should be able to operate faster than 550 MHz at 3.0 V supply and around 25°C. The clock input of the 74AUP1G80, like the D input, is a

Schmitt-trigger input (it has two trigger voltages  $V_H$  and  $V_L$  and hysteresis). So, the input signal can be DC biased to  $(V_H+V_L)/2$  without damage to the device. For Vcc=3.0 V this is about  $V_{bias}$ =1.5 V.

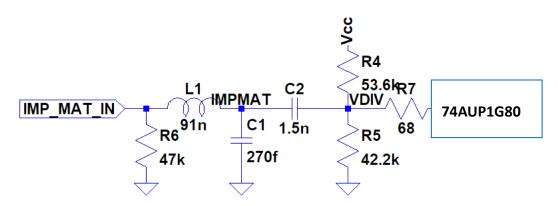

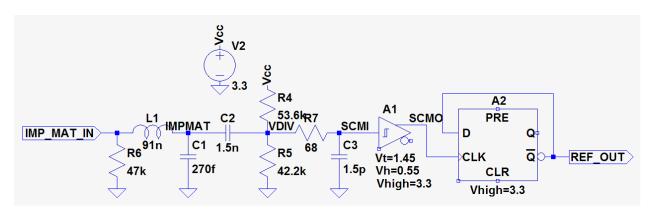

For neglectable effect on the impedance matching circuit, the coupling capacitor C2 can have a minimum value of 150 pF (100 times the input capacitance of the 74AUP1G80) and a maximum value of 1.5 nF (time constant limited), and the bias resistors R4 and R5 between 10 k $\Omega$  and 100 k $\Omega$  (same considerations). An additional protection resistor R7 of 68  $\Omega$  in series with the clock input is needed because the input voltages after the inevitable impedance matching can go considerably beyond the supply rails. According to the Keysight Advanced Design System (ADS)-impedance matching tool, the impedance matching can consist of a 91 nH series inductor L1 close to the source and a 270 fF parallel capacitor C1 close to the input of the device. In fact, this parallel capacitor can be manufactured using the stray capacitance of the PCB. The phase jitter contribution of the bias resistors is about 0.3 ps RMS for the 100 k $\Omega$  case (according to simulations). A circuit diagram of the impedance matching circuit is shown in Figure 3.2. The node "IMP\_MAT\_IN" is connected to the power splitter at the V<sub>i</sub> output of the directional coupler.

Figure 3.2: Impedance Matching & Bias Circuit before Pre-Divider

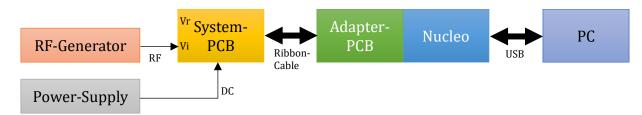

## 3.4 Integer-N PLL Frequency Synthesizer

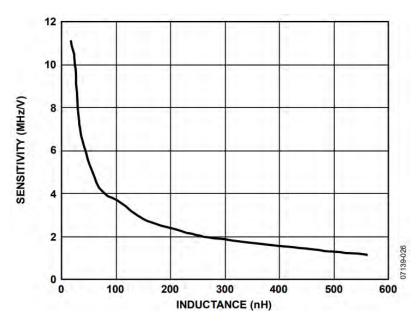

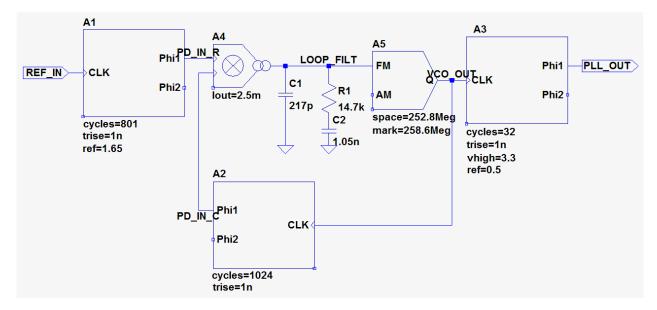

The purpose of the PLL Frequency Synthesizer is to generate the sample frequency for the ADC from the output signal of the pre-divider. It should be an integer-N device to avoid spurious frequencies in the output that might interfere with the under-sampling down-conversion. Furthermore, it should allow the generation of frequencies in the desired sample frequency range from UHF frequencies and allow software configuration of all important parameters. This narrows down the field of available PLL circuits considerably, as today most PLL ICs are either fractional-N or do not support the required input and output frequencies especially the additional A divider at the output is interesting in this case. The chosen Analog Devices ADF4360-9 [38] is a compromise, as it allows only 250 MHz maximum reference frequency (REF) what makes a pre-divider at this input necessary. The integrated voltage-controlled oscillator (VCO) supports frequencies between 65 and 400 MHz, and the device is configured via the SPI interface, which is common in modern microcontrollers such as the system processor.

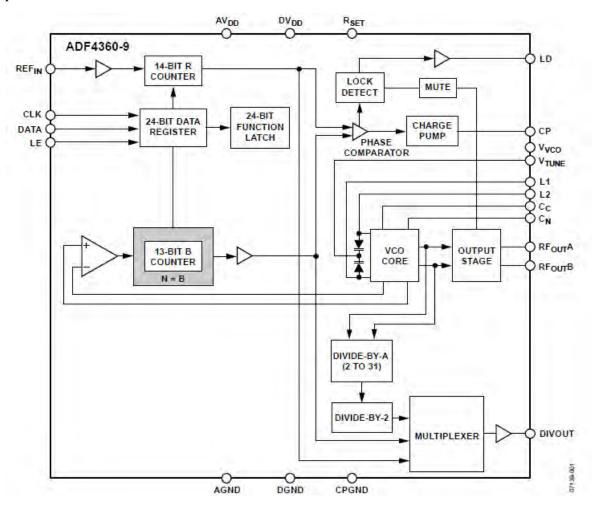

As shown in Figure 3.3, there are three main frequency dividers that can be programmed separately. The R counter divides the REF input frequency by values between 1 and 16383.

After that, it is fed into the phase frequency detector (PFD), that supports frequencies up to 8 MHz. The output of the VCO is divided by the B counter by values between 3 and 8191. The result is also fed into the PFD. The frequency of the VCO is also divided by the A counter that can assume values between 2 and 31. As the output of the A counter generally has a non-50% duty cycle, there exists a further divide-by-2 divider A<sub>2</sub> that can be activated if necessary to ensure 50% duty cycle. The output frequency f<sub>out</sub> for the system is taken from the A<sub>2</sub> divider. There are more options to configure this device, but these are the most important ones.

Figure 3.3: ADF4360-9 Functional Block Diagram [38]

Table 3.2 shows some useful first design values for the application in the under-sampling down-conversion system.

Table 3.2: Chosen values for ADF4360-9 frequency synthesizer and effect

| Value        | Setting 1 | Setting 2 | Unit | Equation   Info                                                                                 |

|--------------|-----------|-----------|------|-------------------------------------------------------------------------------------------------|

| $f_{PreDiv}$ | 400.0     | 400.0     | MHz  | Signal frequency at pre-divider input                                                           |

| fref         | 200.0     | 200.0     | MHz  | = f <sub>PreDiv</sub> / 2   Frequency at PLL input                                              |

| R            | 625       | 625       | -/-  | R-divider value of PLL                                                                          |

| $f_{PFD}$    | 320.0     | 320.0     | kHz  | = f <sub>REF</sub> / R   Frequency at PFD                                                       |

| В            | 798       | 799       | -/-  | B-divider of PLL (normally called N)                                                            |

| fvco         | 255.36    | 255.68    | MHz  | = Bf <sub>PFD</sub>   VCO output frequency                                                      |

| Α            | 8         | 16        | -/-  | A-divider value of PLL                                                                          |

| $A_2$        | 2         | 2         | -/-  | A2-divider for 50% duty cycle                                                                   |

| fout         | 15.96     | 7.99      | MHz  | = $f_{VCO}$ / (AA <sub>2</sub> ) = $f_s$   Sample frequency                                     |

| falias       | 1.0       | 0.5       | MHz  | = f <sub>ADC</sub> - f <sub>out</sub> FLOOR(f <sub>ADC</sub> / f <sub>out</sub> )   Alias freq. |

It would also be possible to derive the REF signal from a quartz, for example of 10 MHz. Then no pre-divider is necessary. But in case the input frequency of the analog-to-digital converter  $f_{ADC}$  changes, this translates directly to a higher relative error. For 5 MHz difference, the relative error is greater than 90%. So, it is advisable to derive  $f_{REF}$  via a pre-divider from  $f_{ADC}$ . This way the relative error stays constantly at the value shown in Table 3.2. This is because the relationship between the alias frequency  $f_{alias}$  (the signal generated in the digital domain by the under-sampling down-conversion) and the frequency that is assumed to be frequency-slot 2 of the FFT is fixed. This relationship will be analyzed in 3.4.1.

#### 3.4.1 Calculation of Good PLL Counter Values

To begin with, the equation (19) as stated earlier (repeated here for convenience) describes the relationship between the input frequency  $f_i$ , the sample frequency  $f_s$  and the resulting alias frequency  $f_a$ , where N is a positive integer that selects the corresponding alias:

$$f_a(N) = |f_i - f_s N| \tag{19}$$

This includes all aliases, the folded (inverted) as well as the non-inverted ones.

The inverted aliases are selected using (25):

$$f_a(N) = f_S N - f_i \tag{25}$$

As we are only interested in the non-inverted aliases, we can apply (26):

$$f_a(N) = f_i - f_s N \tag{26}$$

As we are converting the sampled signal using a fast fourier transform (FFT) algorithm, ideally the alias frequency falls directly within one of the bins of the FFT. This means that there must be at minimum an integer relationship W (samples per aliased wave) between  $f_s$  and  $f_a$  like shown in (27):

$$W = \frac{f_s}{f_a} \tag{27}$$

Ideally, W is equal to the FFT length, or 1/2 or 1/3 of it. Higher division ratios may result in reduced accuracy. As the FFT length is a power of 2 (in our case 32, but could be 64), W of 16, 32 and 64 are especially interesting.

We can easily express  $f_a$  depending on  $f_s$  and W (28):

$$f_a = \frac{f_s}{W} \tag{28}$$

Combining (26) with (28) to eliminate  $f_a$  this results in (29), that allows to calculate possible sample frequencies:

$$f_{\mathcal{S}} = \frac{f_i}{\frac{1}{W} + N} \tag{29}$$

As the sample frequency is generated by an integer-N phase-locked loop (PLL), it is interesting to know if it is possible to generate these sample frequencies exactly using an integer-N. As it turns out, it is, if the reference frequency  $f_r$  of the PLL is also derived from  $f_i$  (30):

$$f_r = \frac{f_i}{2} \tag{30}$$

The integer-n PLL equation was presented in (1), what is repeated here for convenience (just  $f_{VCO}$  was replaced by  $f_s$  already), with  $C_N$  being the n counter value and  $C_R$  being the reference counter value, both integer:

$$f_S = f_{VCO} = f_r \frac{c_N}{c_R} \tag{1}$$

Using (1), (29) and (30), the following expression (31) is found: