#### Universidade Federal da Bahia Escola Politécnica Departamento de Engenharia Elétrica Curso de Mestrado em Engenharia Elétrica CMEE-DEE-EP-UFBA

### Projeto em Circuito Integrado de uma Arquitetura Flexível de Neuroprocessador de Alto Desempenho para Redes Perceptron Multicamadas

#### Igor Dantas dos Santos Miranda

Orientadora: Prof.<sup>a</sup> Dr.<sup>a</sup> Ana Isabela Araújo Cunha

#### Dissertação de Mestrado

apresentada ao Programa de Pós-Graduação em Engenharia Elétrica da UFBA (área de concentração: Microeletrônica) como requisito parcial a obtenção do grau de Mestre em Engenharia Elétrica.

Número de ordem PPGEE: Salvador, BA, dezembro de 2009

#### Divisão de Serviços Técnicos Catalogação da publicação na fonte. UFBA / Biblioteca Central

Miranda, Igor Dantas dos Santos.

Projeto em Circuito Integrado de uma Arquitetura Flexível de Neuroprocessador de Alto Desempenho para Redes Perceptron Multicamadas / Igor Dantas dos Santos Miranda - Salvador, BA, 2009

84 p.

Orientadora: Prof.<sup>a</sup> Dr.<sup>a</sup> Ana Isabela Araújo Cunha

Dissertação (mestrado) - Universidade Federal da Bahia. Escola Politécnica. Programa de Pós-Graduação em Engenharia Elétrica.

BA/UF/ CDU

### Projeto em Circuito Integrado de uma Arquitetura Flexível de Neuroprocessador de Alto Desempenho para Redes Perceptron Multicamadas

### Igor Dantas dos Santos Miranda

|   | ssertação de Mestrado aprovada em 21 de dezembro de 2009 pela banca examinadora mposta pelos seguintes membros: |

|---|-----------------------------------------------------------------------------------------------------------------|

| _ |                                                                                                                 |

|   | Prof. <sup>a</sup> Dr. <sup>a</sup> Ana Isabela Araújo Cunha (orientadora) DEE/UFBA                             |

| _ | Prof. <sup>a</sup> Dr. <sup>a</sup> Luciana Martinez DEE/UFBA                                                   |

| - | Prof. Dr. Robson Nunes de Lima DEE/UFBA                                                                         |

| - | Prof. Dr. Tiago de Oliveira                                                                                     |

# Agradecimentos

- À minha mãe pelo apoio incondicional e incansável, ao meu pai pelos conselhos e exemplo de perseverança e à minha irmã, Iorrana, pelo companheirismo.

- À minha orientadora, professora Ana Isabela, pela orientação, compreensão e confiança. Suas contribuições e ações tiveram uma importância incontestável para a realização deste trabalho.

- Aos amigos pela compreensão da ausência e dos momentos de stress.

- Aos colegas do LSITEC-NE pelas críticas e sugestões.

- Ao LSITEC-NE por conceder acesso às ferramentas de projeto de circuitos integrados.

#### Resumo

As redes neurais artificiais continuam sendo uma importante ferramenta na solução de diversos problemas das ciências aplicadas, como biologia, medicina e engenharias. Dentre estes, existem sistemas com fortes requisitos de desempenho, como aqueles destinado ao reconhecimento de padrões de áudio e vídeo, que exigem arquiteturas de *hardware* dedicadas para suportar o processamento massivamente paralelo das redes neurais em alta velocidade.

Adicionalmente, com os novos desafios na integração dos sistemas, em que muitos blocos funcionais são colocados em um único chip, são solicitadas flexibilidade e reusabilidade dos *hardwares* para redes neurais, visando a implementação em ASIC. Neste trabalho é apresentado um *IP-Core* de uma arquitetura flexível de neuroprocessador de alto desempenho para o processamento de redes neurais do tipo *perceptron* multi-camadas para implementação em circuito integrado.

O número de unidades e de núcleos de processamento, a precisão e a quantidade de memória para os pesos são recursos de *hardware* ajustáveis durante a implementação. A topologia da rede, os valores dos pesos e a função de ativação são configuráveis durante a execução. O projeto lógico do neuroprocessador proposto é apresentado, além de um exemplo de layout para validação da viabilidade física do projeto, utilizando a tecnologia CMOS de 90nm.

Uma nova métrica de avaliação de desempenho é apresentada e utilizada na comparação do desempenho do neuroprocessador proposto com outros encontrados na literatura e disponíveis comercialmente.

**Palavras-chave**: Redes Neurais, Neuroprocessadores, Perceptron Multi-Camadas, ASIC.

### **Abstract**

Artificial Neural Networks have been an important tool to solve several problems in science, biology, medicine and engineering. Some of these systems present severe performance requirements. This is the case of the audio and video pattern recognition systems, which demand dedicated hardware architecture in order to support the massively parallel processing of the neural networks at high speeds.

Moreover, together with the new challenges in system integration, where a single chip comprises many functional blocks, features as flexibility and reusability are required by neural network hardwares that target ASIC implementation. This work presents an IP-Core of a flexible and high speed neuroprocessor architecture for computing multi-layered neural networks targeting integrated circuit implementation.

The number of processing elements and cores, the precision and the weight memory size are adjustable hardware resources available in the circuit implementation. The network topologies, the weight values and the activation function may be configured during the running phase. The neuroprocessor design flow is detailed throughout the work. A layout example has been built to validate the physical feasibility of the design, using CMOS 90 nm technology.

A new performance evaluation metric has been presented and has been used to compare the proposed neuroprocessor with some neurohardwares found in the literature and commercially available.

**Keywords**: Neural networks, Neuroprocessors, Multi-layers Perceptron, ASIC.

# Sumário

| Su | ımári  | 0             |                                   |  | i   |

|----|--------|---------------|-----------------------------------|--|-----|

| Li | sta de | Figura        | as                                |  | iii |

| Li | sta de | <b>Tabela</b> | as                                |  | v   |

| Li | sta de | e Símbo       | olos e Abreviaturas               |  | vii |

| 1  | Intr   | odução        |                                   |  | 1   |

| 2  | Har    | dware 1       | para Redes Neurais                |  | 5   |

|    | 2.1    | _             | s Neurais Artificiais             |  | 5   |

|    | 2.2    |               | iderações na Implementação de RNA |  | 8   |

|    | 2.3    |               | ificações de Hardware para RNA    |  | 9   |

|    | 2.4    |               | ilhos Relacionados                |  | 10  |

| 3  | Arq    |               | a do Neuroprocessador             |  | 15  |

|    | 3.1    |               | isitos                            |  | 15  |

|    | 3.2    |               | ssamento discreto das redes MLP   |  | 16  |

|    | 3.3    | Visão         | Geral da Arquitetura              |  | 16  |

|    | 3.4    | Protoc        | colo de Comunicação               |  | 19  |

|    | 3.5    | Descri        | rição do Kernel                   |  | 23  |

|    |        | 3.5.1         | Caminho de Dados                  |  | 23  |

|    |        | 3.5.2         | Unidade de Processamento          |  | 25  |

|    |        | 3.5.3         | Função de Ativação                |  | 28  |

|    |        | 3.5.4         | Arquitetura de Memória            |  | 29  |

|    |        | 3.5.5         | Unidade de Controle               |  | 34  |

|    | 3.6    | Virtua        | alização                          |  | 34  |

|    | 3.7    | Sumár         | rio                               |  | 35  |

| 4  | Proj   | eto em        | Circuito Integrado                |  | 39  |

|    | 4.1    | Metod         | dologia de Projeto                |  | 39  |

|    | 4.2    | Front-        | -end                              |  | 43  |

|    |        | 4.2.1         | Modelo de Referência              |  | 43  |

|    |        | 4.2.2         | Projeto Lógico                    |  | 46  |

|    |        | 4.2.3         | Verificação Funcional             |  | 52  |

|    |        | 4.2.4         | Síntese Lógica                    |  | 54  |

|                            | 4.2.5 Geração de Memórias                            |    |  |

|----------------------------|------------------------------------------------------|----|--|

| 5                          | Avaliação de Características Físicas e de Desempenho | 59 |  |

|                            | 5.1 Análises do Erro                                 | 59 |  |

|                            | 5.2 Análise de Desempenho                            | 60 |  |

|                            | 5.3 Características Físicas                          | 64 |  |

| 6                          | Conclusões                                           | 67 |  |

| Referências bibliográficas |                                                      |    |  |

| A                          | Código-fonte em Verilog da UP                        | 73 |  |

| В                          | Folha de Especificações de Bloco de Memória          | 77 |  |

# Lista de Figuras

| 2.1  | Neurônio Biológico [Haykin 1999]                                          | 5  |

|------|---------------------------------------------------------------------------|----|

| 2.2  | Componentes do Neurônio Artificial (Figura adaptada de [Omondi e Rajapaka |    |

|      | 2006])                                                                    | 6  |

| 2.3  | Exemplo de rede MLP de 3 camadas, com 4 entradas e 3 neurônios em         |    |

|      | cada camada (Figura adaptada de [Demuth et al. 2008])                     | 7  |

| 2.4  | Grupos de classificação de neurohardware segundo [Ienne 1997]             | 9  |

| 2.5  | Arquitetura BBA (Figura adaptada de [Ienne 1993])                         | 11 |

| 2.6  | Modelo do neurohardware (esquerda) e da UP (direita) apresentados por     |    |

|      | [Yun et al. 2002]                                                         | 11 |

| 2.7  | Esquema funcional do neurohardware apresentado por [Vitabile et al. 2005] | 12 |

| 2.8  | Esquema funcional do CogniMem [CogniMem 2008]                             | 13 |

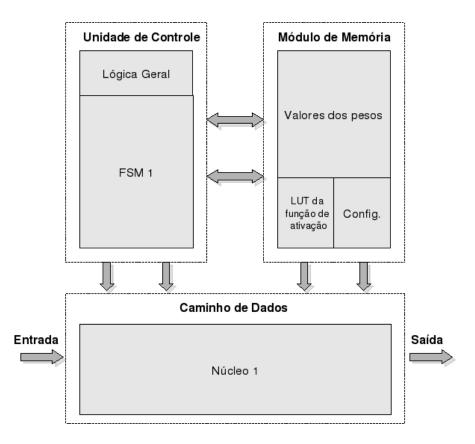

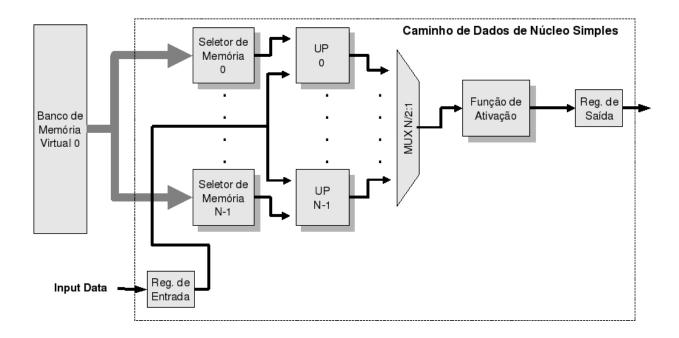

| 3.1  | Kernel de núcleo simples                                                  | 18 |

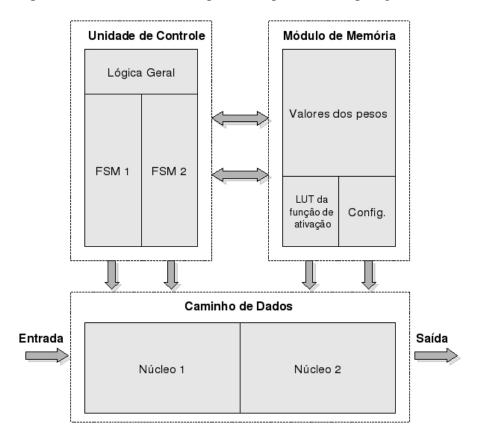

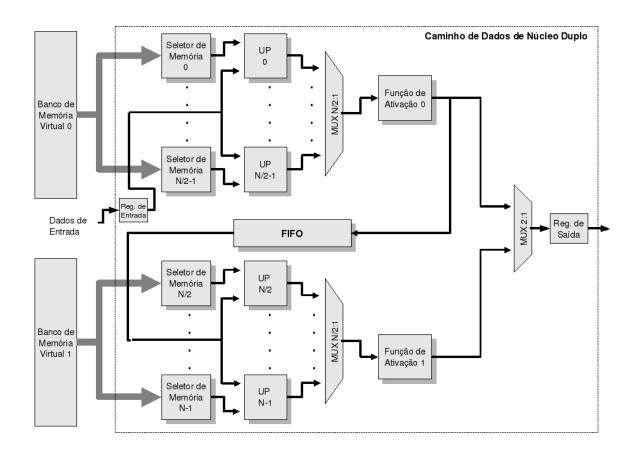

| 3.2  | Kernel de núcleo duplo                                                    | 19 |

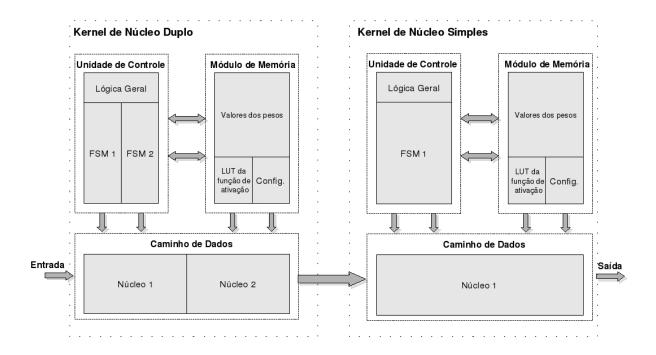

| 3.3  | Esquema para três camadas no modo desempenho                              | 20 |

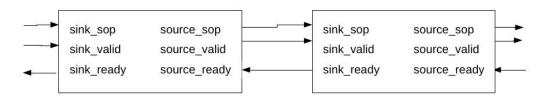

| 3.4  | Conexão entre blocos comunicantes                                         | 20 |

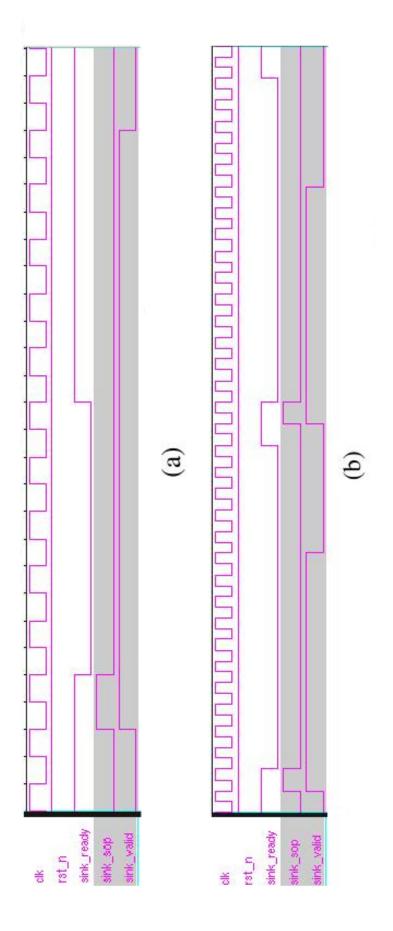

| 3.5  | (a) Transmissão simples (b) Dispositivo de recepção ocupado               | 22 |

| 3.6  | Caminho de Dados de Núcleo Simples                                        | 24 |

| 3.7  | Caminho de Dados de Núcleo Duplo                                          | 25 |

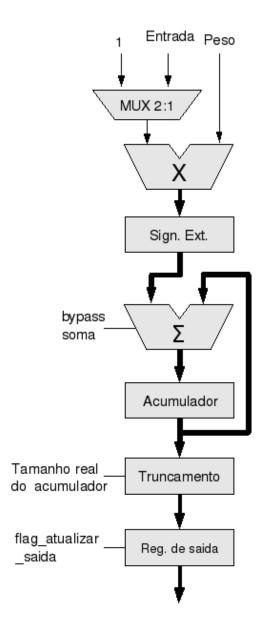

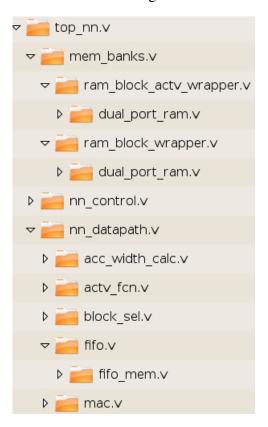

| 3.8  | Diagrama da Unidade de Processamento                                      | 26 |

| 3.9  | Esquema de truncamento na UP                                              | 27 |

| 3.10 |                                                                           | 31 |

| 3.11 | Atribuição de dados ao banco virtual                                      | 32 |

|      | Exemplo de configuração para diversas topologias de RNA                   | 33 |

| 3.13 | Arquitetura de memória incluindo LUT e configuração                       | 34 |

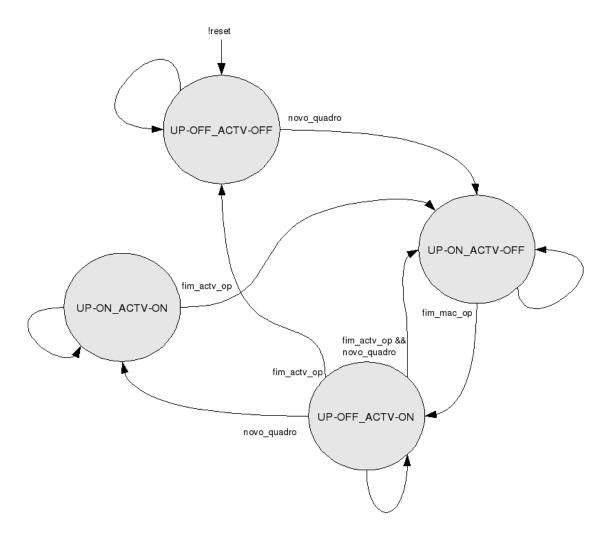

| 3.14 | Máquina de estados para um núcleo do caminho de dados                     | 36 |

| 3.15 | Esquema de virtualização                                                  | 37 |

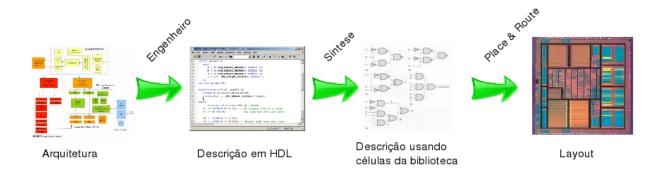

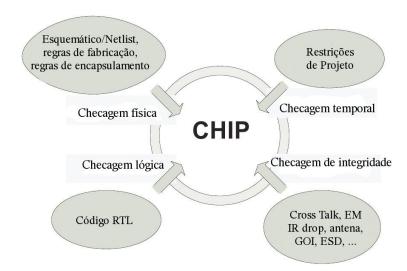

| 4.1  | Versão simplificada das etapas da metodologia de células padrões          | 40 |

| 4.2  | Verificações realizadas durante o desenvolvimento (Figura adaptada de     |    |

|      | [Xiu 2007])                                                               | 41 |

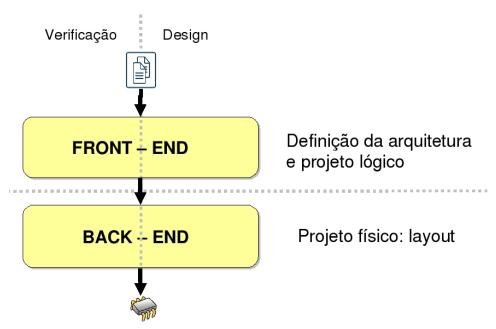

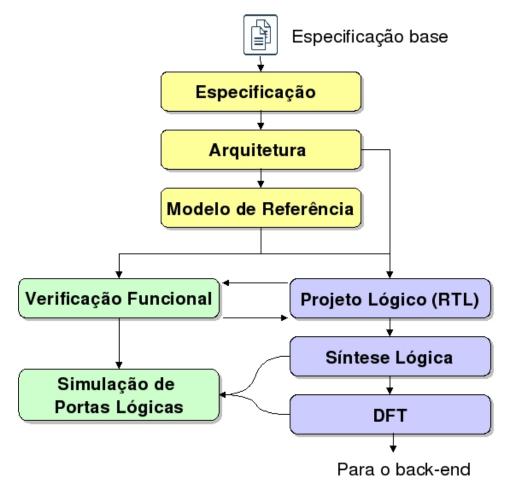

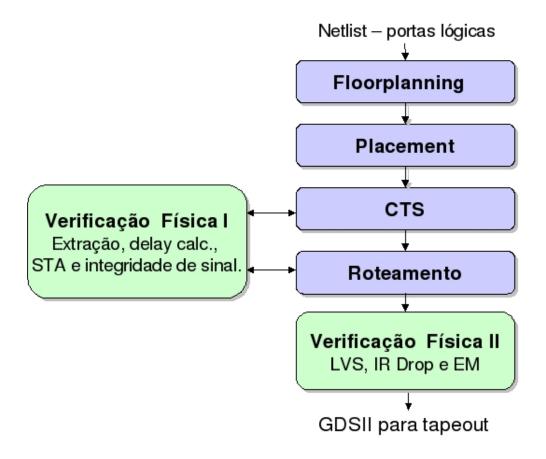

| 4.3  | Visão geral do fluxo de projeto                                           | 41 |

| 4.4  | Sub-etapas do front-end                                                   | 42 |

| 4.5  | Sub-etapas do back-end                                                    | 43 |

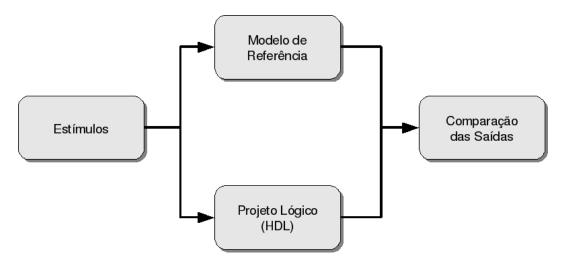

| 4.6  | Comparação entre modelo de referência e projeto lógico durante simulação  | 44 |

| 4.7  | Diagrama do modelo de referência                                          | 45 |

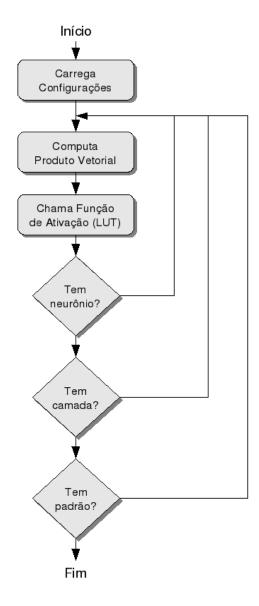

| 4.8  | Organização hierárquica do RTL                                            | 47 |

| 4.9  | Esquemático da UP                                                     | 49 |

|------|-----------------------------------------------------------------------|----|

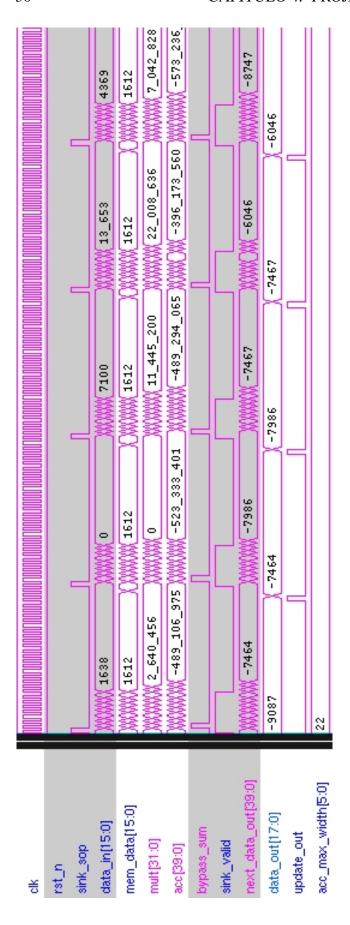

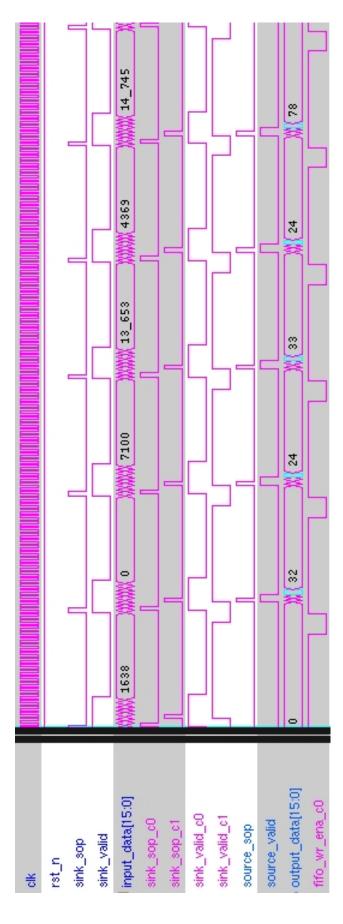

| 4.10 | Sinais do processamento na UP                                         | 50 |

| 4.11 | Envio de dados ao neuroprocessador                                    | 51 |

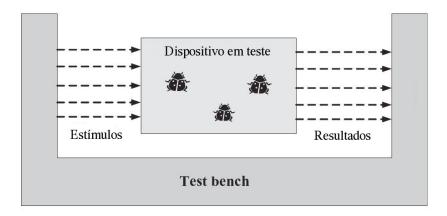

| 4.12 | Simulação do sistema com um testbench (Figura adaptada de [Xiu 2007]) | 52 |

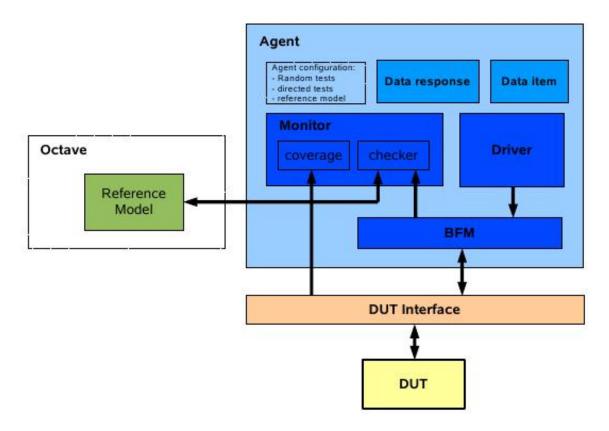

| 4.13 | Ambiente de Simulação do LVM                                          | 54 |

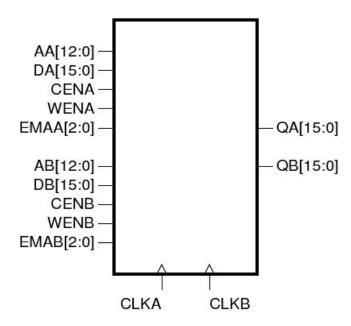

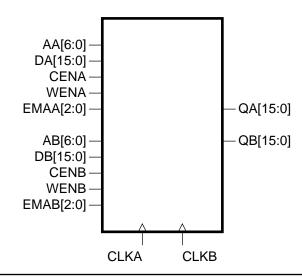

| 4.14 | Visão externa da memória gerada                                       | 56 |

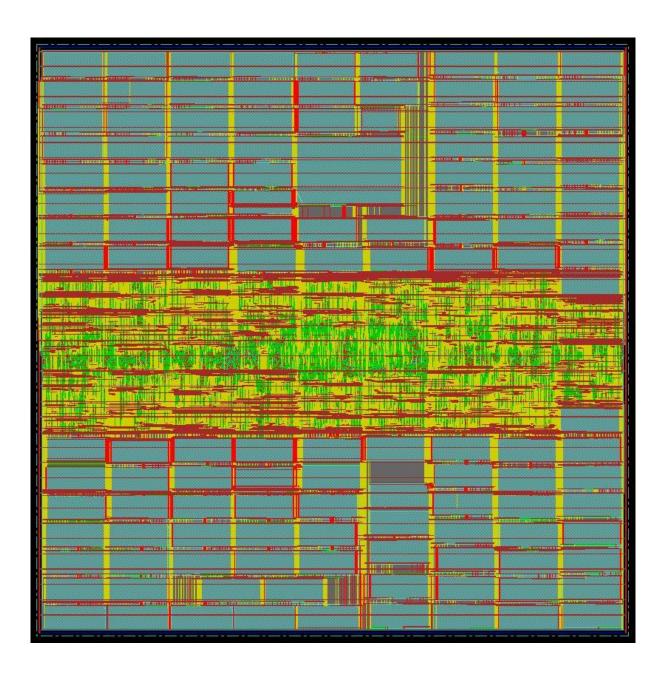

| 4.15 | Layout do neuroprocessador                                            | 58 |

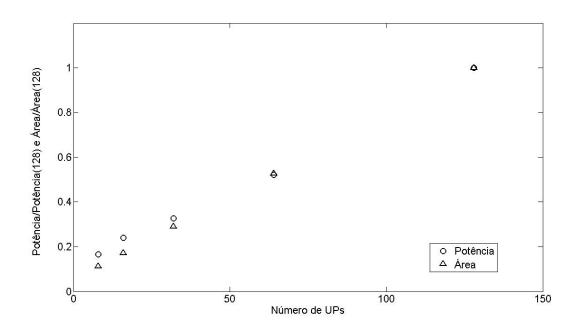

| 5.1  | Área e potência em função do número de UPs                            | 65 |

# Lista de Tabelas

| 3.1 | Sinais no protocolo de comunicação                                 | 21 |

|-----|--------------------------------------------------------------------|----|

| 3.2 | Registradores de configuração                                      | 35 |

| 3.3 | Sumário das propriedades do neuroprocessador                       | 37 |

| 4.1 | Resultados da Síntese                                              | 55 |

| 5.1 | Erro no Proben1 e no Matlab                                        | 60 |

| 5.2 | Erro introduzido com o cálculo em ponto fixo de 16 bits no RTL     | 60 |

| 5.3 | Análise de desempenho para simulações no modo desempenho           | 62 |

| 5.4 | Análise de desempenho para simulações no modo área com 8 UPs       | 63 |

| 5.5 | Comparações do neuroprocessador proposto com outros neurohardwares | 63 |

| 5.6 | Sínteses para diversos números de UPs                              | 64 |

| 5.7 | Resultados da síntese para maior frequência de operação suportada  | 64 |

### Lista de Símbolos e Abreviaturas

$E_C$  Erro percentual de classificação dos padrões

$E_Q$  Erro quadrático percentual

$n_Q$  Eficiência da paralelização

ADC Analog to Digital Converter

ASIC Application Specific Integrated Circuit

BBA Broadcast Bus Architecture

BFM Bus Functional Model

CI Circuito Integrado

CMOS Complementary Metal-Oxide-Semiconductor

CPCPU Conexões por Ciclo por Unidade de Processamento

CTS Clock Tree Synthesis

DAC Digital to Analog Converter

EDA Electronic Design Automation

FIFO First in First Out

FPGA Field Programmable Gate Array

FPNA Field Programmable Neural Array

FPNN Field Programmed Neural Network

HDL Hardware Description Language - Linguagem de Descrição de Hardware

IHM Interface humano máquina

IP Intellectual Property

LSB Least Significant Bit - Dígito Menos Significativo

LSITEC-NE Laboratório de Sistemas Integráveis Tecnológico Nordeste

LUT Look-up Table

LVM LSITEC-NE Verification Methodology - Metodologia de Verificação do LSITEC-

NE

MAC Unidade Multiplica-Acumula

MCPS Milhões de Conexões por Segundo

MIPS Milhões de Instruções Por Segundo

MLP Multi Layer Perceptron

MSB Most Significant Bit - Dígito Mais Significativo

RNA Rede Neural Artificial

RTL Register Transfer Level - Nível de Transferência de Registradores

SoC System-on-Chip

SRAM Static Random Access Memory

UP Unidade de Processamento

WTA Winner Takes All

# Capítulo 1

### Introdução

A natureza e a engenharia reservam uma infinidade de problemas que a modelagem matemática formal ainda não consegue resolver. Uma das alternativas para lidar com esses sistemas são as técnicas de inteligência artificial.

As redes neurais artificiais (RNA), que figuram entre as principais técnicas de inteligência artificial, tiveram suas primeiras publicações na década de 40, com o trabalho de McCulloch e Pitts [McCulloch e Pitts 1943]. No entanto, após a publicação do livro Perceptrons de Minsky e Papert em 1969 [Minsky e Papert 1969], no qual uma falsa ineficiência da técnica era citada, as pesquisas a respeito do assunto reduziram significativamente.

Somente cerca de dez anos depois, houve uma retomada dos trabalhos em RNA, com o advento do algoritmo de treinamento *backpropagation* [Rumelhart et al. 1986] e outros resultados teóricos importantes. Desde então, aumentaram vertiginosamente a quantidade e a variedade de aplicações, como relatado em [Kemsley et al. 1992] e [Widrow et al. 1994]. Outro fator motivador do renascimento das RNAs foi o aumento da capacidade de processamento dos computadores, fato contemporâneo aos avanços teóricos. Com o poder computacional do *hardware* da época já foi possível executar a grande quantidade de operações aritméticas requeridas em aplicações da técnica a problemas reais.

Com o passar dos anos, a revitalização do interesse nesse campo de pesquisa resultou na aparição de pesquisadores, recursos, conferências e jornais dedicados às redes neurais, além da inclusão do tema na formação básica oferecida por diversas escolas de engenharia e ciência da computação. Então, essa técnica se consolidou como uma importante ferramenta computacional, se tornando uma solução atrativa para inúmeros problemas do mundo real num amplo espectro de aplicações.

Atualmente, as redes neurais são muito utilizadas, segundo [Madani 2006], em problemas relacionados a: otimização; modelagem; sistemas decisórios; classificação de padrões; aproximação de funções não-lineares; mineração de dados.

Dentre essas, classificadores de padrões aplicados a sistemas de reconhecimento de padrões têm sido a utilização mais popular, sendo implementada com sucesso em várias pesquisas acadêmicas e produtos disponíveis no mercado [Bishop 1995]. Alguns exemplos de sistemas de reconhecimento de padrões nos quais as RNAs têm sido utilizadas são:

• manutenção preditiva e preventiva;

- monitoramento de condições;

- reconhecimento de caracteres;

- diagnóstico médico;

- reconhecimento de padrões sonoros;

- reconhecimento de voz;

- síntese da fala;

- reconhecimento de padrões de vídeo.

Diversos produtos finais utilizam ou podem utilizar *hardwares* capazes de processar reconhecimento de padrões. Dentre estes produtos, podemos citar câmeras fotográficas, robôs dotados de visão, identificadores de frutas em supermercados, controladores de acesso por voz e face, brinquedos e detectores de disparos de armas de fogo. No setor automobilístico, esses *hardwares* podem ser utilizados em sistemas de controle adaptativo de velocidade de cruzeiro de automóveis, onde um reconhecedor de padrões analisa a distância entre o automóvel e os veículos ao redor assim como a velocidade média destes para determinar a velocidade de cruzeiro. Também no setor automobilístico, padrões faciais, extraídos do movimento da cabeça e dos olhos, a taxa de piscadela e a média de tempo em que os olhos permanecem fechados, podem ser analisados utilizando um reconhecedor de padrões em sistemas de detecção de sonolência do motorista.

Devido à grande quantidade de informação manipulada, a aplicação de RNA na classificação de padrões de áudio ou vídeo requer soluções de *hardware* de alto desempenho, especialmente para sistemas de tempo real.

Implementação de RNAs em processadores de propósito geral apresentam um desempenho baixo devido à sua natureza seqüencial de operação, em contraste com a característica paralela das RNAs. Se implementadas em *hardware* paralelo, a característica paralela inerente das RNAs pode ser aproveitada para acelerar o processamento em muitas ordens de magnitude. Assim, a aceleração necessária para aplicações de tempo real de alto desempenho pode ser proporcionada por um conjunto de unidades de processamento simples, trabalhando juntas em paralelo.

Diante dessa necessidade, surgiu uma categoria de *hardware* dedicado ao processamento de RNAs, chamada *neurohardware*. *Neurohardware* é definido como qualquer sistema de *hardware* dedicado ao processamento de RNAs, dando suporte parcial ou total ao paralelismo da rede. O *neurohardware* pode ser projetado como um sistema composto de vários subsistemas, passando a ser chamado neurocomputador. Pode também ser projetado como um chip independente que faz todo o processamento neural, os chamados neuroprocessadores.

Vale ressaltar que, com o avanço das tecnologias de integração de circuitos, todos os blocos funcionais dos dispositivos de aplicação estão sendo implementados em um único chip, como em modems Zig-bee e leitores de mídia Blue-Ray. Em um nível de integração ainda maior, há o paradigma do System-on-Chip (SoC), em que um sistema eletrônico inteiro é integrado em uma pastilha de circuito integrado, reunindo diversos dispositivos de aplicação como ADCs, DACs, microprocessadores, modems, gestão de IHM, memória etc. Uma vez que, em geral, os *neurohardwares* são apenas um dos blocos funcionais do sistema, eles devem ser projetados visando a sua integração no dispositivo de aplicação. Por exemplo, para sistemas de reconhecimento de voz em Circuito Integrado (CI), a RNA

que faz a classificação dos padrões é apenas um dos blocos funcionais que compõe o processamento da informação, pois existe o pré-processamento da informação. Este CI, por sua vez, pode ser integrado em um SoC para um celular, que possuirá muitas outras funcionalidades além do reconhecimento de voz. Então, os neuroprocessares precisam ser desenvolvidos como blocos de Propriedade Intelectual (IP), que são módulos ASIC projetados para ter fácil integração e alta reusabilidade.

Por conta disso, novos requisitos surgem no projeto de neuroprocessadores visando integrá-los em dispositivos de aplicação ou SoCs. Esses neuroprocessadores devem suportar uma parametrização personalizada da arquitetura visando deixá-los compatíveis com os requisitos do sistema. Em outras palavras, um integrador de sistema deve ser capaz de ajustar os recursos do neuroprocessador para atender requisitos de área, desempenho ou consumo do dispositivo de aplicação. Além disso, o projeto deve oferecer o máximo de independência possível da tecnologia de fabricação. Estas propriedades proporcionarão reusabilidade e escalabilidade ao neuroprocessador.

Uma grande variedade de *neurohardwares* tem sido desenvolvida, como sumarizado em [Dias et al. 2003]. As principais diferenças estão no compromisso entre desempenho e área, no grau de paralelismo, na abordagem da arquitetura do sistema e no tipo de RNA suportada.

Muitos dos *neurohardwares* encontrados na literatura foram desenvolvidos como dispositivos independentes para ASIC ou FPGA, chips que apresentam somente a função de neuroprocessador, como em [Omondi e Rajapakse 2006] e [Dias et al. 2003]. Esse tipo de projeto, em geral, é incompatível com a flexibilidade necessária para integração em dispositivos de aplicação ou SoC.

Outros trabalhos, como [Vitabile et al. 2005], [Yun et al. 2002] e [Girau 2000], apresentaram arquiteturas flexíveis quanto à quantidade de recursos instanciados, tais como o número de Unidades de Processamento (UP) e a quantidade de memória, representando um avanço significativo na direção de IPs para neuroprocessadores.

Entretanto, duas dificuldades são encontradas na utilização dessas arquiteturas para integração com outros blocos em ASIC. A primeira dificuldade está no fato de todas essas arquiteturas terem sido projetadas para FPGA, desconsiderando aspectos importantes relacionados à implementação em ASIC. A segunda dificuldade é que nenhuma das arquiteturas flexíveis encontradas apresenta um esquema de reutilização do neuroprocessador para mais de uma topologia de RNA em tempo de execução. Nessas situações, o desempenho do sistema cai bruscamente devido à necessidade de mudança de pesos sinápticos na memória interna do neuroprocessador.

A partir do que foi discutido anteriormente, os objetivos do trabalho desenvolvido nesta dissertação são os seguintes:

- apresentar uma arquitetura de neuroprocessador para ser implementado como um IP de ASIC;

- desenvolver o projeto lógico do neuroprocessador e estudar sua viabilidade física através de um layout de validação;

- avaliar o desempenho do *hardware* proposto e realizar comparações com outros neuroprocessadores.

O neuroprocessador desenvolvido deve:

- apresentar flexibilidade na escolha dos recursos;

- considerar os aspectos de implementação em CI;

- ter desempenho compatível com os neuroprocessadores encontrados na literatura ou comercialmente;

- processar redes perceptron multicamadas.

A escolha do tipo de RNA, as redes Multi Layer Perceptron (MLP), foi realizada por conta desta ser a categoria mais utilizada na solução de diversos problemas práticos, como mencionado por [Samarasinghe 2006]. Dessa forma o neuroprocessador terá um amplo espectro de aplicação.

As contribuições deste trabalho são:

- a arquitetura de um neuroprocessador flexível de alto desempenho;

- uma métrica para avaliar o desempenho de neuroprocessadores, independente da freqüência de operação ou do número de UPs da implementação.

O trabalho apresentado nesta dissertação está distribuído em seis capítulos.

O segundo capítulo apresenta conceitos importantes no projeto de *neurohardware*. Trabalhos anteriores no desenvolvimento de *neurohardware* também são mostrados.

No terceiro capítulo a arquitetura do neuroprocessador proposto é apresentada em detalhes. As características do projeto são descritas e justificadas.

O capítulo quatro descreve a metodologia e o processo de desenvolvimento do *hardware*, passando pelo projeto lógico e pelo projeto físico.

O capítulo cinco mostra as avaliações das características físicas e de desempenho do neuroprocessador. Uma comparação dos resultados com outros neuroprocessadores encontrados na literatura ou comercialmente também é apresentada.

No último capítulo o trabalho é sumarizado e concluído. As principais contribuições dessa dissertação são discutidas.

### Capítulo 2

# Hardware para Redes Neurais

#### 2.1 Redes Neurais Artificiais

Classificadas como uma técnica de inteligência artificial, as RNAs, assim como outras técnicas desse segmento, são modelos matemáticos desenvolvidos visando imitar comportamentos inteligentes presentes na natureza.

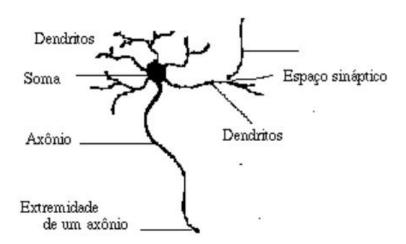

Dentro do cérebro, os neurônios biológicos são interligados entre si por intermédio de axônios e dentritos. Numa abordagem superficial, nós podemos considerar que estes são espécies de elementos condutores de eletricidade e podem, dessa forma, conduzir uma mensagem de um neurônio para o outro. Os dentritos representam as entradas do neurônio e o axônio a saída, como mostrado na figura 2.1.

Figura 2.1: Neurônio Biológico [Haykin 1999]

Um neurônio emite um sinal em função dos sinais provenientes de outros neurônios. No neurônio, existe uma integração dos sinais recebidos no decorrer do tempo, podendo ser visto como um somatório dos sinais de entrada.

Na conexão entre um axônio e um dentrito, existe um espaço vazio em que não há condução. Nessa região o sinal é transmitido através de substâncias químicas e depois

convertido novamente para impulsos elétricos. Abstraindo o processo químico, podemos considerar que essas conexões entre os axônios e os dentritos fazem a comunicação entre os neurônios, mas também excitam ou inibem os sinais na entrada de cada neurônio, ponderando suas entradas. Essas conexões ponderadas recebem o nome de sinapses. Mudar as ponderações pode significar aprender.

Esta simples unidade biológica de processamento se interliga aos outros 10 bilhões de neurônios, o que produz cerca de 16 trilhões de interconexões, dotando o cérebro humano com uma capacidade absurda de processamento e com o que chamamos de inteligência.

Partindo dessa idéia, mas com pretensões numéricas bem mais modestas, surgem as RNAs, onde modelos matemáticos simples são agrupados e interconectados visando um sistema com um pouco da capacidade de aprendizagem e generalização do cérebro humano. Os primeiros trabalhos em RNA datam de 1943, onde foi apresentado em [McCulloch e Pitts 1943] um modelo bem simples de neurônio e a exploração de suas possibilidades. O modelo de neurônio que se consolidou foi o perceptron [Rosenblatt 1962], cuja expressão é dada por:

$$y = \varphi\left(\sum_{i=1}^{N} w_i \cdot x_i + \Theta\right), \tag{2.1}$$

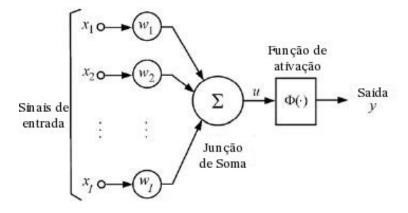

Onde N é o número de entradas,  $w_i$  os pesos sinápticos,  $x_i$  as entradas e  $\Theta$  é a polarização (ou limiar) do neurônio.  $\varphi$  é a função de ativação, que pode ser linear ou não-linear, dependendo do sistema que se deseja modelar. Diversas funções podem ser usadas como função de ativação, podendo ser encontradas em [Haykin 1999]. A figura 2.2 mostra os componentes básicos de um neurônio artificial.

Figura 2.2: Componentes do Neurônio Artificial (Figura adaptada de [Omondi e Rajapakse 2006])

Estabelecido o modelo matemático dos neurônios, basta interconectá-los para termos um comportamento inteligente em pequena escala, com características similares às do cérebro humano. A um grupo destas unidades matemáticas interconectadas dá-se o

nome de RNA. As diversas possibilidades de conexão dão origem às várias categorias de RNA, dentre as quais se destacam as redes perceptron, as redes MLP, os mapas autoorganizáveis e as redes recorrentes. Os modelos dos neurônios também podem mudar com categoria de RNA. O avanço da pesquisa em RNA seguiu em direção à aplicação e não mais ao modelo de funcionamento do cérebro, trazendo categorias voltadas às aplicações específicas e já sem nenhum vínculo com os sistemas biológicos. A definição de RNA dada por [Haykin 1999] faz com que mesmo com modelos distantes das redes biológicas, ainda existam similaridades que as incluam no mesmo grupo.

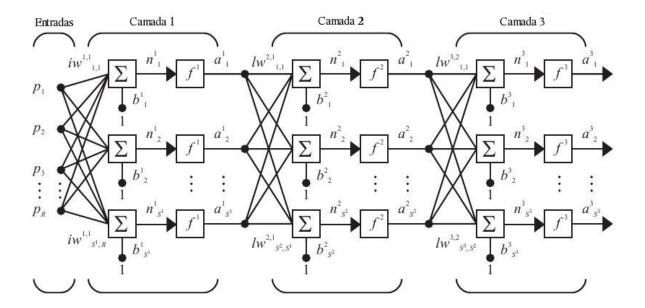

Como mencionado anteriormente, segundo [Samarasinghe 2006], as redes MLP são as mais conhecidas e utilizadas e, por conta disso, foram adotadas nesse trabalho. Nas redes MLP os neurônios são organizados em camadas, em que existem conexões de um neurônio de uma camada com os da camada posterior como mostrado na figura 2.3. As redes perceptron, constituídas de um ou mais neurônios em uma única camada, podem ser vistas como um caso particular das redes MLP.

Figura 2.3: Exemplo de rede MLP de 3 camadas, com 4 entradas e 3 neurônios em cada camada (Figura adaptada de [Demuth et al. 2008])

Fazendo uma generalização da equação 2.1, a equação que representa o processamento de cada camada da rede MLP é dado pela equação 2.2.

$$y_k^c = \varphi\left(\sum_{i=1}^M w_i^c \cdot y_i^{c-1} + \Theta_k\right), k = 1...G$$

(2.2)

Onde M é o número de nós da camada anterior, G é o número de nós da camada atual, o índice c representa a camada,  $y_i^{c-1}$  são as saídas da camada anterior e  $y_k^c$  são as saídas da camada atual.

O algoritmo backpropagation foi o principal precursor das técnicas de treinamento

das RNAs, permitindo a aprendizagem através de exemplos. Desde então, diversos outros algoritmos de treinamento surgiram e são encontrados na literatura, mas esse tópico foge ao escopo deste trabalho.

#### 2.2 Considerações na Implementação de RNA

O projeto de *neurohardware* necessita de abordagens especiais se comparado ao projeto de processadores baseados na arquitetura von Neumann. A principal razão disso é a característica de processamento paralelo, inerente ao conceito das redes neurais. As RNAs podem ser processadas seqüencialmente, porém, em aplicações restritivas com relação ao desempenho, é útil se utilizar do fato de que os dados têm pouca dependência de cálculos anteriores para acelerar a execução.

A primeira questão a ser considerada no projeto está relacionada à escolha entre implementação analógica ou digital. Implementações analógicas têm vantagens sobre as digitais com relação à área, pois os neurônios podem ser implementados com apenas alguns transistores e os pesos sinápticos associados às razões de aspectos dos transistores. No entanto, muitas desvantagens aparecem dentre as quais podem ser citadas a falta de programabilidade, ausência de escalabilidade, baixa imunidade a ruído e a perda de precisão dos pesos devido às incertezas do processo de fabricação [Ienne 1993]. A flexibilidade é um fator essencial no projeto de um neuroprocessador, levando imediatamente à escolha de implementações digitais.

Definida a implementação como digital, os principais aspectos que precisam ser considerados durante a elaboração da arquitetura são o grau de paralelismo, a escalabilidade do *hardware*, a portabilidade entre tecnologias, o armazenamento dos pesos, a virtualização, a precisão e o compromisso entre desempenho e área [Omondi e Rajapakse 2006].

Há vários graus de paralelismo que podem ser considerados: de bit; de neurônio; de camada; de padrões de entrada [Omondi e Rajapakse 2006]. O paralelismo de bit indica que vários bits podem ser processados de uma só vez, como em uma operação aritmética. Processar neurônios, camadas ou padrões diferentes simultaneamente confere paralelismo de neurônio, camada ou de padrões de entrada, respectivamente. Em geral, os paralelismos de bits e neurônios são sempre adotados.

A escalabilidade é a característica do projeto de aumentar os recursos sem prejudicar o funcionamento. Essa é uma característica essencial para arquiteturas que precisam fornecer flexibilidade para adaptar o *hardware* à aplicação [Ienne 1993]. A virtualização e a escalabilidade estão intimamente ligadas, pois quando o número de UPs do *neurohardware* é menor que o número de neurônios da rede, deve haver reuso de recursos. A este reuso de recursos se dá o nome de virtualização [Ienne 1993]. Em muitos casos a escalabilidade do sistema é feita através da virtualização.

A precisão e o compromisso entre área e desempenho são questões comuns encontradas na maioria dos projetos de ASIC digital. Em geral, aumentar o poder de processamento ou a precisão implica no aumento da área e vice-versa [Xiu 2007]. Nos neuroprocessadores este compromisso está relacionado basicamente à quantidade de UPs, enquanto que a questão da precisão relaciona-se com a resolução dos dados e dos pesos.

#### 2.3 Classificações de Hardware para RNA

Como mencionado no capítulo 1, existe uma quantidade considerável de trabalhos publicados acerca da implementação de *hardware* para RNAs. Diversas publicações propuseram classificações para os *neurohardwares* como em [Heemskerk 1995], [Ienne 1997] e [Lindsey e Lindblad 1998], descrevendo métodos próprios de categorização. Devido aos diversos aspectos de implementação, como citado na seção 2.2, e à variedade de técnicas enquadradas como RNAs, criar categorias homogêneas e critérios bem definidos não é uma tarefa simples.

Em geral, a principal forma de classificação dos *neurohardwares* é baseada no tipo de circuito que os implementa. O projeto pode conter circuitos analógicos, digitais ou ambos, resultando nas categorias de *neurohardwares* analógicos, digitais ou híbridos, respectivamente. Como os *neurohardwares* digitais possuem muito mais flexibilidade em termos de configuração e arquitetura que os analógicos, a maioria das outras classificações enquadram somente os digitais.

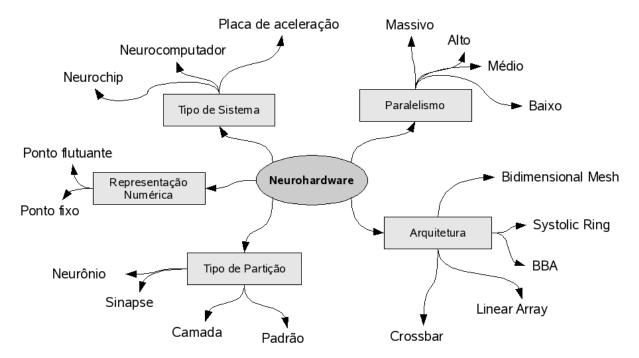

A respeito dessa classificação, [Ienne 1997] apresenta a categorização para *neurohardwares* digitais mais abrangente em relação aos demais trabalhos pesquisados. As categorias sugeridas por [Ienne 1997] são: tipo de sistema; grau de paralelismo; representação numérica; tipo de comunicação entre as UPs; tipo de partição da rede. A figura 2.4 mostra uma visão geral deste sistema de classificação de *neurohardware*

Figura 2.4: Grupos de classificação de neurohardware segundo [Ienne 1997]

Na classificação do tipo do sistema, o *neurohardware* pode ser enquadrado como neuroprocessador (ou neurochip), neurocomputador ou placa de aceleração. Os neurocomputadores são CIs que possuem toda a lógica necessária para o processamento da RNA,

podendo ser usados tanto como um dispositivo independente em uma placa de aplicação ou como um periférico de um microprocessador. Em neurocomputadores e placas de aceleração, neuroprocessadores ou processadores de propósito gerais são utilizados para compor o sistema que processa a RNA. O termo neuroprocessador, ao invés de neurochip, foi adotado durante este trabalho, para evitar confusão com neurochips de redes de comunicação de dados.

O grau de paralelismo é medido através do número de UPs do sistema. [Ienne 1997] propõem uma transição superposta entre as categorias, condizente com a subjetividade da divisão. As categorias para o grau de paralelismo são baixo (2 a 16 UPs), médio (8 a 128 UPs), alto (64 a 2048 UPs) e massivo (maior que 1024).

A classificação pela representação numérica está relacionada com o tipo de operação adotada, que pode ser em ponto fixo ou ponto flutuante.

O tipo de partição da rede define como as RNAs são divididas para executar o processamento. O processamento pode ocorrer neurônio a neurônio, sinapse a sinapse, camada a camada, padrão a padrão etc. Em *neurohardwares* de alto desempenho, mais de um padrão pode ser processado em paralelo.

Por fim, a classificação por tipo de comunicação entre as UPs é, em linhas gerais, a distinção dos *hardwares* com relação às suas arquiteturas. *Bidmensional Mesh*, *Systolic Ring*, *Broadcast Bus*, *Linear Array* e *Crossbar* são as arquiteturas sugeridas em [Ienne 1997], onde o detalhamento de cada uma delas pode ser encontrado.

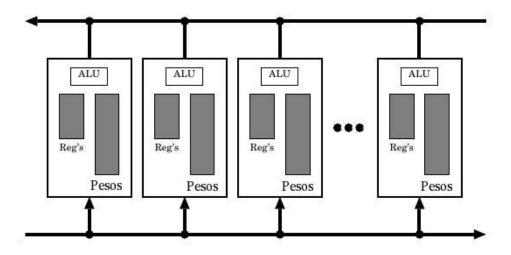

[Ienne 1997] destaca a arquitetura *Broadcast Bus* (BBA) como a mais indicada quando modularidade e versatilidade são desejadas, como no caso do neuroprocesssador proposto. No BBA, todos os dados de entrada ou proveniente de camadas anteriores são enviados simultaneamente para todas as UPs disponíveis. As UPs efetuam a operação de multiplicar e acumular a cada novo dado, utilizando um peso sináptico armazenado em uma memória interna em cada UP. Uma função de ativação, também interna em cada UP, é então aplicada ao resultado da acumulação ao final da operação. A figura 2.5 mostra o diagrama da BBA.

À medida que novos *neurohardwares* surgiram, as categorias para classificação baseadas na arquitetura passaram a perder a generalização. Outra deficiência das classificações apresentadas por [Ienne 1997] é o fato de que nenhuma categoriza os *hardwares* pelo tipo de RNA processada. Em alguns casos, diferentes tipos de RNAs podem levar a *hardwares* sem nenhuma similaridade.

#### 2.4 Trabalhos Relacionados

*Neurohardwares* com requisitos de projeto similares aos apresentados no capítulo 1 foram encontrados em [Vitabile et al. 2005], [Yun et al. 2002] e [Girau 2000]. Nestes três trabalhos, flexibilidade, configurabilidade e escalabilidade são as principais características dos *neurohardwares*, assim como esperado para o neuroprocessador proposto.

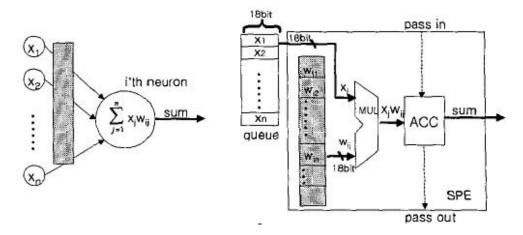

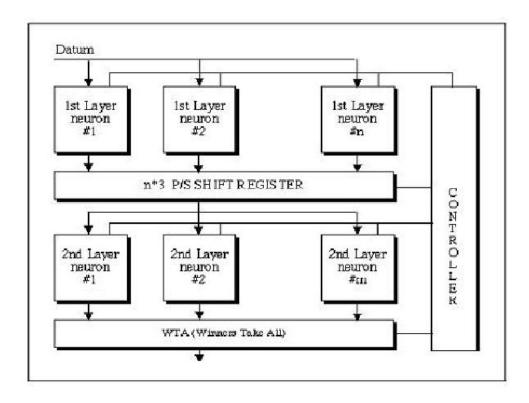

Outra semelhança entre esses três *neurohardwares* é que todos utilizam a arquitetura BBA para a comunicação dos dados internos, como no diagrama da figura 2.5. As figuras 2.7 e 2.6 mostram os diagramas dos *neurohardwares* apresentados em [Vitabile et al. 2005] e [Yun et al. 2002], respectivamente.

Figura 2.5: Arquitetura BBA (Figura adaptada de [Ienne 1993])

Entretanto, os três neuroprocessadores referidos foram projetados para implementação em FPGA, não atendendo por completo os requisitos estabelecidos no capítulo 1, principalmente no que se refere à implementação em ASIC. O principal problema causado pelo fato do projeto ser direcionar à tecnologia de FPGA está no armazenamento dos pesos dentro da UP, tal como na BBA. Este armazenamento disperso, necessário devido à estrutura interna da maioria dos FPGAs, pode reduzir a configurabilidade e dificultar o layout, como será discutido com mais detalhes adiante neste documento. Alguns FPGAs apresentam memória interna separada da lógica, porém não eliminam os problemas por conta das poucas portas de escrita e leitura.

Figura 2.6: Modelo do neurohardware (esquerda) e da UP (direita) apresentados por [Yun et al. 2002]

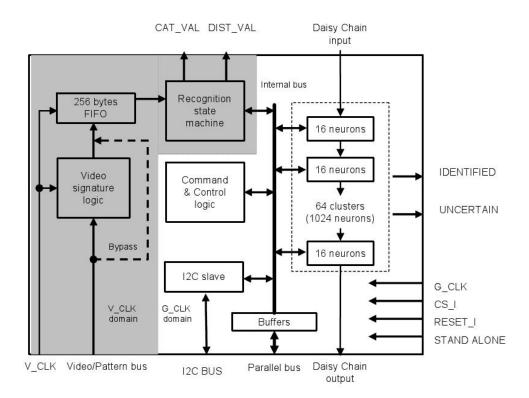

Também foram encontrados neuroprocessadores no mercado, dentre os quais destacase o CogniMem [CogniMem 2008]. Este destina-se ao reconhecimento de padrões de

Figura 2.7: Esquema funcional do neurohardware apresentado por [Vitabile et al. 2005]

vídeo e foi implementado com uma arquitetura específica em ASIC. A figura 2.8 mostra o diagrama funcional do CogniMem.

Figura 2.8: Esquema funcional do CogniMem [CogniMem 2008]

# Capítulo 3

# Arquitetura do Neuroprocessador

### 3.1 Requisitos

O neuroprocessador descrito no decorrer deste capítulo foi projetado como um módulo de propriedade intelectual em tecnologia ASIC, visando apresentar flexibilidade ao integrador de sistemas no que concerne ao compromisso entre desempenho e área. Este hardware foi desenvolvido para processar RNAs pré-treinadas, ou seja, sem suporte à aprendizagem.

Outro objetivo do projeto é suportar o reuso do sistema para processar mais de uma RNA com topologias distintas, modificando o número de camadas e neurônios em tempo de execução. Com esta característica, o neuroprocessador também pode ser implementado como um chip independente.

Para atender aos requisitos citados acima, têm sido adotadas as seguintes funcionalidades para o sistema:

- número ajustável de UPs;

- número ajustável de camadas processadas em paralelo;

- função de ativação implementada em Look-up Table (LUT);

- processamento em etapas (virtualização);

- tamanho ajustável da memória de pesos;

- tamanho ajustável da memória da LUT;

- precisões ajustáveis;

- topologia de RNA reconfigurável em tempo de execução;

- mudança dos pesos sinápticos e da LUT em tempo de execução para processar RNA diferentes.

Adicionalmente, foi incorporada como requisito a possibilidade de utilizar a comunicação com o ambiente externo palavra a palavra, de modo que o sistema seja independente da topologia de RNA e tenha um número factível de pinos de entrada. Isso também garante a compatibilidade com a maioria dos sistemas de processamento de sinais nos quais suas fontes de dados são conversores analógico-digital.

Com base nestes requisitos e com o exposto na seção 2.3, a arquitetura BBA foi utilizada como base para a concepção da arquitetura do neuroprocessador proposto. Ainda segundo a seção 2.3, o neurohardware aqui apresentado pode ser classificado como um

sistema do tipo neurochip (*IP core*), com tipo de partição por neurônio e camada, com paralelismo ajustável, representação numérica em ponto fixo e arquitetura BBA.

#### 3.2 Processamento discreto das redes MLP

O cálculo para RNAs do tipo MLP foi apresentado no capítulo 2 através da equação 2.2. Para uma RNA de uma camada, podemos separar o argumento da função de ativação, como em 3.1 e 3.2.

$$u_k = \sum_{i=1}^{M} w_i^c \cdot x_j^{c-1} \tag{3.1}$$

$$y_k^c = \varphi(u_k + \Theta_k) \tag{3.2}$$

Dessa forma, o cálculo de 2.2 pode ser realizado em duas etapas, o produto vetorial e a função de ativação. Considerando uma implementação discreta, teremos primeiro multiplicações e um somatório com valores em ponto fixo. A precisão da representação dos dados e dos pesos vai inserir o primeiro estágio de erro. A operação por si só pode não inserir erro, caso haja bits suficientes na variável que armazena o resultado do somatório.

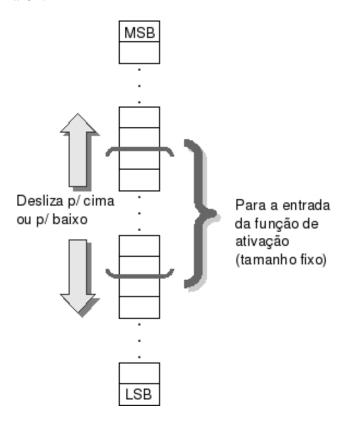

Entretanto, se tivermos a função de ativação implementada com uma LUT, teremos dois momentos em que ocorre perda de precisão. O primeiro é na entrada da função de ativação onde se tem um número limitado de dados armazenados, para não haver uma memória de armazenamento muito grande. Isto implica em truncar a saída do somatório, perdendo precisão. Como temos também uma precisão limitada nos valores armazenados na LUT, a saída da função de ativação vai inserir mais um erro, o de quantização.

A representação em ponto fixo utilizada para representar os dados, os pesos sinápticos, as entradas e as saídas foi o complemento de dois. Esta representação é normalmente adotada pelas ferramentas de EDA durante a interpretação do código HDL, pois resulta em menor hardware para operações aritméticas.

Para RNAs de duas ou mais camadas, as saídas das camadas intermediárias vão para as próximas camadas até chegar à saída. Isso significa que o ruído de quantização aumenta exponencialmente a cada camada, pois a cada vez que uma função de ativação é utilizada, duas novas fontes de erros aparecem no processamento.

Porém, nem sempre o erro final da RNA afeta o resultado, dependendo do tipo de classificação final adotado, como o *Winner Takes All* (WTA) [Prechelt 1994].

No projeto do neuroprocessador, cuidados foram tomados com o truncamento e com a discretização da função de ativação de modo a reduzir o erro final, conforme descrito no capítulo 4.

#### 3.3 Visão Geral da Arquitetura

A flexibilidade do neuroprocessador proposto está relacionada com as suas características ajustáveis. Tais características podem ser divididas nos grupos das características parametrizáveis e das características configuráveis. As características parametrizáveis

estão relacionadas com a definição da quantidade de recurso utilizada em uma implementação do neuroprocessador. As características configuráveis definem como os recursos são utilizados.

A quantidade e a disposição das UPs, as precisões dos dados e pesos sinápticos, o tamanho da memória de pesos e o tamanho da LUT devem ser escolhidos durante a etapa de integração lógica do sistema, antes do mapeamento tecnológico. Estas são características parametrizáveis.

Por outro lado, no conjunto das características configuráveis estão as configurações relativas à topologia da RNA processada, como os valores dos pesos sinápticos e memória com a função de ativação, que devem ser ajustados após a implementação em uma tecnologia de circuito integrado, durante a utilização da rede. Estas e outras configurações serão detalhadas no decorrer do capítulo.

Durante a fase de parametrização do neuroprocessador, ainda no projeto lógico, dois modos de implementação podem ser escolhidos, dependendo dos requisitos da aplicação. Estes modos são:

- modo desempenho;

- modo área.

No modo Desempenho, como o nome sugere, o desempenho é priorizado, utilizando-se um número de UPs suficiente para processar todos os nós da rede da aplicação simultaneamente. No modo Área, visando reduzir a área, o número de UPs é inferior ao número de nós da rede, o que requer processamento seqüencial.

Em ambos os casos, todas as UPs são encerradas em um bloco principal, aqui chamado de *kernel* que, dependendo do modo, pode processar partes de uma rede ou toda a rede simultaneamente. O *kernel* é composto pelos sub-blocos Unidade de Controle, Módulo de Memória e Caminho de Dados. Uma vez que o processamento de RNAs requer um alto grau de paralelismo, o Caminho de Dados e o Módulo de Memórias têm suas capacidades distribuídas em pequenas unidades que funcionam paralelamente, provendo para cada nó da rede (um neurônio) uma unidade aritmética e o armazenamento dos pesos sinápticos referentes. O *kernel* do neuroprocessador é ilustrado na figura 3.1.

Utilizando a terminologia de descrição de *neurohardware* chamada Field Programmable Neural Array (FPNA), proposta por [Girau 2000], uma subunidade de memória e uma subunidade do caminho de dados podem ser vistos como um nó (neurônio) que realiza um produto vetorial completo e cujos recursos são disponibilizados para os outros nós da rede. Os nós, unidades de função de ativação e conexões virtuais (providos pela unidade de controle), todos juntos, consistem no conjunto completo de recursos necessário para a implementação de uma FPNA. Quando apropriadamente configurado o *hardware* torna-se uma Field Programmed Neural Network (FPNN) [Girau 2000], processando uma aplicação e topologias de RNAs específicas.

Porém, esta arquitetura não é completamente compatível com a definição de FPNA uma vez que a conectividade entre os nós é limitada às camadas consecutivas e os recursos do nó só são disponibilizados de maneira temporizada. Consequentemente, nem conexões recorrentes nem conexões paralelas são suportadas entre os neurônios.

Para implementação orientada ao desempenho, existem três possíveis estruturas que podem ser utilizadas, dependendo se o *hardware* deverá suportar no máximo uma, duas

Figura 3.1: Kernel de núcleo simples

ou três camadas. Para RNAs com mais de três camadas, a arquitetura apresenta um baixo desempenho e, portanto, não foi implementada para tal. Topologias de mais de 3 camadas também não são muito encontradas na literatura. Para redes com uma camada, um *kernel* com apenas um núcleo é utilizado, como mostrado na figura 3.1. Neste são processados todos os nós da camada de saída de forma paralela.

Para redes de duas camadas, o *hardware* pode ser instanciado com uma estrutura de núcleo duplo. Dessa forma, cada camada é atribuída a um núcleo diferente, mantendo o processamento paralelo com relação às camadas e aos padrões de entrada. A camada oculta é processada pelo primeiro núcleo e a camada de saída pelo segundo. O *kernel* com núcleo duplo é ilustrado na figura 3.2. Após a implementação, as UPs não podem mais ser realocadas entre os núcleos.

Para redes de três camadas são utilizados dois *kernels*, de tal forma que um de núcleo duplo é concatenado a um de núcleo simples. As duas camadas ocultas são processadas no *kernel* de núcleo duplo e a camada de saída no *kernel* de núcleo simples. A figura 3.3 mostra o esquema para três camadas no modo desempenho.

Ainda com relação ao modo Desempenho, o número de UPs por núcleo tem que ser o suficiente para processar o máximo número de nós em cada camada nas topologias suportadas.

A unidade de controle do kernel é responsável por controlar o fluxo de dados internos.

19

Em casos de núcleo duplo, a unidade de controle também possui duas FSM, para controlar os núcleos, e uma lógica geral, que controla o fluxo de dados entres núcleos. Neuroprocessadores instanciados para três camadas suportam também duas e uma camada, assim como neuroprocessadores instanciados para duas processam topologias de uma camada.

Figura 3.2: Kernel de núcleo duplo

No caso de projetos que visam otimizar a área, o neuroprocessador pode ser implementado com apenas um *kernel* de núcleo simples e um número pequeno de UPs, para qualquer número de camadas e de neurônios. Nesta implementação, o número máximo de neurônios em uma camada é geralmente maior que o número de UPs disponíveis, requerendo virtualização para processar seqüencialmente as operações relacionadas a cada camada. Além do *kernel*, algumas memórias e uma máquina de estados também são utilizadas para fazer o processamento seqüencial. A arquitetura e o funcionamento do uso da virtualização para o processamento seqüencial são elucidados na secção 3.6.

# 3.4 Protocolo de Comunicação

Um protocolo de comunicação de dados único está sendo utilizado em diversos níveis hierárquicos do sistema. As UPs, os núcleos dos caminhos de dados, os *kernels* e mesmo o neuroprocessador utilizam este protocolo para receber e enviar dados.

Figura 3.3: Esquema para três camadas no modo desempenho

Este protocolo é uma versão simplificada do protocolo utilizado pela Altera Corp. em diversos dos seus blocos de propriedade intelectual, o Avalon Streaming Interface [Altera 2009].

Todos os módulos envolvidos na comunicação devem possuir duas portas, uma de entrada e outra de saída. A comunicação sempre é feita ponto a ponto, com a porta de saída de um módulo conectada à porta de entrada do módulo seguinte. Os dados são transmitidos quadro a quadro, em que cada quadro pode ter tamanho variável. A figura 3.4 ilustra a conexão entre dois blocos na comunicação.

Figura 3.4: Conexão entre blocos comunicantes

Três situações são possíveis durante uma comunicação:

- início do quadro de dados;

- trasmissão do dado;

- dispositivo receptor pronto para receber.

O início de um novo quadro de dados é sempre marcado com um pulso do sinal 'sop'

21

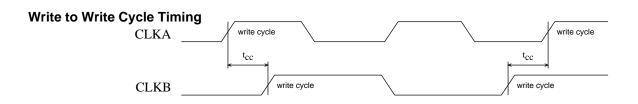

(start of operation). Quando um dado está sendo transmitido, o sinal 'valid' permanece alto. O final de um quadro de dados é marcado pela descida do sinal 'valid' ou pelo começo de um novo quadro. O sinal 'ready' alto indica que o receptor está pronto para receber. O prefixo 'sink' indica que é uma porta de entrada, enquanto que o prefixo 'source' indica uma porta de saída. A tabela 3.1 descreve todos os sinais e a figura 3.5 ilustra duas situações de transição.

|              |         |         | ÷                                                 |  |  |

|--------------|---------|---------|---------------------------------------------------|--|--|

| Nome         | Direção | Largura | Descrição                                         |  |  |

| sink_sop     | entrada | 1       | Indica o início de um quadro de dados chegando    |  |  |

| sink_valid   | entrada | 1       | Quando alto, indica que tem um dado sendo re-     |  |  |

|              |         |         | cebido                                            |  |  |

| sink_ready   | saída   | 1       | Indica para o bloco anterior que está pronto para |  |  |

|              |         |         | receber                                           |  |  |

| source_sop   | saída   | 1       | Indica o início de um quadro de dados saindo      |  |  |

| source_valid | saída   | 1       | Quando alto, indica que tem um dado sendo en-     |  |  |

|              |         |         | viado                                             |  |  |

| source_ready | entrada | 1       | O próximo bloco está indicando que está pronto    |  |  |

|              |         |         | para receber                                      |  |  |

Tabela 3.1: Sinais no protocolo de comunicação

O neuroprocessador comunica-se com o ambiente externo através desse protocolo, assim como o(s) *kernel*(s). A unidade de controle manipula os dados que entram e saem dos núcleos com essa sinalização. Os sinais de comunicação provenientes da unidade de controle, que entram nos núcleos, seguem até as UPs, que também utilizam o protocolo. O fato de usar um protocolo único facilita a integração de novos blocos e a conexão entre eles.

Figura 3.5: (a) Transmissão simples (b) Dispositivo de recepção ocupado

23

## 3.5 Descrição do Kernel

#### 3.5.1 Caminho de Dados

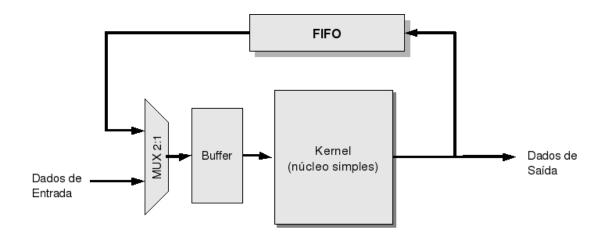

O processamento matemático dos dados de uma RNA acontece no Caminho de Dados. Este concentra todas as UPs e as funções de ativação, que fazem acesso às memórias contidas no bloco de memórias para acessar os pesos sinápticos e a LUT, respectivamente. Como mencionado anteriormente, o caminho de dados pode ter um ou dois núcleos, dependendo do modo de implementação utilizado.

Para a implementação com um núcleo, o sistema pode processar apenas uma camada por vez. O número de UPs no caminho de dados do núcleo determina o número máximo de neurônios por camada suportado. O núcleo pode ser utilizado para processar camadas com um número menor de neurônios que o de UPs. Porém, nesses casos, não há reaproveitamento das unidades em excesso.

A arquitetura do caminho de dados de núcleo simples, ilustrado na figura 3.6, pode ser classificado como BBA, baseando-se na forma que as UPs recebem e entregam os dados. Cada entrada de um novo padrão vai, de um em um, para todas as UPs do núcleo. Estas UPs computam operações de multiplicar-acumular em paralelo, a cada dado que chega, da mesma forma que na arquitetura BBA. No entanto, diferentemente da BBA apresentado em [Ienne 1993], somente uma LUT tem sido usada para todas as UPs do núcleo. Esta contenção de recursos é uma limitação para o processamento, resultando em um desempenho pior em relação à BBA, mas com o benefício de diminuir significantemente a área.

Uma vez que os dados do padrão de entrada chegam um a um, a limitação só acontece quando o número de entradas é menor que o número de nós na camada de saída. Isso indica que, em algumas situações, a restrição de recursos pode ter somente a redução da área, sem prejudicar o desempenho.

Junto com cada dado de entrada também chega o peso correspondente, sendo estes multiplicados e acumulados em um registrador dentro da UP. Os pesos para as UPs chegam através de um barramento único que liga todas as UPs ao módulo de memórias. Existe um seletor de memória relacionado a cada UP que escolhe os fios corretos no barramento. Este barramento pode dar acesso às diversas posições de memória como será discutido em mais detalhes na seção 3.5.4.

Depois que todos os dados de entrada foram processados, os resultados da operação de multiplicar e acumular de cada UP são enviados um a um para a função de ativação e, em seguida, vão para a saída. Enquanto os dados estão aguardando para serem processados pela função de ativação, outro padrão de entrada pode começar a ser processado visto que os resultados calculados pelos UPs são armazenados em registradores temporários. Todo o processo é controlado por uma FSM presente na Unidade de Controle.

Se o neuroprocessador tiver sido implementado com *kernel* de núcleo duplo, o caminho de dados tem sua estrutura duplicada para manter o desempenho similar ao de núcleo simples, no caso de estar configurado para redes de duas camadas. Os dois núcleos do caminho de dados são conectados por meio de uma memória do tipo First in First Out (FIFO). Os dados processados pelo primeiro núcleo passam pela FIFO e vão para o segundo núcleo. A FIFO é utilizada com o intuito de reduzir a limitação na comunicação

Figura 3.6: Caminho de Dados de Núcleo Simples

entre os núcleos. A figura 3.7 mostra como os núcleos são conectados.

O funcionamento individual de cada núcleo é exatamente o mesmo que o descrito acima para o caminho de dados de núcleo simples. Porém, cada camada é processada em um dos núcleos onde os dados da camada oculta são processados e enviados para o outro núcleo, que processa a camada de saída e envia os resultados para a saída. Se o neuroprocessador for configurado para uma rede de uma camada, apenas o primeiro núcleo é utilizado e sua saída é multiplexada para a saída do sistema.

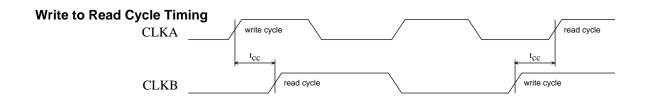

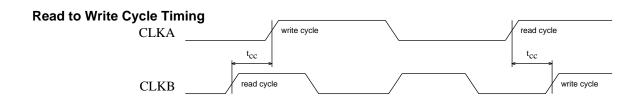

As duas funções de ativação, apesar de serem usadas independentemente, acessam a mesma LUT, também visando economizar área. Como a LUT está numa memória RAM de porta dupla, os núcleos podem usar a função paralelamente sem problemas de conflito de recursos. Essa escolha apenas restringe o sistema a um tipo de função de ativação via LUT.

A função de ativação também pode ser configurada para executar duas funções que não utilizam a LUT, a função degrau (*threshold*) e a função linear. Se o caminho de dados for de núcleo duplo, duas funções diferentes podem ser usadas em cada núcleo. Para núcleo simples, qualquer um dos três tipos de função pode ser utilizado.

No caso de implementações para processar três camadas, dois *kernels* em cascata são utilizados (ver Fig. 3.3). A conexão entre estes dois *kernels* é feita diretamente, sem o uso de FIFOs. Isto não diminui o desempenho contanto que o número de nós na camada de saída seja menor que o da segunda camada oculta. A comunicação entre os dois *kernels* é feita usando o protocolo descrito em 3.4.

Neste caso de dois *kernels*, como estes são independentes, pode haver mais de uma LUT, sendo que uma usada no primeiro *kernel* e a outra no segundo. Obviamente, a área aumenta de forma significativa.

25

Figura 3.7: Caminho de Dados de Núcleo Duplo

### 3.5.2 Unidade de Processamento

O somatório de produtos descrito na equação 3.1 é a operação mais crítica que afeta o desempenho do sistema. De fato, as principais métricas de desempenhos podem ser medidas indiretamente pela quantidade e velocidade de processamento paralelo dos neurônios. Esta operação é realizada por unidades do tipo multiplica-acumula (MAC) a cada novo dado que chega.

A figura 3.8 mostra as etapas envolvidas no processamento de um nó da rede. Cada dado novo que chega é multiplicado por um peso que chega ao mesmo tempo. Em seguida, o resultado da multiplicação é somado ao registrador acumulador. O primeiro dado a chegar é a polarização, que é multiplicada por um ao mesmo tempo em que ocorre uma desativação da soma do acumulador. Assim, o valor da polarização é o primeiro a ser carregado a cada novo nó processado. Esta operação determina a máxima freqüência de trabalho do sistema.

Os multiplicadores e somadores utilizados para compor a UP tiveram suas arquiteturas específicas selecionadas pelo sintetizador. Este escolhe as arquiteturas de cada operação

Figura 3.8: Diagrama da Unidade de Processamento

aritmética baseando-se em diversas variáveis de otimização do sistema como um todo, fazendo uma escolha melhor que a manual para a maioria dos casos.

Ao fim da recepção dos dados da camada anterior, o resultado da operação no acumulador é truncado e armazenado no registrador de saída. A informação permanece nesse registrador enquanto não poder ser enviada para a função de ativação, permitindo que a unidade já possa começar a receber dados referentes a outro padrão de entrada.

Em geral, o bloco da função de ativação tem uma entrada com largura menor que o tamanho do acumulador, devido à limitação de precisão (LUT pequena). O truncamento faz-se então necessário antes do dado ser enviado adiante.

27

A precisão durante o cálculo é assegurada por meio de bits de guarda que expandem a precisão do acumulador para suportar um número de adições igual ao número máximo de entradas em uma UP. Segundo [Omondi e Rajapakse 2006], o tamanho do acumulador é determinado a partir da equação:

$$acc\_width = log_2(n\_predecessors) + data\_width + weight\_width - 1$$

(3.3)

Onde data\_width e weight\_width são as resoluções do dado e do peso, respectivamente. n\_predecessors é o número de nós predecessores, que é igual à quantidade de dados de entrada na UP.

Figura 3.9: Esquema de truncamento na UP

Se o neuroprocessador for destinado a processar apenas uma topologia de RNA, o número de predecessores será fixo para cada um dos núcleos. Entretanto, caso haja reuso do *kernel* através de virtualização ou com topologias diferentes, o número de predecessores em cada núcleo dependerá da topologia que está sendo processada. A escolha mais coerente é considerar o maior número de operações que podem ser realizadas conforme as topologias que vão ser configuradas no neuroprocessador. Assim, sempre haverá bits suficientes para o processamento das UPs em todas as situações planejadas para o *hardware*.

Porém, o truncamento mencionado anteriormente não pode consistir somente de des-

cartar alguns bits menos significativos (LSB), porque para camadas diferentes e topologias diferentes temos um número de nós predecessores diferente. Isto significa que o bit mais significativo (MSB) para uma camada não é necessariamente o MSB da largura total do acumulador. Sendo assim, o truncamento deve descartar alguns LSB e alguns MSB mantendo uma saída fixa, igual à largura da entrada da função de ativação. A saída final do MAC desliza dentro da faixa de largura do acumulador, como ilustrado na figura 3.9. A posição é escolhida usando a largura real do acumulador para o número de predecessores da camada. Esta largura é computada no caminho de dados, realizando o mesmo cálculo da equação 3.3.

Para uma mesma configuração de topologia a faixa de bits deve se manter fixa para não inserir ganhos nos resultados de algumas camadas com relação às outras. Então, dentro de uma mesma topologia, o número de predecessores utilizado para o cálculo da largura efetiva do acumulador é o da camada com o maior número de entradas cujo valor é definido *off-line* e configurado no *hardware*.

### 3.5.3 Função de Ativação

Neste neuroprocessador, a função de ativação pode ser configurada para três tipos de operações diferentes:

- Função Linear;

- Função Degrau;

- Tabela de Look-up (LUT).

Para topologias de RNA lineares, nas quais as camadas de saídas são funções lineares, ou seja, simplesmente a soma ponderada dos valores de entrada, a função linear deve ser utilizada. A única operação realizada para esta função é um novo truncamento dos dados para deixá-los do mesmo tamanho da palavra do sistema.

A função degrau, que é muito utilizada em diversas aplicações, funciona colocando na saída o valor máximo ou mínimo se a entrada for positiva ou negativa, respectivamente. O valor mínimo pode ser configurado para zero ou o valor mais negativo representado na palavra do sistema.

Devido à flexibilidade, o uso da função de ativação através de uma tabela de look-up é a solução mais atraente e necessária para a maioria das aplicações.

A LUT tem que ser carregada na memória com uma aproximação suficientemente precisa da função não-linear escolhida. No conjunto das funções comumente usadas para redes MLP estão sigmoid, tangente hiperbólica, arco-tangente e rampa.

Para discretizar e armazenar em *hardware* uma função de ativação não-linear surgem algumas questões com relação à precisão.

A metodologia de discretização de funções descrita em [Omondi e Rajapakse 2006] têm sido adotada. De acordo com esta metodologia, somente um número conveniente  $n_s$  de MSB dentre o total de  $N_S$  bits da soma ponderada discreta deve ser usado como entrada da função de ativação discreta. Em [Omondi e Rajapakse 2006], o número ótimo  $n_{sopt}$  de bits de entrada é estimado em termos da derivada da função no ponto zero  $f'_0$ , o máximo de conexões de entrada em um neurônio, o valor máximo absoluto  $M_w$  de pesos contínuos, o número  $n_z$  de bits de entrada para o perceptron discreto e  $N_S$ .

29

A expressão para calcular  $n_{sopt}$  [Omondi e Rajapakse 2006] é repetida aqui por conveniência:

$$n_{sopt} = \left\lceil log_2 \left\lceil f_0' \# w M_w \frac{2^{N_S} (2^{n_z} - 2)}{2^{N_S} - 2} \right\rceil \right\rceil$$

(3.4)

Uma vez que o número de conexões de entrada para um neurônio pode variar consideravelmente entre diferentes configurações de topologias de RNA,  $n_s$  não pode ser o valor ótimo para todas as situações. Um  $n_{sopt}$  pode ser encontrado para o pior caso em que o número de predecessores é o maior. Por exemplo, se adotarmos uma função sigmoide padrão, #w = 511,  $M_w = 1$ ,  $N_S = 40$ ,  $n_z = 16$  e  $f'_0 = 1/4$ , a partir de 3.4,  $n_{sopt}$  será 23.

Além disso, ainda de acordo com [Omondi e Rajapakse 2006], uma vez que os valores da função de ativação discreta, em sua maioria, são iguais aos seus valores mínimo ou máximo, a LUT precisa armazenar apenas os valores correspondentes ao intervalo central de entrada, onde a variação é significativa. [Omondi e Rajapakse 2006] Também apresenta expressões para calcular os limites do intervalo central  $i_{min}$  e  $i_{max}$ , em termos dos parâmetros da função de ativação adotada. Portanto, o número de bits necessários para especificar a LUT é dado por [Omondi e Rajapakse 2006]:

$$n_{LUT} = \lceil log_2(i_{max} - i_{min} + 1) \rceil \tag{3.5}$$

De fato, a LUT é aplicada somente aos valores da soma discreta ponderada dentro do intervalo  $i_{min}$  e  $i_{max}$ . Estes parâmetros têm que ser configurados para cada tipo de função adotada.

Como  $n_{LUT}$  é diretamente proporcional a ns através das expressões de  $i_{min}$  e  $i_{max}$ , o tamanho da memória da LUT pode ser diminuído reduzindo-se o valor de  $n_s$  para um valor abaixo de  $n_{sopt}$ , o que obviamente reduzirá a precisão da função.

Neste projeto, a LUT é implementada utilizando memória SRAM de porta dupla para que possa ser usada por dois núcleos simultaneamente. Memória de tecnologia *flash* também poderia ser usada para eliminar a necessidade de reescrita a cada vez que o sistema é reiniciado.

### 3.5.4 Arquitetura de Memória

Durante a operação do sistema, cada UP precisa acessar um valor de peso a cada pulso de clock, independente das outras UPs. Isto significa que o armazenamento dos pesos precisa ser feito em pequenas unidades, de forma que as UPs possam acessar os seus pesos em paralelo. A arquitetura de memória também deve permitir que os dois núcleos acessem todos os valores de pesos armazenados a qualquer hora. Além disso, quando o neuroprocessador é utilizado para mais de uma topologia de RNA, a arquitetura deve permitir que o conjunto de pesos seja modificado a cada transição de configurações de topologia.

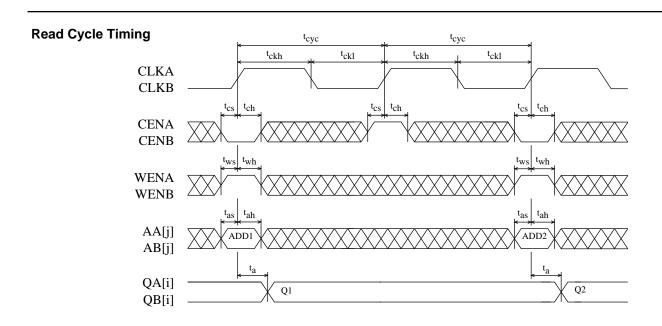

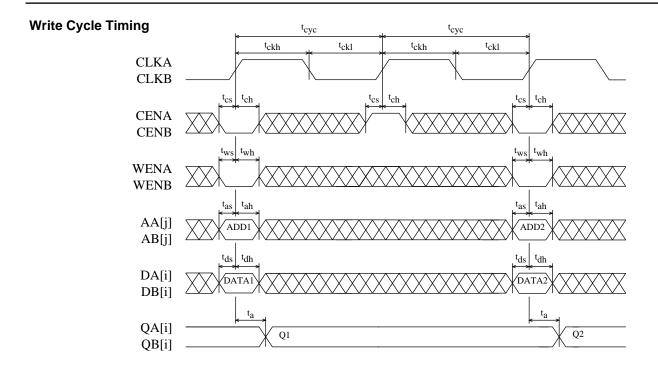

Essas pequenas unidades de memória, aqui chamadas de blocos, estão sendo implementadas com memórias SRAM síncrona de duas portas, atendendo dois dos requisitos citados acima. Memórias de duas portas permitem leituras de endereços diferentes em paralelo durante um único ciclo.

Entretanto, se tivermos um bloco associado a cada UP e diversas topologias utilizadas no mesmo *hardware*, o tamanho dos blocos pode ser consideravelmente grande. Para projetar os circuitos integrados de memória na tecnologia CMOS, geradores automáticos de memória são amplamente utilizados, pois apresentam melhores resultados com relação ao alto nível de densidade, à velocidade e ao consumo. As informações com relação às memórias geradas vêm em forma de um *hard block*, para ser usado no *layout*, e um modelo em uma Linguagem de Descrição de *Hardware* (HDL) para simulação. Este *hard block* tem uma forma definida pelo gerador, o que pode ocasionar problemas em casos de um número elevado de blocos grandes, reduzindo drasticamente a flexibilidade de definição do formato do *layout*. A ocorrência de grandes e numerosas memórias também pode ser problemática para implementação em outras tecnologias, como na prototipação em FPGA.

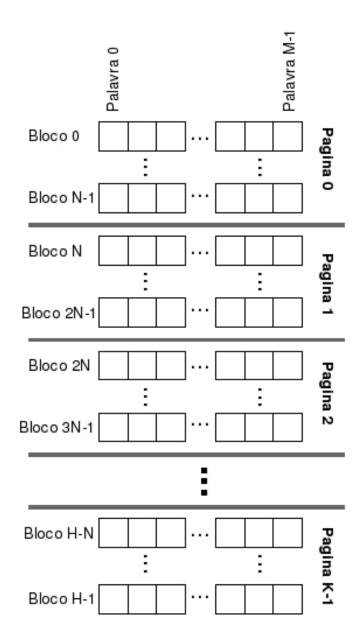

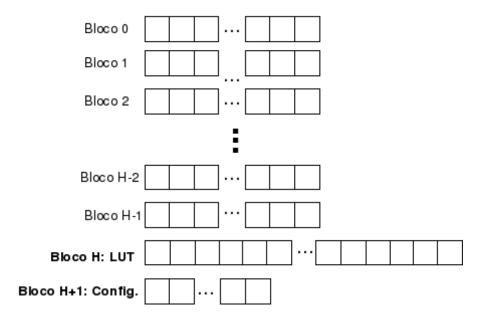

Visando reduzir o tamanho dos blocos, estes foram agrupados em páginas. Cada página contém um número de blocos menor ou igual ao número de UPs. Um núcleo pode apontar para uma página por vez. No entanto, os dados dos neurônios podem estar tanto concentrados em um único bloco como espalhados em alguns blocos em páginas diferentes. A organização de blocos e páginas está ilustrada na figura 3.10, contendo uma arquitetura com H blocos de M palavras e K páginas de N blocos cada uma.

Essa arquitetura com divisão por páginas provê escalabilidade para o *hardware* com relação às memórias. Também possibilita um bom aproveitamento das memórias, associando páginas a núcleos. Assim, as páginas podem ter a quantidade de blocos igual à quantidade de UPs do núcleo.

A unidade de controle faz o gerenciamento de qual posição é lida pelas UPs a cada instante. A cada dado que chega no *kernel* (ou no núcleo), todas as UPs precisam acessar o peso associado àquela entrada simultaneamente. Para uma página selecionada, um único endereço é usado para acessar todos os pesos referentes às UPs de um núcleo. Por exemplo, se a página 1 e o endereço 64 estiverem selecionados, todas as UPs do núcleo acessarão a posição 64 de memória do bloco correspondente, dentro da página 1. Apesar desta organização, a unidade de controle trata a memória como contínua, simplesmente usando um endereço global composto pelos endereços da página (MSB) e interno do bloco (LSB).

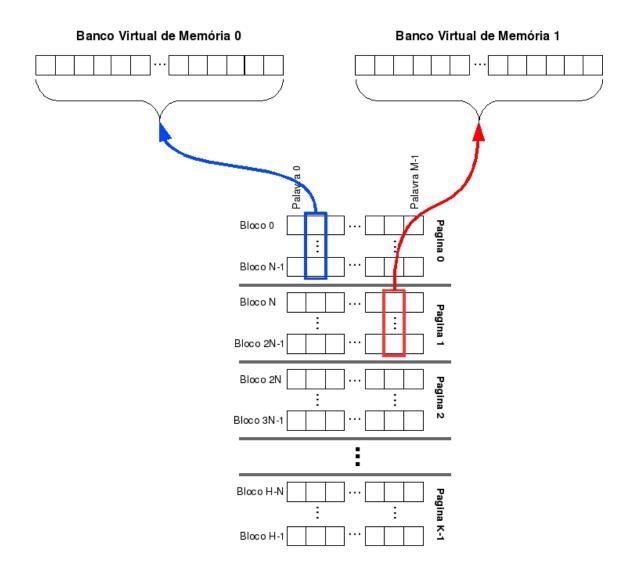

A transferência dos dados entre o módulo de memória e os núcleos acontece por meio de barramentos onde são concatenados todos os dados que vão para um mesmo núcleo. Este barramento, chamado de banco virtual, conecta um núcleo com uma página, dando acesso a todos os seus blocos. A implementação em barramento, ao invés de matricial, foi escolhida por conta de limitações da linguagem Verilog em utilizar vetores bidimensionais como entrada ou saída dos módulos. Figura 3.11 ilustra a atribuição dos dados no banco virtual.

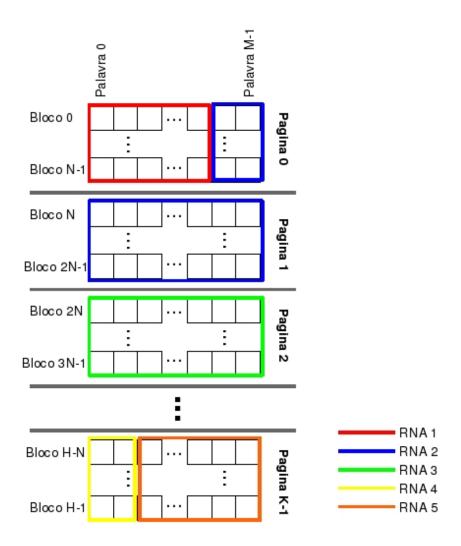

Quando o sistema é utilizado para processar mais de uma RNA, quando há virtualização ou mesmo para estrutura de núcleo duplo, a memória deve ser dividida para alocar os pesos relativos a cada camada ou parte de camada para cada RNA. Nestes casos, os dois núcleos podem precisar endereçar os mesmos blocos em regiões diferentes, o que exige o uso de memórias de duas portas. Um exemplo de divisão é mostrado na figura 3.12. Uma configuração é guardada para informar à unidade de controle o começo e o comprimento

Figura 3.10: Arquitetura da memória de pesos

de cada trecho.

Todas as memórias do sistema têm sido implementadas utilizando a tecnologia SRAM, onde cada bloco da figura 3.10 é um módulo SRAM de duas portas. Sendo assim, elas precisam ser escritas antes do sistema começar a ser usado. O *kernel* disponibiliza duas portas para endereçar os dados, uma para acessar o bloco e outra para acessar uma posição dentro do bloco. Do ponto de vista da escrita externa, a LUT e uma memória de configurações são tratadas como blocos e podem ser escritas utilizando as mesmas portas,

Figura 3.11: Atribuição de dados ao banco virtual

como mostrado na figura 3.13.

A memória de configurações armazena valores usados pela Unidade de Controle e pelo caminho de dados durante o processamento. A tabela 3.2 mostra a lista dos registradores de configuração. Note que existem vários pares dos registradores  $cfg\_nodes\_virtual < xx >$  e  $cfg\_start\_virtual < xx >$ . Essas são várias opções de configuração visando dar suporte à virtualização, onde cada par pode estar relacionado com uma camada, pedaço de camada ou uma topologia de RNA. Todos os registradores de configuração possuem 16 bits. Para mudar a configuração para outra camada, pedaço de camada ou RNA, o registrador  $cfg\_layers$  deve ser modificado, conforme indicado na tabela 3.2.

Dessa forma, a reconfiguração do *kernel* para processar camadas ou pedaços de camadas diferentes acontece em apenas um ciclo de relógio, bastando mudar o valor das configurações  $cfg\_virtual\_conf < x >$ . Por exemplo, o par  $cfg\_nodes\_virtual00$  e

Figura 3.12: Exemplo de configuração para diversas topologias de RNA

$cfg\_start\_virtual00$  podem ser as configurações da primeira metade de uma camada e o par  $cfg\_nodes\_virtual01$  e  $cfg\_start\_virtual01$  a configuração da segunda metade.

Os registradores de configuração  $cfg\_nodes\_virtual < xx >$  possuem os seguintes campos:

- bit 0-9 : Numero de nós

- bit 10: faixa da função de ativação. 0 [0;1] / 1 [-1;1]

- bit 11: Reservado

- bit 12-13: Tipo de função de ativação. 00 LUT; 01 *bypass* (linear); 10 *Threshold*; 11 Reservado

- bit 14-15: Indica a camada sendo processada. 00 entrada; 01 oculta1; 10 oculta2; 11 saída

Figura 3.13: Arquitetura de memória incluindo LUT e configuração

#### 3.5.5 Unidade de Controle

O modo como os dados fluem na cadeia de processamento do sistema faz com que não haja muita necessidade de *hardware* de controle. As atribuições da unidade de controle são:

- geração dos sinais do protocolo que vão para as UPs;

- gerenciamento das limitações entre UPs e a função de ativação;

- atribuição dos endereços da página e da posição no bloco de memória;

- multiplexação dos dados das UPs para funções de ativação.

Essas tarefas, já descritas anteriormente, são realizadas utilizando-se uma ou duas FSM, sendo que cada FSM está associada a um núcleo do caminho de dados. Cada FSM funciona de forma independente, não importando se o *kernel* está configurado para núcleo simples, núcleo duplo ou virtualização. Figura 3.14 ilustra o diagrama de estados da FSM.

A sinalização é feita com base nos sinais que chegam ao *kernel* e a disponibilidade do bloco seguinte. Funcionando de acordo com o protocolo utilizado no sistema. Em casos de núcleo duplo, a FIFO entre os núcleos facilita o trabalho do controle.

## 3.6 Virtualização

A operação de virtualização consiste em realizar o cálculo computacional da RNA inteira em algumas etapas, reusando o *kernel* para calcular camada por camada ou mesmo quebrando camadas em pequenos pedaços. O número de neurônios desses pedaços de camadas deve ser menor ou igual ao número de UPs disponíveis.

3.7. SUMÁRIO 35

Nome Descrição End. bit 0-2 - Número de camadas 0 cfg\_layers bit 3 – reservado bit 4-9 - cfg\_virtual\_conf0 - Configuração virtual para o núcleo 0 bit 10-15 - cfg\_virtual\_conf1- Configuração virtual para o núcleo 1 Valor mínimo de entrada na função de ativação onde cfg\_actv\_i\_min a LUT precisa ser usada Valor máximo de entrada na função de ativação onde 2 cfg\_actv\_i\_max a LUT precisa ser usada Número de predecessores para ser usado no trunca-3 cfg\_n\_pred\_lut mento das UPs reservado 4 5 cfg\_nodes\_virtual00 Config. 00 para os nós de um núcleo cfg\_start\_virtual00 Posição de início dos pesos para conf. 00 6 7 cfg\_nodes\_virtual01 Config. 01 para os nós de um núcleo 8 cfg\_start\_virtual01 Posição de início dos pesos para conf. 01 Config. 02 para os nós de um núcleo 9 cfg\_nodes\_virtual02 cfg\_start\_virtual02 Posição de início dos pesos para conf. 02 10 11 cfg\_nodes\_virtual03 Config. 03 para os nós de um núcleo 12 cfg\_start\_virtual03 Posição de início dos pesos para conf. 03 Config. 04 para os nós de um núcleo cfg\_nodes\_virtual04 13 cfg\_start\_virtual04 Posição de início dos pesos para conf. 04 14

Tabela 3.2: Registradores de configuração

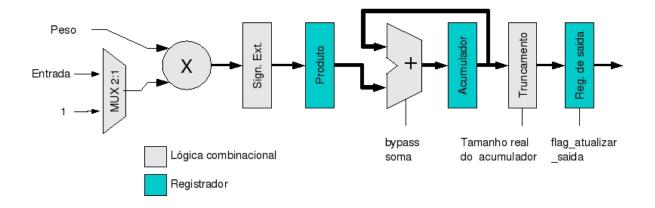

Uma lógica de controle extra, uma FIFO, um *buffer* e um *kernel* são usado para fazer os cálculos passo a passo. Mudar o conjunto de neurônios a ser processado requer endereçar valores de pesos diferentes na memória. Como visto na seção 3.5.4, a mudança dos pesos previamente armazenados dura apenas um ciclo de relógio, bastando modificar o valor do registrador de configuração  $cfg\_layers$  no campo  $cfg\_virtual\_conf < x >$ . O esquema de virtualização é mostrado na figura 3.15.