## UNIVERSIDADE FEDERAL DA BAHIA ESCOLA POLITÉCNICA DA UFBA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

# DISTORÇÃO EM MULTIPLICADORES ANALÓGICOS: ANÁLISE COMPARATIVA DE MÉTODOS AC E DC

Autora: Gabriele Costa Gonçalves Orientadora: Prof<sup>a</sup> Dr<sup>a</sup> Ana Isabela Araújo Cunha

# GABRIELE COSTA GONÇALVES

# DISTORÇÃO EM MULTIPLICADORES ANALÓGICOS: ANÁLISE COMPARATIVA DE MÉTODOS AC E DC

Tese de Doutorado submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal da Bahia como parte dos requisitos necessários para obtenção do grau de Doutora em Engenharia Elétrica.

Ana Isabela Araújo Cunha (Orientadora)

Gonçalves, Gabriele

Distorção em multiplicadores analógicos: Análise

Comparativa de métodos AC e DC / Gabriele Gonçalves. -Salvador, 2020.

114 f.

Orientadora: Ana Isabela Cunha. Tese (Doutorado - Engenharia Elétrica) --Universidade Federal da Bahia, Escola Politécnica, 2020.

1. distorção. 2. multiplicador analógico. 3. função não-linear integral. 4. distorção harmônica total. I. Cunha, Ana Isabela. II. Título.

#### Gabriele Costa Gonçalves

"Distorção em Multiplicadores Analógicos: Análise Comparativa de Métodos AC e DC"

Tese apresentada à Universidade Federal da Bahia, como parte das exigências do Programa de Pós-Graduação em Engenharia Elétrica, para a obtenção do título de Doutor.

APROVADA em: 17 de Fevereiro de 2020.

#### **BANCA EXAMINADORA**

Prof<sup>a</sup>. Dr<sup>a</sup> Ana Isabela Argújo Cunha Orientadora/UFBA

> Prof. Dr. Tito Luís Maia Santos UFBA

Prof. Dr. Carlos Eduardo Viana Nunes UFBA

Prof. Dr. Sebastian Yuri Cavalcanti Catunda UFRN

Prof. Dr. Raimundo Carlos Silvério Freire UFCG

Kainjundo Carlos S. Freise

### **AGRADECIMENTOS**

Primeiramente gostaria de agradecer à minha estimada orientadora e amiga, Prof.<sup>a</sup> Ana Isabela, por todo o conhecimento ensinado, pela dedicação, por sua amizade, sinceridade, pelos puxões de orelha, por ter sido presente em todas as etapas do meu trabalho, o meu muito obrigada porque sem a senhora nada disso seria possível.

Aos professores Edson, Maicon e Carlos, por estarem sempre disponíveis para ajudar nas medições e pelas explicações esclarecedoras.

Aos meus queridos colegas do LCCI, Fernando, Lucas D'Eça, Fabian e Hildeloi, pelos momentos de descontração, de colaboração e de conhecimentos compartilhados.

À minha estimada família, Gilmar, Rosa e Grazi, por estarem presentes durante a minha caminhada e pelas palavras de amor e carinho.

Ao meu querido noivo Paulo Roberto, por ser sempre tão compreensivo, carinhoso, amoroso e prestativo.

À Deus por iluminar os meus passos, estar sempre presente na minha vida e por permitir a finalização dessa pesquisa.

E finalmente a todos que ajudaram diretamente ou indiretamente na conclusão do meu trabalho.

# LISTA DE ILUSTRAÇÕES

| Figura 2.1: Configuração Básica de um multiplicador24                         |

|-------------------------------------------------------------------------------|

| Figura 2.2: Operação do multiplicador utilizando transcondutor                |

| programável                                                                   |

| Figura 2.3: Dispositivo não linear                                            |

| Figura 2.4: Esquema de cancelamento baseado em núcleos de                     |

| multiplicadores de um quadrante                                               |

| Figura 2.5: Esquema de cancelamento baseado em núcleos quadradores29          |

| Figura 2.6: Métodos de injeção de sinal em tensão30                           |

| Figura 2.7: Representação da superfície característica de transferência de um |

| multiplicador analógico ideal (paraboloide hiperbólico), para o caso de       |

| constante de multiplicação igual a 0,143                                      |

| Figura 2.8: Rede neuronal celular                                             |

| Figura 2.9: Diagrama de blocos da célula padrão50                             |

| Figura 2.10: Diagrama de blocos para a célula do tipo FSR51                   |

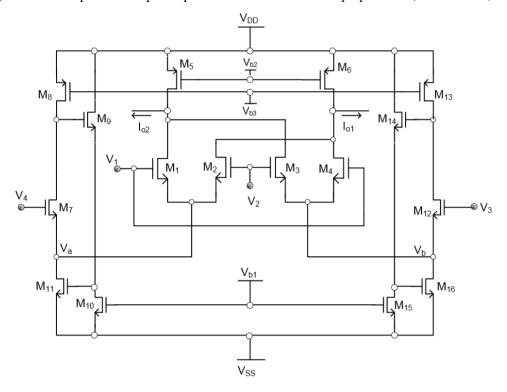

| Figura 3.1: Multiplicador proposto em (SAWIGUN; DEMOSTHENOUS e                |

| PAL, 2007)53                                                                  |

| Figura 3.2: Multiplicador de quatro quadrantes proposto em (CARDOSO;          |

| SHNEIDER e SANTANA, 2018)54                                                   |

| Figura 3.3: Multiplicador de quatro quadrantes em modo corrente proposto      |

| em (TANNO; ISHIZUKA e TANG)55                                                 |

| Figura 3.4: Multiplicador de quatro quadrantes em modo corrente proposto      |

| em (MAHMOUD, 2009)56                                                          |

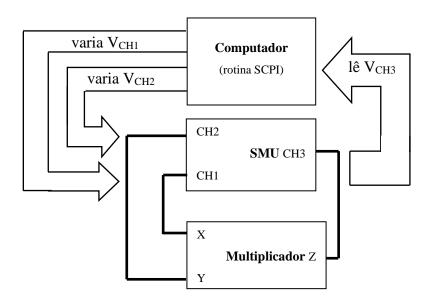

| Figura 3.5: Acessório de teste paramétrico U2941A da Agilent57                |

| Figura 3.6: Diagrama de blocos da configuração para medição das               |

| superfícies DC $V_{CHi}$ é a tensão do canal CHi, com i = 1, 2, 358           |

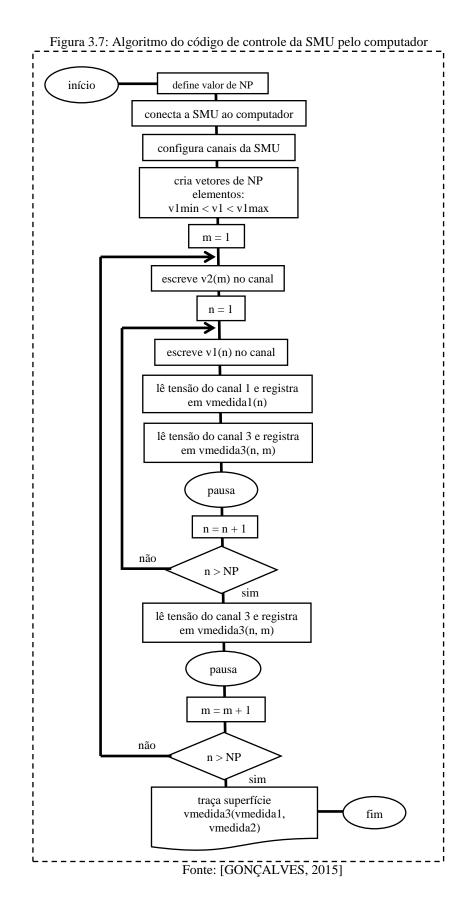

| Figura 3.7: Algoritmo do código de controle da SMU pelo computador60          |

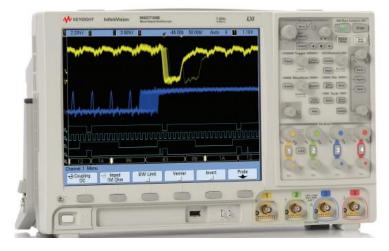

| Figura 3.8: Osciloscópio da Keysight Technologies MSO7104B62                  |

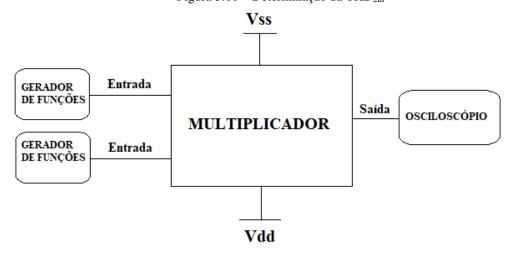

| Figura 3.9: Determinação da THD                                                                | 63  |

|------------------------------------------------------------------------------------------------|-----|

| Figura 3.10: Determinação da THD <sub>2in</sub>                                                | 63  |

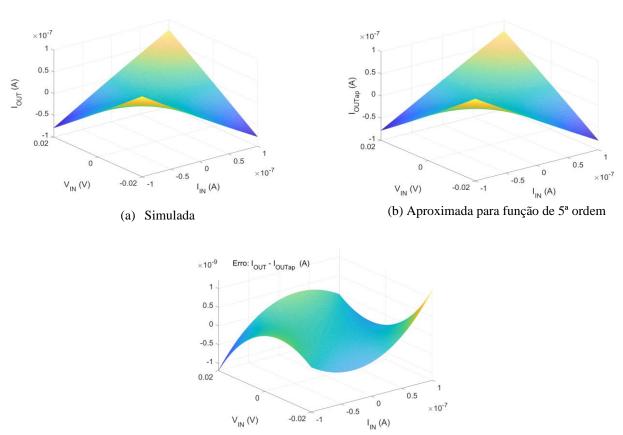

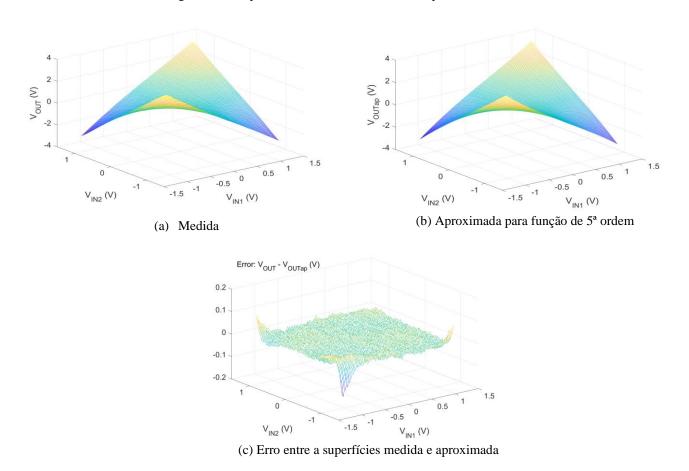

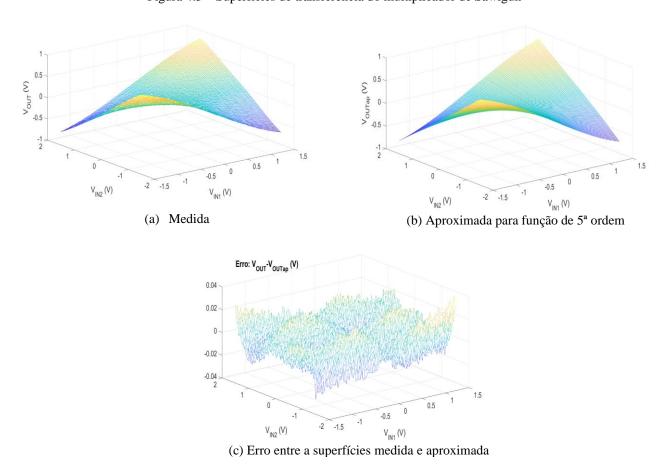

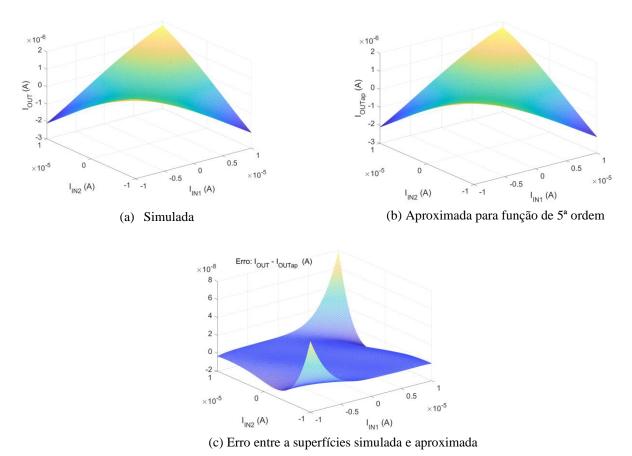

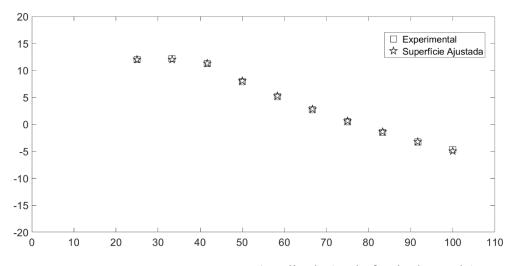

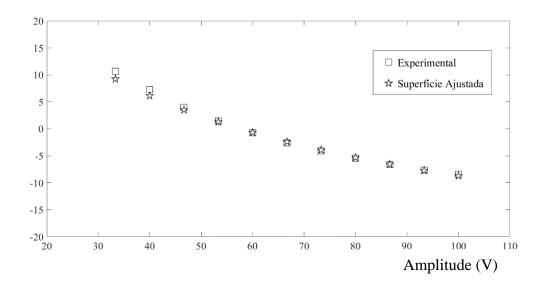

| Figura 4.1: Superfícies de transferência do multiplicador de Cardoso                           | 67  |

| Figura 4.2: Superfícies de transferência do multiplicador de Mahmoud                           | 68  |

| Figura 4.3: Superfícies de transferência do multiplicador de Sawigun                           | 68  |

| Figura 4.4: Superfícies de transferência do multiplicador de Tanno                             | 69  |

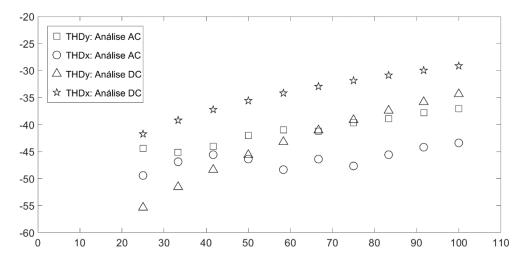

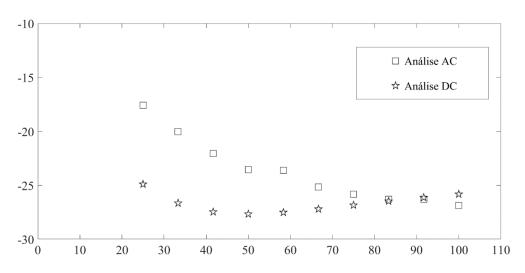

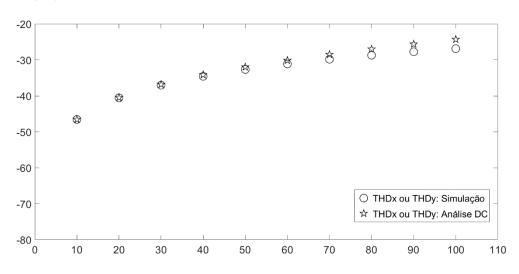

| Figura 4.5: THD do multiplicador de Cardoso                                                    | 70  |

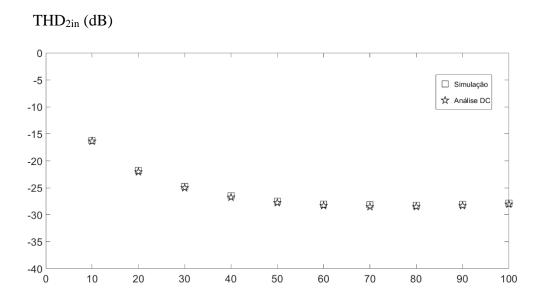

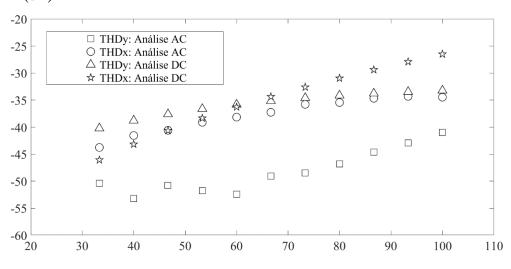

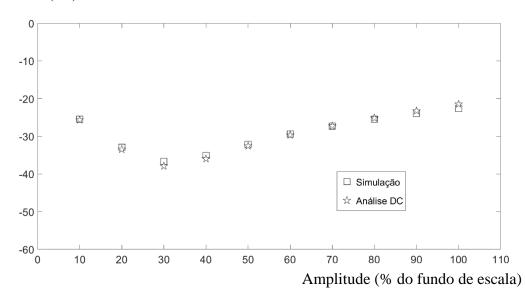

| Figura 4.6: THD <sub>2in</sub> do multiplicador de Cardoso                                     | 71  |

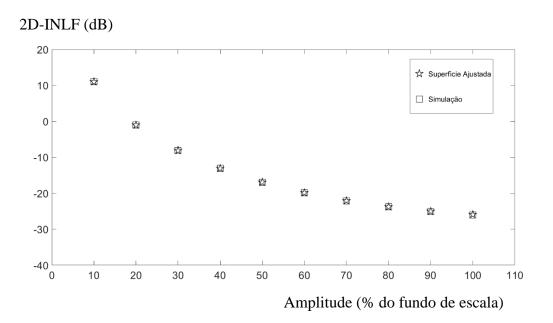

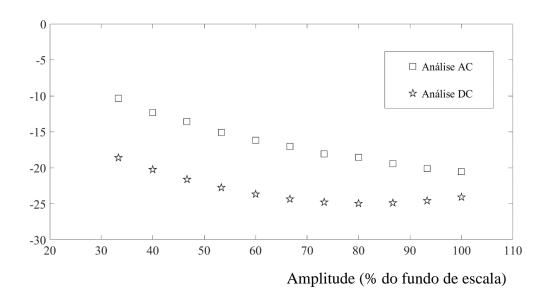

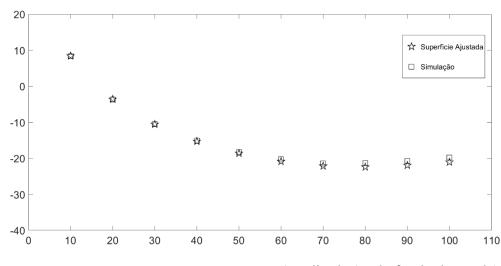

| Figura 4.7: 2D-INLF do multiplicador de Cardoso                                                | 71  |

| Figura 4.8: THD do multiplicador de Mahmoud                                                    | 72  |

| Figura 4.9: THD <sub>2in</sub> do multiplicador de Mahmoud                                     | 72  |

| Figura 4.10: 2D-INLF do multiplicador de Mahmoud                                               | 73  |

| Figura 4.11: THD do multiplicador de Sawigun                                                   | 73  |

| Figura 4.12: THD <sub>2in</sub> do multiplicador de Sawigun                                    | 74  |

| Figura 4.13: 2D-INLF do multiplicador de Sawigun                                               | .74 |

| Figura 4.14: THD do multiplicador de Tanno                                                     | 75  |

| Figura 4.15: THD <sub>2in</sub> do multiplicador de Tanno                                      | 75  |

| Figura 4.16: 2D-INLF do multiplicador de Tanno                                                 | 76  |

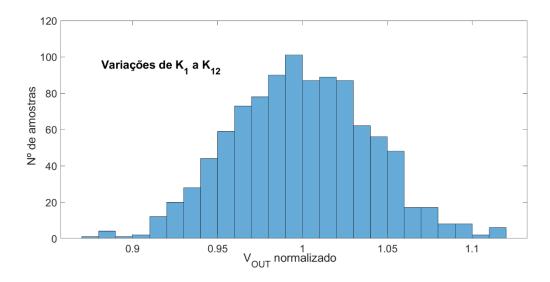

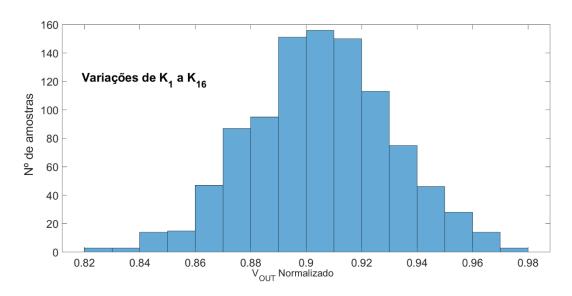

| Figura 5.1: Distribuição da tensão de saída do multiplicador Sawigun p                         | ara |

| 1000 combinações aleatórias de $K_1$ a $K_{12}$ em distribuição normal com des                 | vio |

| padrão de 1%                                                                                   | .84 |

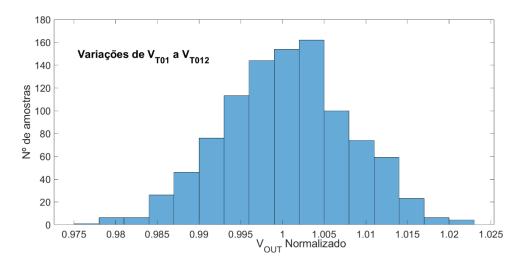

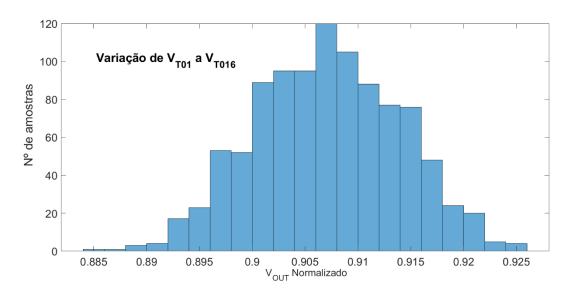

| Figura 5.2: Distribuição da tensão de saída do multiplicador Sawigun p                         | ara |

| 1000 combinações aleatórias de $V_{T01}$ a $V_{T012}$ em distribuição normal c                 | om  |

| desvio padrão de 10%                                                                           | 84  |

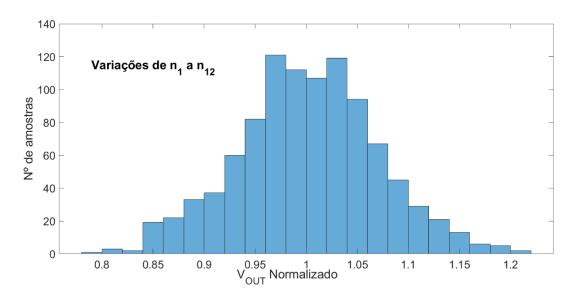

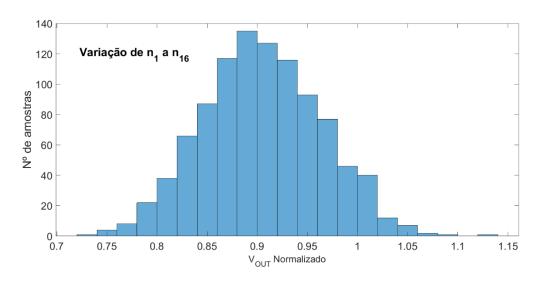

| Figura 5.3: Distribuição da tensão de saída do multiplicador Sawigun p                         | ara |

| 1000 combinações aleatórias de n <sub>1</sub> a n <sub>12</sub> em distribuição normal com des | vio |

| padrão de 1%                                                                                   | .85 |

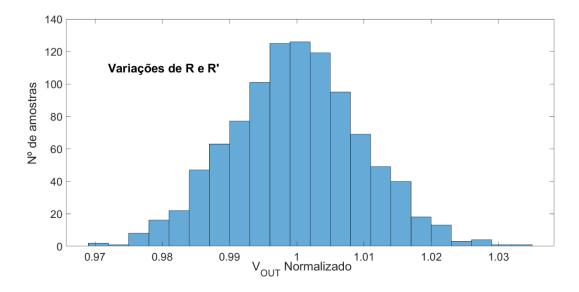

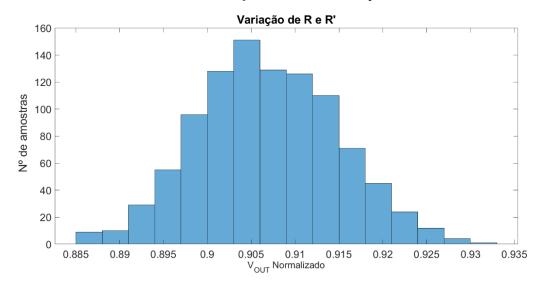

|                                                                                                |     |

| Figura 5.4: Distribuição da tensão de saída do multiplicador Sawigun para                  |

|--------------------------------------------------------------------------------------------|

| 1000 combinações aleatórias de R a R' em distribuição normal com desvio                    |

| padrão de 10%85                                                                            |

| Figura 5.5: Distribuição da tensão de saída do multiplicador Mahmoud para                  |

| $1000\ combinações\ aleatórias\ de\ K_1\ a\ K_{12}\ em\ distribuição\ normal\ com\ desvio$ |

| padrão de 1%86                                                                             |

| Figura 5.6: Distribuição da tensão de saída do multiplicador Mahmoud para                  |

| 1000 combinações aleatórias de $V_{T01}$ a $V_{T016}$ em distribuição normal com           |

| desvio padrão de 10%86                                                                     |

| Figura 5.7: Distribuição da tensão de saída do multiplicador Mahmoud para                  |

| $1000$ combinações aleatórias de $n_1$ a $n_{16}$ em distribuição normal com desvio        |

| padrão de 1%87                                                                             |

| Figura 5.8: Distribuição da tensão de saída do multiplicador Mahmoud para                  |

| 1000 combinações aleatórias de R a R' em distribuição normal com desvio                    |

| padrão de 10%87                                                                            |

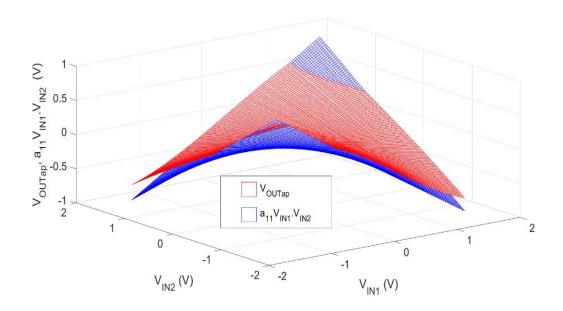

| Figura 5.9: Comparação entre a superfícies de transferência do ideal (azul) e              |

| a superfície de transferência aproximada (vermelha) do Multiplicador                       |

| Sawigun89                                                                                  |

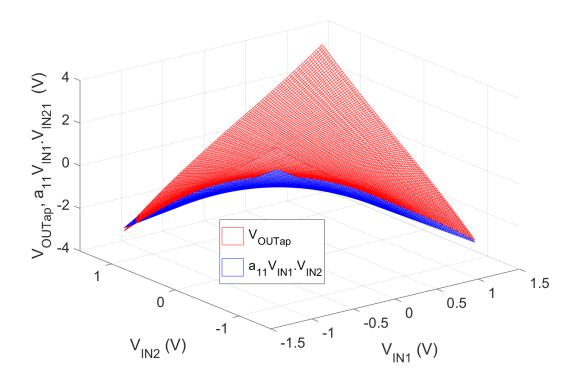

| Figura 5.10: Comparação entre a superfícies de transferência do ideal (azul)               |

| e a superfície de transferência aproximada (vermelha) do Multiplicador                     |

| Mahmoud89                                                                                  |

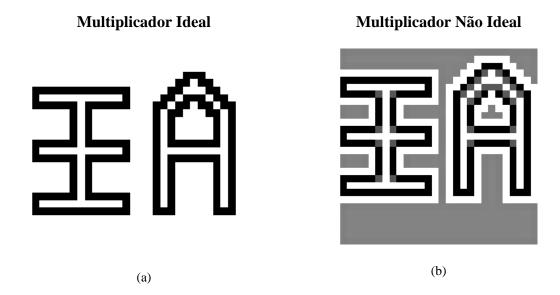

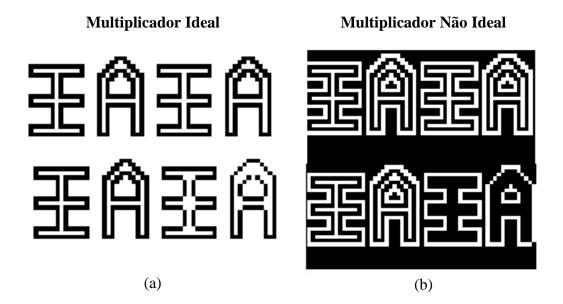

| Figura 6.1: Imagem de entrada (Função detecção de bordas binária)94                        |

| Figura 6.2: Imagem de saída da CNN teórica operando como detector de                       |

| borda binária, nos casos do multiplicador ideal e não ideal para a imagem de               |

| entrada da Figura 6.194                                                                    |

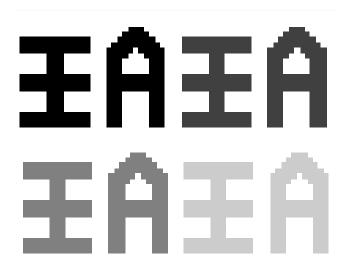

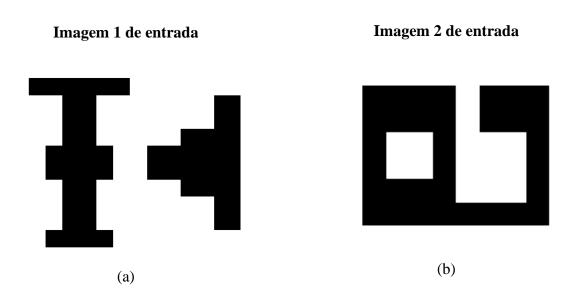

| Figura 6.3: Imagem de entrada (Função detecção de bordas em escala preto                   |

| e cinza)95                                                                                 |

|                                                                                            |

| Figura 6.4: Imagem de saída da CNN teórica operando como detector de         |

|------------------------------------------------------------------------------|

| borda em escala preto e cinza, nos casos do multiplicador ideal e não ideal  |

| para a imagem de entrada da Figura 6.395                                     |

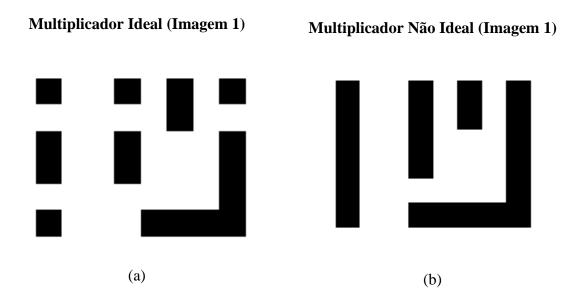

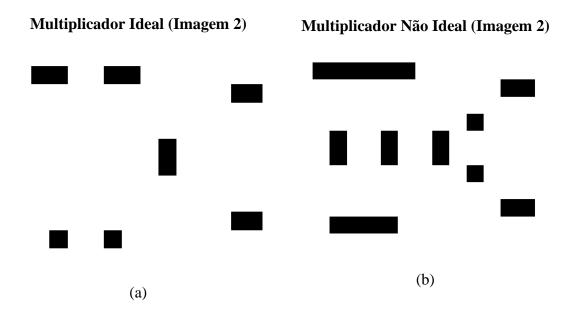

| Figura 6.5: Imagens de entrada para a função de quina96                      |

| Figura 6.6: Imagem de saída da CNN teórica na operação de detecção de        |

| quina, nos casos do multiplicador ideal e não ideal para a imagem de entrada |

| da Figura 6.5(a)                                                             |

| Figura 6.6: Imagem de saída da CNN teórica na operação de detecção de        |

| quina, nos casos do multiplicador ideal e não ideal para a imagem de entrada |

| da Figura 6.5(b)97                                                           |

# LISTA DE TABELAS

| Tabela 2.1: Multiplicadores x Figuras de mérito                              |  |  |  |  |

|------------------------------------------------------------------------------|--|--|--|--|

| Tabela 2.2: Amplitudes das componentes de frequências da saída do            |  |  |  |  |

| multiplicador com distorção de 5ª ordem – caso de entrada senoidal e entrada |  |  |  |  |

| constante                                                                    |  |  |  |  |

| Tabela 2.3: Amplitudes das componentes de frequências da saída do            |  |  |  |  |

| multiplicador com distorção de 5ª ordem – caso de duas entradas              |  |  |  |  |

| senoidais                                                                    |  |  |  |  |

| Tabela 3.1: Resumo das metodologias x multiplicadores65                      |  |  |  |  |

| Tabela 4.1: Coeficientes de distorção dos multiplicadores                    |  |  |  |  |

| testados                                                                     |  |  |  |  |

| Tabela 4.2: Erros na Aproximação das Superfícies de Transferência dos        |  |  |  |  |

| Multiplicadores                                                              |  |  |  |  |

| Tabela 5.1: Expressões dos coeficientes de distorção do multiplicador de     |  |  |  |  |

| Sawigun81                                                                    |  |  |  |  |

| Tabela 5.2: Expressões dos coeficientes de distorção do multiplicador de     |  |  |  |  |

| Mahmoud83                                                                    |  |  |  |  |

| Tabela 5.3: Contribuição dos coeficientes de distorção para o sinal de saída |  |  |  |  |

| - Multiplicadores de Sawigun e Mahmoud88                                     |  |  |  |  |

### LISTA DE ABREVIATURAS

RMS - Root Mean Square

DC - Direct Current

AC - Alternating Current

THD - Total Harmonic Distortion

IM<sub>n</sub> - *Intermodulation Distortion of order n*

INLF - Integral Non-Linear Function

2D-INLF - Two Dimensional Integral Non-Linear Function

CNN - Cellular Neural Network

CMOS - Complementary Metal Oxide Semiconductor

MOS - Metal Oxide Semiconductor

MOSFET - Metal Oxide Semiconductor Field Effect Transistor

TBJ - Transistor Bipolar de Junção

FET - Field Effect Transistor

GPDK – Generic Process Design Kit

VSLI - Very Large Scale Integration

HD<sub>n</sub> - Harmonic Distortion of order n

IP<sub>n</sub> - Intercept Points of order n

IP<sub>2</sub>- Second Intercept Points

IP<sub>3</sub> - Third Intercept Points

HD<sub>2</sub> - Second Harmonic Distortion

HD<sub>3</sub> - Third Harmonic Distortion

IFM - Integral Function Method

NP - Número de pontos

FSR - Full Signal Range

SMU - Source Measure Unit

SCPI - Standard Commands for Programmable Instruments

## LISTA DE SÍMBOLOS

K - constante de multiplicação (ganho)

Z - saída do multiplicador

A<sub>máx</sub> - máxima amplitude

A<sub>min</sub> - mínima amplitude

DR - Dynamic Range

Gm1 - transcondutância bipolar

V<sub>t</sub> - tensão térmica

k<sub>B</sub> - constante de Boltzmann

T - temperatura absoluta

x e y - entradas do multiplicador

a e b - números inteiros

$A_1$  e  $A_2$  - amplitudes diferentes

$A_{a,b}$  - amplitude da componente do sinal de saída

$a_{mn}\mbox{-}$  coeficientes de distorção (m e n inteiros não negativos)

C<sub>1</sub> - amplitude da componente na frequência fundamental na saída

C<sub>n</sub> - amplitude da enésima harmônica

$f_1$  e  $f_2$  - frequências diferentes

v1min, v1max, v2min e v2max - limites de variações das tensões nas entradas do multiplicador

### **RESUMO**

Este trabalho apresenta uma comparação teórica entre três critérios distintos para avaliação da distorção harmônica em multiplicadores analógicos: a função não linear integral de duas dimensões e a distorção harmônica total de duas entradas, ambas propostas por nosso grupo de pesquisa do Laboratório de Concepção de Circuitos Integrados (LCCI) da Universidade Federal da Bahia, e a distorção harmônica total simples convencional. Metodologias são propostas para determinar estas figuras de mérito utilizando caracterização DC. Além da determinação direta da função não linear integral de duas dimensões, os coeficientes de distorção calculados para ajustar a superfície de transferência DC são utilizados para estimar as distorções harmônicas totais para entrada simples ou dupla. Resultados de simulação e experimentais obtidos para quatro diferentes topologias de multiplicadores analógicos em tecnologia CMOS demonstram que figuras de mérito determinadas seja por análise AC ou por análise DC podem ser consistentes. Também ilustramos como tirar vantagem da análise de distorção de multiplicadores analógicos por meio de caracterização DC para estabelecer diretrizes de projeto e de implementação do circuito a fim de minimizar a distorção. Com este propósito, dois multiplicadores analógicos em tecnologia CMOS em modo tensão são analisados teoricamente para relacionar os coeficientes de distorção de suas superfícies de transferência DC aos parâmetros tecnológicos e à geometria dos transistores.

Palavras-Chaves: distorção; multiplicador analógico; função não-linear integral; distorção harmônica total.

#### ABSTRACT

This work presents a theoretical comparison between three distinct criteria for evaluating distortion of analog multipliers: the two-dimensional integral nonlinear function and the double input total harmonic distortion, both proposed by our research group in Laboratório de Concepção de Circuitos Integrados (LCCI) at Universidade Federal da Bahia (UFBA), and the conventional single input total harmonic distortion. Methodologies are proposed to determine these figures of merit using DC characterization. Besides the direct determination of two-dimensional integral nonlinear function, the distortion coefficients calculated to fit the DC transfer surface are used to estimate the total harmonic distortions for single and double input. Simulation and experimental results obtained from four different topologies of CMOS analog multipliers demonstrate that the figures of merit determined either by AC or DC analysis may be consistent. We also illustrate how to take advantage of the distortion analysis of analog multipliers through DC characterization to establish design and implementation guidelines for the circuit with the aim of minimizing distortion. For this purpose, two CMOS voltage-mode analog multipliers are theoretically analyzed to relate the distortion coefficients of their DC transfer surfaces to the technology parameters and to the geometry of the transistors.

Keywords: distortion; analog multiplier; integral nonlinear function; total harmonic distortion.

# **SUMÁRIO**

| 1.  | CA            | APÍTULO 1 – INTRODUÇÃO                                                              | 17      |

|-----|---------------|-------------------------------------------------------------------------------------|---------|

| 1   | 1.1.          | Contextualização do problema                                                        | 17      |

| 1   | 1.2.          | Objetivos                                                                           | 21      |

| 1   | 1.3.          | Organização da tese                                                                 | 22      |

| 2.  | CA            | APÍTULO 2 - FUNDAMENTAÇÃO TEÓRICA                                                   | 23      |

| 2   | 2.1.          | Multiplicadores analógicos em Tecnologia CMOS                                       | 23      |

|     |               | 2.1.1 Modos de operações e topologias de circuitos                                  | 27      |

|     |               | 2.1.1.Resumo                                                                        | 37      |

| 2   | 2.2.          | Critérios e Métodos para Análise de Distorção                                       | 38      |

|     |               | 2.2.1Critérios Clássicos para Análise de Distorção                                  | 38      |

| 2   | 2.2.21        | Distorção Harmônica Total com Sinais Senoidais nas Duas Entradas—THD <sub>2in</sub> | 40      |

|     |               | 2.2.3Método da Função Integral-IFM                                                  | 42      |

|     |               | 2.2.3.1Função Não Linear Integral-INFL                                              | 42      |

|     |               | 2.2.3.2Função Não Linear Integral em Duas Dimensões -2D-INLF                        | 42      |

| 2   | 2.3.          | Expressões Teóricas das Figuras de Distorção em termos dos Coeficientes de Di       | storção |

|     |               |                                                                                     | 44      |

| 2   | 2.4.          | Princípios de uma CNN teórica                                                       | 48      |

|     |               | 2.4.1Célula do tipo FSR                                                             | 51      |

| 3.  | CA            | APÍTULO 3 – METODOLOGIAS PARA ANÁLISE DE DISTORÇÃO                                  | ) EM    |

| MU  | J <b>LT</b> I | IPLICADORES                                                                         | 52      |

| 3   | 3.1.          | Dispositivos Testados                                                               | 52      |

| 3   | 3.2.          | Descrição do Método Experimental da 2D-INLF                                         | 56      |

|     |               | 3.2.1Método experimental                                                            | 56      |

|     |               | 3.2.2 Método por simulação                                                          | 59      |

|     |               | 3.2.3 Método pela superfície ajustada                                               | 59      |

| 3   | 3.3.          | Descrição dos Métodos para Determinação da THD e da THD <sub>2in</sub>              | 61      |

|     |               | 3.3.1Método experimental por Análise AC                                             | 62      |

|     |               | 3.3.2 Método por simulação                                                          |         |

|     |               | 3.3.3 Método por análise DC                                                         |         |

| 3   | 3.4.          | Resumo                                                                              |         |

| 4.  | CA            | APÍTULO 4 - RESULTADOS EXPERIMENTAIS E DE SIMULAÇÃO                                 | 66      |

| 4   | 1.1.          | Coeficientes de Distorção                                                           | 66      |

| 4   | 1.2.          | Resultados Experimentais e de Simulação                                             | 69      |

| 4   | 1.3.          | Discussão                                                                           | 76      |

| 5.  | CA            | APÍTULO 5 – RELAÇÃO ENTRE A DISTORÇÃO E LIMITAÇÕES                                  | NOS     |

| DIS | SPO           | SITIVOS E CIRCUITOS                                                                 | 78      |

| Considerações Preliminares                                       | 78                    |  |  |  |  |  |  |

|------------------------------------------------------------------|-----------------------|--|--|--|--|--|--|

| Multiplicador de Sawigun                                         |                       |  |  |  |  |  |  |

| Multiplicador de Mahmoud                                         | 81                    |  |  |  |  |  |  |

| Variação dos parâmetros                                          | 83                    |  |  |  |  |  |  |

| 5.4.1 Multiplicador de Sawigun                                   | 84                    |  |  |  |  |  |  |

| 5.4.2 Multiplicador de Mahmoud                                   | 85                    |  |  |  |  |  |  |

| Contribuição dos coeficientes de distorção para o sinal de saída | 88                    |  |  |  |  |  |  |

| APÍTULO 6 - DISTORÇÃO NA OPERAÇÃO DE UMA CNN                     | 93                    |  |  |  |  |  |  |

| APÍTULO 7 - CONCLUSÃO                                            | 98                    |  |  |  |  |  |  |

| REFERÊNCIAS BIBLIOGRÁFICAS101                                    |                       |  |  |  |  |  |  |

| DICE A                                                           | 106                   |  |  |  |  |  |  |

| DICE B                                                           | 107                   |  |  |  |  |  |  |

| DICE C                                                           | 109                   |  |  |  |  |  |  |

|                                                                  |                       |  |  |  |  |  |  |

| DICE E                                                           |                       |  |  |  |  |  |  |

|                                                                  | APÍTULO 7 - CONCLUSÃO |  |  |  |  |  |  |

# CAPÍTULO 1 INTRODUÇÃO

## 1.1. Contextualização do Problema

Multiplicadores analógicos são processadores de sinais analógicos de pelo menos duas entradas e uma saída, com importantes aplicações em instrumentação e em sistemas de comunicações. Em geral se apresentam nas formas de um, dois ou quatro quadrantes, dependendo de quais sinais de entrada podem assumir valores positivos ou negativos.

A vasta aplicabilidade dos multiplicadores analógicos como blocos de construção de circuitos eletrônicos para processamento e comunicação de sinais analógicos é incontestável (HAN e SANCHEZ, 1998) (CARDOSO et al, 2018). Entre outros papéis, eles atuam como moduladores, dobradores de frequência e elementos de sinapse em redes neuronais analógicas. Nos sistemas de instrumentação é possível também incluir multiplicadores analógicos em suas implementações, como por exemplos, em wattímetros, detectores de fase, densitômetros e medidores de vazão (ANALOG DEVICES, 1978).

Na prática, por causa de aspectos associados à sua implementação, os multiplicadores exibem características de transferência com distorção. Limitando-se às aplicações em baixas e médias frequências dos multiplicadores analógicos, é possível identificar diversos exemplos em que o nível de distorção introduzido pelo multiplicador pode ser crítico. No campo do processamento analógico de sinais, podem ser citados:

(i) Conversores RMS (valor eficaz) para DC (valor constante) (ANALOG DEVICES, 1978): nesta aplicação, os sinais de entrada  $v_{in}$  e saída  $v_{out}$  do circuito se relacionam segundo a equação  $(v_{in}+v_{out})(v_{in}-v_{out})=\tau.(dv_{out}/dt)$ , sendo  $\tau$  uma constante de tempo. Nesta expressão, o termo da esquerda é obtido por meio de um multiplicador analógico. Espera-se que no regime permanente ou para variações lentas de  $v_{out}$ , a equação resulte na igualdade aproximada entre o valor médio de  $v_{in}^2$  e o valor  $v_{out}^2$ , sendo  $v_{out}$ , pois, uma aproximação para a raiz média quadrática (valor rms) de  $v_{in}$ . Entretanto, a acurácia desta aproximação depende do cancelamento de termos na equação do sistema, o que pode não ser atingido de forma satisfatória em virtude de distorção presente na operação do multiplicador.

- (ii) Dobradores de frequência (ANALOG DEVICES, 1978): neste caso, o multiplicador é configurado para operar como quadrador (o mesmo sinal é aplicado às duas entradas). Ao se aplicar um tom à entrada do dobrador, o resultado é constituído de um valor constante, que pode ser bloqueado capacitivamente, e um tom uma oitava acima, conforme a equação ideal:  $\sin^2(\omega t) = [1 \cos(2\omega t)]/2$ . Contudo, a presença de distorção na operação do multiplicador deve fazer aparecer outros tons, em frequências múltiplas da frequência do sinal de entrada. Por exemplo, suponha-se que a relação de transferência real do multiplicador tenha a forma:  $z = K_1 x.y + K_2 x^2 y$ , onde x e y são os sinais de entrada, z é o sinal de saída,  $K_1$  é o ganho do multiplicador e  $K_2$  é um coeficiente de distorção. Neste caso, a operação como quadrador dá origem a senóides nas frequências  $\omega$ ,  $2\omega$  e  $3\omega$ .

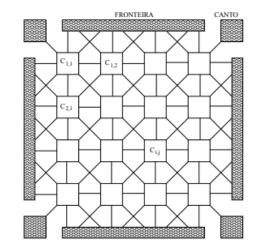

- (iii) Redes neuronais celulares (CNN, do inglês: cellular neural networks) analógicas (SANTANA et al, 2012): trata-se de uma classe de circuitos analógicos densos, muito adequados ao processamento analógico de imagens. Estas redes consistem de matrizes retangulares de células circuitais, onde cada célula compreende vários blocos multiplicadores que realizam o produto dos sinais de entrada e de saída da própria célula em questão e de células vizinhas por coeficientes de ponderação, os chamados operadores sinápticos. Os valores destes coeficientes definem a função que será realizada pela rede sobre a imagem (detecção de bordas, projeção de sombras, filtragens diversas, entre tantas outras). Para exemplificar, uma rede de dimensões 64 x 64 e com vizinhança de raio unitário (cada uma das 64<sup>2</sup> células relacionando-se com oito vizinhas e com ela mesma), o número de multiplicadores pode chegar a 77824. A operação ligeiramente distorcida destes numerosos multiplicadores pode ter um efeito cumulativo e degradar de forma dramática o processamento executado pela rede sobre a imagem.

Estes exemplos ilustram intuitivamente como limitações presentes na operação dos multiplicadores podem afetar a função global do circuito e o quanto é importante estimar o nível de distorção dos multiplicadores como parte de sua avaliação de desempenho.

Nos multiplicadores a distorção geralmente é devida a não idealidades na operação de dispositivos eletrônicos, bem como na topologia do circuito. O esquema de cancelamento aplicado com o objetivo de suprimir os sinais indesejáveis à multiplicação está fortemente condicionado a um perfeito casamento entre as características dos dispositivos. A dependência das tensões de alimentação e da temperatura também pode afetar o nível de distorção. Devido a todas essas razões, figuras de mérito, significativas, confiáveis e completas para avaliar a distorção em multiplicadores analógicos são essenciais.

No entanto, a natureza de duas entradas dos multiplicadores analógicos e as especificações da faixa de variação do sinal, tornam difícil determinar com precisão o nível de distorção. O erro de linearidade (também conhecido por não linearidade) percentual em relação ao fundo de escala é um parâmetro DC calculado separadamente para cada entrada do multiplicador, considerando a outra fixa em um valor constante (ANALOG DEVICES, 1977) (ANALOG DEVICES, 2012). Também é amplamente adotado pelos projetistas de circuitos analógicos para comparar o desempenho de diferentes arquiteturas dos multiplicadores analógicos (ALIKHANI e AHMADI, 2012) (TANNO et al, 2000), assim como a THD (distorção harmônica total, do inglês: Total Harmonic Distortion) (CARDOSO et al, 2018) (ALIKHANI e AHMADI, 2012) (SAWIGUN e PAL, 2007). A THD e a IM<sub>n</sub> (intermodulação de enésima ordem) são figuras de mérito clássicas, que avaliam o nível de distorção em circuitos dos quais se espera um comportamento linear. São normalmente calculadas a partir de análises AC a fim de identificar componentes de frequências estranhas à resposta ideal do circuito. Isto pode ser realizado tanto por análise espectral do sinal, aplicada diretamente, quanto por análise de Fourier aplicada a formas de onda de amplitudes significativas (grandes sinais variando no domínio do tempo). Em multiplicadores, estas figuras de mérito são levantadas para cada entrada com a outra fixada num valor constante, normalmente correspondente ao valor absoluto do fundo de escala especificado para o circuito.

Outro critério baseado em análise AC para avaliar o comportamento das distorções presentes em multiplicadores ou, de um modo geral, circuitos com duas entradas, consiste na THD<sub>2in</sub>, método proposto por (GONÇALVES, 2015) (LACERDA et al, 2009), que, ao contrário da THD simples, considera as variações em ambas as entradas do multiplicador simultaneamente.

Dentre os critérios baseados em caracterização DC, além do já mencionado erro de linearidade, podemos citar a INLF (função não linear integral, do inglês: *integral*

nonlinear function) (CERDEIRA et al., 2001) (GARCÍA-SÁNCHEZ et al.,2002) (SALAZAR et al, 2007) (CERDEIRA et al, 2004), para circuitos de entrada simples, e a 2D-INLF (função não linear integral de duas dimensões), método proposto por (GONÇALVES, 2015, 2016) (LACERDA et al, 2009), que permite avaliar a influência simultânea das duas entradas do multiplicador.

Foi argumentado em (GONÇALVES, 2015, 2016) que métodos experimentais baseados em análise AC para levantamento direto de figuras de mérito tradicionais demandam a medição de sinais de tensão por instrumentos como o analisador de espectros ou o osciloscópio. No caso de circuitos com saída em corrente, um conversor correntetensão deve ser inserido em sua saída, introduzindo sua própria distorção e, portanto, modificando os valores de distorção harmônica ou intermodulação gerados exclusivamente pelo circuito a ser analisado.

Em (GONÇALVES, 2015, 2016), é discutida também a incompletude da análise de distorção por critérios que levam em consideração apenas uma entrada simples, como é o caso do erro de linearidade, obtido por análise DC, ou a THD simples e a intermodulação, obtidas por análise AC. Foi destacado que a operação simultânea das duas entradas incorporam elementos de distorção não apresentados quando a análise é realizada admitindo variação em apenas uma entrada, enquanto a outra é fixada num valor constante, em geral o valor absoluto do fundo de escala. Isto, frequentemente leva a um nível subestimado de distorção.

Por estas razões, o critério da 2D-INLF, cuja validação experimental na quantificação do grau de distorção de multiplicadores analógicos foi objeto de (GONÇALVES, 2015, 2016), desponta como um método confiável e operacional. Além disto, requer uma caracterização DC tridimensional para sua determinação, caracterização esta que permite o levantamento dos coeficientes de distorção dos multiplicadores, com os quais é possível estimar outras figuras de mérito, inclusive as baseadas em análise AC, procedimento este que é objeto da pesquisa aqui relatada.

De fato, a determinação dos coeficientes de distorção, a partir do ajuste de uma função polinomial de duas entradas à característica DC tridimensional do multiplicador, é um expediente versátil, pois permite também, mediante uma análise do circuito com o uso de modelos teóricos para os dispositivos, identificar a contribuição para a distorção de limitações da arquitetura e de não idealidades dos dispositivos eletrônicos constituintes do multiplicador. Outros sim, utilizando estes coeficientes é possível avaliar o impacto

do nível de distorção em aplicações práticas de multiplicadores, como é o caso das sinapses de redes neuronais celulares (CNN).

### 1.2 Objetivos

O objetivo principal deste trabalho de pesquisa é realizar um estudo comparativo sobre a utilização dos critérios da 2D-INLF, THD<sub>2in</sub> e THD na avaliação do nível de distorção em multiplicadores analógicos, por meio de análises AC e DC. Em (GONÇALVES et al, 2016) são apresentados argumentos sólidos de que a determinação dos coeficientes de distorção por meio da análise DC é suficiente para fornecer um cenário representativo das limitações do circuito devidas à distorção, permitindo dessa forma uma boa estimativa tanto para as figuras de mérito DC como AC. Esses coeficientes de distorção são extraídos por meio das superfícies características de transferência DC medidas ou simuladas.

Os objetivos específicos deste trabalho são:

- i. Dar continuidade à validação do critério da 2D-INLF por comparação com os métodos tradicionais, utilizando dados experimentais e obtidos por simulação. Em (GONÇALVES 2015), o levantamento experimental da THD e da THD<sub>2in</sub> nos dispositivos sob teste, multiplicadores analógicos integrados de alta precisão, não logrou sucesso em virtude da inadequação dos equipamentos disponíveis.

- ii. Demonstrar a confiabilidade dos valores das figuras THD e THD<sub>2in</sub>, estimados pela aplicação de coeficientes de distorção, levantados a partir de características DC tridimensionais (sinal de saída versus dois sinais de entrada), sendo estas figuras tradicionalmente determinadas por análise AC.

- iii. Aplicação dos critérios da 2D-INLF, da THD simples e da THD<sub>2in</sub> em dados obtidos por simulação de um multiplicador projetado especificamente para utilização como sinapses de CNN, para comparação.

- iv. Relacionar os coeficientes de distorção com parâmetros de circuito e de modelagem dos dispositivos para avaliar a contribuição destes

- na distorção de dois exemplos de multiplicadores, visando estabelecer diretrizes de projeto que possam mitigar o problema.

- v. Avaliar o impacto da distorção dos multiplicadores nas operações de processamento de imagens por uma CNN, em alguns exemplos de funções.

### 1.3 Organização da tese

No capítulo 1 apresentou-se a contextualização, a justificava para o desenvolvimento do presente trabalho e os seus objetivos e ainda foram introduzidos conceitos para auxiliar na construção e delimitação do tema proposto para a pesquisa. O capítulo 2 descreve os fundamentos teóricos sobre os multiplicadores, os métodos e critérios para avaliação de distorção, relações teóricas das figuras de distorção em termos de coeficientes de distorção e os princípios de uma rede celular neuronal (CNN). No capítulo 3 descrevem-se os circuitos multiplicadores testados, assim como as metodologias aplicada aos mesmos para determinação da THD, da THD<sub>2in</sub> e da 2D-INLF. No capítulo 4 são apresentados os resultados experimentais e de simulação para as figuras de mérito THD, THD<sub>2in</sub> e 2D-INLF. No capítulo 5 são apresentadas as relações entre a distorção dos multiplicadores e as limitações nos dispositivos e circuitos que os realizam. No capítulo 6 são apresentados os resultados obtidos na operação de processamento de imagem de uma CNN implementada teoricamente em um código executável no *software* MATLAB, no caso de as sinapses apresentarem certo nível de distorção. para o processamento de imagem. E, por fim, no capítulo 7 é apresentada a conclusão.

## **CAPÍTULO 2**

# **FUNDAMENTAÇÃO TEÓRICA**

## 2.1 Multiplicadores Analógicos em Tecnologia CMOS

A multiplicação analógica em tempo real de dois sinais é um dos processos de operação mais importantes em processamento de sinais analógicos. Os multiplicadores não só são utilizados como blocos de construção computacional, mas também como elementos de programação em sistemas como filtros, redes neuronais, misturadores, moduladores e sistemas de comunicação (HAN e SÁNCHEZ, 1998).

Os multiplicadores analógicos são blocos de circuitos cujo sinal de saída consiste no produto entre os sinais aplicados nas duas entradas, sinais estes que podem variar no tempo.

Apesar dos multiplicadores a transistor bipolar de junção de alto desempenho estarem disponíveis há bastante tempo, a implementação de multiplicadores fabricados na tecnologia CMOS (do inglês: *Complementary Metal-Oxide- Semiconductor*) ainda é um pouco desafiadora, especialmente para projetos de circuitos de baixa tensão e baixa potência. Apesar do grande número de artigos que propõem novas estruturas de multiplicadores com a tecnologia *Metal-Oxide-Semiconductor* (MOS), eles podem ser mais ou menos alocados em poucas categorias. (HAN e SÁNCHEZ, 1998)

Os multiplicadores analógicos a MOSFET em geral demandam menores tensões de alimentação que seus congêneres a TBJ. Além disto são compatíveis com a tecnologia CMOS, adequada para a fabricação de circuitos ditos de modo misto, ou seja, com a porção analógica e digital na mesma pastilha.

O produto linear de um multiplicador com dois sinais de entrada x e y apresenta uma saída igual a z=K.x.y, em que: K é a constante de multiplicação com dimensão adequada. Os multiplicadores podem ser caracterizados como: de um quadrante (x e y são unipolares, ou seja, os dois sinais de entrada devem ser não negativos), de dois quadrantes (ou x ou y pode ser bipolar, ou seja, apenas um dos sinais pode ser positivo ou negativo) e de quadrantes (ambos, x e y, podem ser bipolares). Em geral, a multiplicação de 2 ou 4 quadrantes é obtida pela conexão de estágios de 1 quadrante.

Os multiplicadores são sistemas não-lineares que apresentam algumas limitações, como, por exemplo, o ruído e a largura de banda não otimizados. Exemplos de aplicações

de multiplicadores em que as especificações de ruído e banda são determinantes são os moduladores e os misturadores. (HAN e SÁNCHEZ, 1998)

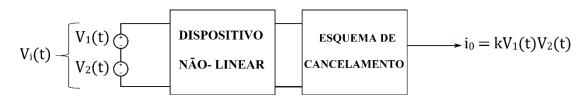

A ideia básica da implementação de um multiplicador pode ser observada na Figura 2.1, em que dois sinais  $v_1(t)$  e  $v_2(t)$  são aplicados a um dispositivo não linear, que pode ser caracterizado por uma função polinomial. Esta função gera termos como:  $v_1^2(t)$ ,  $v_2^2(t)$ ,  $v_1^3(t)$ ,  $v_2^3(t)$ ,  $v_1(t)v_2^2(t)$  e muitos outros termos estranhos ao termo desejado  $v_1(t)v_2(t)$ . Para cancelar os componentes indesejados é criado um esquema de cancelamento (HAN e SÁNCHEZ, 1998).

Figura 2.1 – Configuração básica de um multiplicador

Fonte: [HAN e SÁNCHEZ, 1998]

Em trabalhos técnicos, científicos e didáticos, as principais características de desempenho analisadas em multiplicadores são:

i. Linearidade em relação a cada entrada: as características no plano de duas dimensões da saída(z) versus uma das entradas (x ou y), assumindo que a outra entrada (y ou x) é constante, devem ter um bom grau de linearidade, que pode ser avaliado pelo erro médio quadrático ou outro critério. Por exemplo, em folhas de especificações de multiplicadores analógicos, o "erro de linearidade", também conhecido como "não linearidade", é calculado como a máxima diferença entre as saídas real (z<sub>real</sub>) e teórica, com uma das entradas constante, dividida pelo fundo de escala (z<sub>máx</sub>) e expressa em porcentagem, conforme a equação 2.1:

$$NL(\%) = 100 \frac{\max(z_{real} - K.x.y)}{z_{m\acute{a}x}}$$

(2.1)

em que, NL é a não linearidade e K é a constante de multiplicação

Distorção Harmônica Total: é o somatório das contribuições em potência das componentes de frequências indesejadas presentes no sinal de saída dividido pelas contribuições das componentes desejadas. Tradicionalmente, é computada para uma entrada constante, estando, pois, relacionada a não-linearidade. Sua expressão matemática será apresentada no item 2.2.1;

iii. Faixa dinâmica nas entradas: consiste na razão entra a máxima amplitude  $(A_{máx})$  à entrada, limitada pela não linearidade do circuito, e a amplitude mínima  $(A_{min})$ , limitada pelo ruído:

$$DR = \frac{A_{m\acute{a}x}}{A_{min}} \tag{2.2}$$

em que, DR = *Dynamic Range*

- iv. Largura de banda de frequências;

- v. Mínima tensão de alimentação;

- vi. Potência;

- vii. Área;

- viii. Sensibilidade às variações de processo e ao descasamento de características dos componentes;

- ix. Imunidade ao ruído.

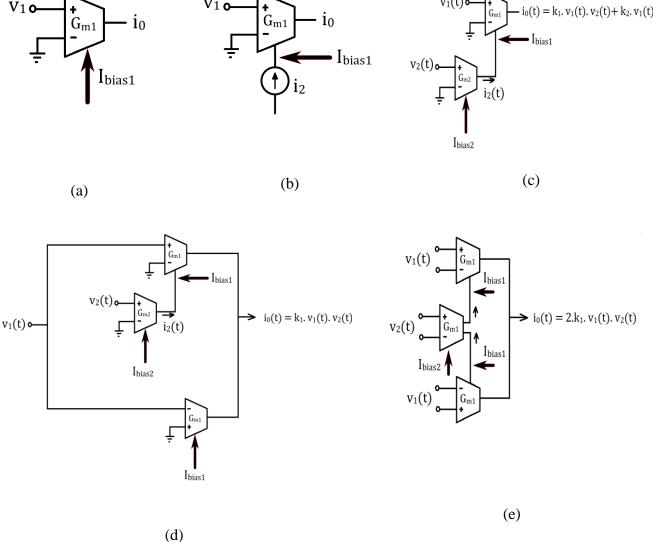

Um multiplicador pode ser realizado utilizando componentes de transcondutância programável. A Figura 2.2(a) considera um amplificador de transcondutância conceitual, no qual a corrente de saída é dada por:

$$i_0 = G_{m1} v_1 \tag{2.2a}$$

em que o ganho de transcondutância  $G_{m1}$  é função da corrente de polarização  $I_{bias1}$ :

$$G_{m1} = G_{m1}(I_{bias1}) \tag{2.2b}$$

Para o transcondutor bipolar,  $G_{m1}$  é calculado por:

$$G_{m1} = \frac{I_{bias1}}{2V_t} \tag{2.2c}$$

em que  $V_t$  é a tensão térmica ( $k_BT/q$ ), sendo  $k_B$  é a constante de Boltzmann, T é temperatura absoluta e q é o valor absoluto da carga eletrônica.

A Figura 2.2 (b) ilustra o caso em que um sinal pequeno  $i_2$  é adicionado à corrente de polarização  $I_{bias1}$ . Este sinal de corrente é gerado a partir do sinal de tensão de entrada  $v_2(t)$ , por meio de um segundo amplificador de transcondutância, tal que  $i_2(t) = G_{m2}v_2(t)$ . Então, de acordo com a Figura 2.2 (c), a corrente de saída ( $i_0$ ) fica:

$$i_o(t) = G_{m1}v_1 = \frac{I_{bias1} + G_{m2} \cdot v_2(t)}{2V_t} v_1(t)$$

(2.3a)

Substituindo  $G_{m2} = \frac{I_{bias2}}{2V_t}$ :

$$i_o(t) = \frac{G_{m2}.v_1(t).v_2(t)}{2V_t} + \frac{I_{bias1}}{2V_t}v_1(t) = \frac{I_{bias2}.v_1(t).v_2(t)}{2V_t.2V_t} + \frac{I_{bias1}.v_1(t)}{2V_t}$$

(2.3 b)

Ou, simplificando a notação:

$$i_0(t) = k_1 \cdot v_1(t) \cdot v_2(t) + k_2 \cdot v_1(t)$$

(2.3c)

em que

$$k_1 = \frac{I_{bias2}}{4V_t^2}$$

e  $k_2 = G_{m1} = \frac{I_{bias1}}{2V_t}$ .

Portanto,  $i_o(t)$  representa a multiplicação de dois sinais  $v_1(t)$  e  $v_2(t)$  e uma componente indesejada  $k_2v_1(t)$ . Esta componente pode ser eliminada, conforme a ilustração da Figura 2.2(d), na qual a corrente de saída de um terceiro amplificador de transcondutância, com ganho  $G_{m1}$  e sinal de entrada  $v_1(t)$ , é subtraído da saída. Entretanto, a melhor opção de cancelamento é alcançada quando o transcondutor de ganho  $G_{m2}$  é do tipo diferencial na entrada e na saída, enquanto os dois transcondutores de ganho  $G_{m1}$  são utilizados na forma diferencial para os sinais de entrada  $v_1$  e  $v_2$ , conforme ilustrado na Figura 2.2 (e). Neste caso,  $i_o(t)$  torna-se:

$$i_0(t) = 2k_1 \cdot v_1(t) \cdot v_2(t)$$

(2.4)

Este é o princípio básico de operação da Célula de Gilbert (*Gilbert Cell*) (HAN e SÁNCHEZ, 1998). O circuito da Célula de Gilbert pode ser obtido substituindo os transcondutores ilustrados na Figura 2.2(e) por pares diferenciais de Transistores Bipolares de Junção (TBJ).

Um problema que os projetistas encontram com frequência é como selecionar a melhor arquitetura de multiplicador para as aplicações por eles visadas. Normalmente, as propostas de multiplicadores apresentadas em trabalhos científicos não são em geral comparadas com outras, o que dificulta esta escolha, como reportado em (HAN e SÁNCHEZ, 1998), mas ainda constatado em publicações mais recentes.

$G_{m1} \\$ 10

Figura 2.2 - Operação do multiplicador utilizando transcondutor programável

Fonte: [HAN e SÁNCHEZ, 1998]

## 2.1.1 Modos de operações e topologias de circuitos

Segundo (HAN e SÁNCHEZ, 1998), os multiplicadores podem ser divididos em dois grupos com base na região de operação dos dispositivos empregados. Deve-se enfatizar que a topologia do núcleo fundamental do multiplicador é a mesma para muitos dos multiplicadores. A classificação dos multiplicadores é feita de acordo com diferentes critérios, como região de operação do transistor, esquemas de cancelamento e método de injeção de sinal (HAN e SÁNCHEZ, 1998). Esta classificação continua atual, de acordo revisão bibliográfica levada a efeito no presente trabalho.

Os princípios que regem a operação de multiplicadores analógicos são:

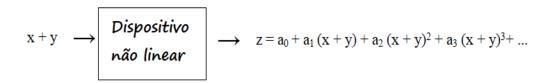

i. Por dispositivo não linear: em que, conforme a ilustração da Figura 2.3 o termo desejado na saída está embutido no termo de  $2^a$  ordem:  $a_2(x + y)^2 = a_2.x^2 + 2.a_2x.y + a_2y^2$ .

Figura 2.3 – Dispositivo não linear

A combinação de estruturas como esta e um esquema de cancelamento garante a eliminação dos termos indesejados;

ii. Por transcondutância programável (Célula de Gilbert).

Esquemas de cancelamento: são utilizados em combinação com núcleos de multiplicadores com duas finalidades:

- a. Eliminação das componentes indesejadas naturalmente geradas pelos núcleos multiplicadores que seguem os princípios de operação por dispositivo não linear ou por transcondutância programável.

- b. Realização da multiplicação em quatro quadrantes: como normalmente é necessário acrescentar sinais de polarização aos sinais que devem ser multiplicados para aplicá-los a um núcleo multiplicador de um quadrante, podem-se combinar as saídas de quatro núcleos de um quadrante em um esquema de cancelamento para eliminar termos oriundos destes sinais de polarização.

De acordo com (HAN e SÁNCHEZ, 1998), dois métodos de cancelamento são identificados:

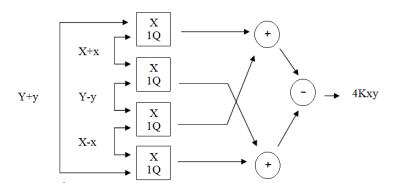

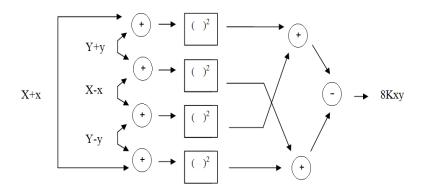

Método de cancelamento baseado em núcleos de multiplicadores de um quadrante, ilustrado na Figura 2.4: Neste caso:

$$z = K(X+x)(Y+y) + K(X-x)(Y-y) + K(X-x)(Y+y) - K(X+x)(Y-y)$$

$$z = K[XY+xy+Xy+Yx+XY+xy-Xy-Yx] + K[XY-xy+Xy-Yx+XY-xy-Xy-Yx]$$

$$z = K[2XY+2xy] - K[2XY-2xy] = 4Kxy$$

(2.5.b)

Note-se que as componentes de polarização são eliminadas.

Figura 2.4 – Esquema de cancelamento baseado em núcleos multiplicadores de um quadrante

Fonte: [HAN e SÁNCHEZ, 1998]

• Esquema baseado em núcleos quadradores, ilustrado na Figura 2.5.

Figura 2.5 – Esquema de cancelamento baseado em núcleos quadradores

Fonte: [HAN e SÁNCHEZ, 1998]

Neste caso:

$$z = K (X + x + Y + y)^{2} + K (X - x + Y - y)^{2} +$$

$$-K (X - x + Y + y)^{2} + K (X + x + Y - y)^{2}$$

$$z = K [X^{2} + 2Xx + x^{2} + 2XY + 2xy + 2Yx - 2Xy + Y^{2} + 2Yy + y^{2}] +$$

$$+ K [X^{2} - 2Xx + x^{2} + 2XY + 2xy - 2Yx - 2Xy + Y^{2} - 2Yy + y^{2}] +$$

$$-K [X^{2} - 2Xx + x^{2} + 2XY - 2xy - 2Yx + 2Xy + Y^{2} - 2Yy + y^{2}] +$$

$$-K [X^{2} + 2Xx + x^{2} + 2XY - 2xy + 2Yx - 2Xy + Y^{2} - 2Yy + y^{2}]$$

$$z = K [2X^{2} + 2x^{2} + 4XY + 4xy + 2Y^{2} + 2y^{2}] +$$

$$-K [2X^{2} + 2x^{2} + 4XY + 4xy + 2Y^{2} + 2y^{2}] = 8Kxy$$

$$(2.6.c)$$

As topologias ilustradas na Figura 2.4 e na Figura 2.5 efetuam a multiplicação e simultaneamente o cancelamento de todos os componentes de alta ordem e de modo comum.

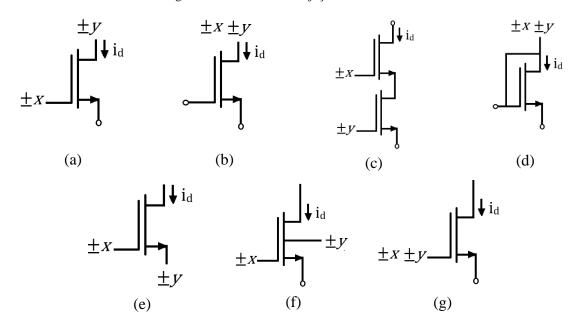

A Figura 2.6 ilustra os métodos de aplicação dos dois sinais de entrada (x e y) no caso de se utilizar um MOSFET. O pequeno círculo no terminal do transistor representa a tensão de polarização fixa, e x e y são sinais de tensão variáveis no tempo. O primeiro, dos três métodos são utilizados para transistores operando em sua região linear e os outros dois são para transistores operando em saturação.

Figura 2.6 – Metodos de injeção de sinal em tensão

Fonte: [HAN e SÁNCHEZ, 1998]

Os multiplicadores podem operar com entradas em modo tensão, em modo tensão-corrente ou em modo corrente e diversas podem ser as implementações de suas arquiteturas. Com o intuito de proporcionar uma visão geral de como os multiplicadores analógicos em tecnologia CMOS são inovados em diversos trabalhos, segue uma breve compilação de algumas publicações científicas na área. Os critérios utilizados para avaliar distorção, quando for o caso, são também indicados:

- Em (HASAN, 2005) um novo multiplicador de quatro quadrantes em tecnologia CMOS de 0,18 μm é proposto, com projeto escalável, faixa de variação do sinal grande e ampla largura de banda, permitindo aplicações numerosas em processamento de sinais de comunicação. O multiplicador opera em uma faixa de tensão ajustável para tensão de alimentação entre 3,3 V e 1 V, com a faixa dinâmica da entrada máxima de 500 mV, no caso de tensão de alimentação de 3,3 V. Apresenta um valor de THD típico em torno de -56 dB.

- Em (HUANG et al, 2006) uma estrutura nova de circuito para multiplicador analógico de quatro quadrantes em tecnologia CMOS é apresentada, em que a técnica de realimentação ativa é utilizada para se obter alta linearidade e uma ampla faixa dinâmica de entrada. Os resultados simulados mostram que o multiplicador proposto pode oferecer uma faixa dinâmica de entrada de ±1,8 V, e para a tensão de alimentação de ±2,5 V, sendo esses valores muito maiores do que nos multiplicadores analógicos em tecnologia CMOS convencionais. Para analisar o nível de distorção no circuito foi utilizada uma das figuras de mérito clássicas, a THD.

- Em (AL-ABSI et al, 2012) é proposto um novo multiplicador analógico CMOS em modo corrente. O projeto é baseado na operação do MOSFET na região de sublimar, para reduzir a dissipação de potência a um mínimo. O multiplicador proposto trabalha com tensões DC de alimentação de ±0,75 V. O nível de distorção no circuito é analisado por meio da THD, a qual é 0,7 % e o erro de linearidade máximo é de 0,3 %.

- Em (SANTANA et al, 2012) uma nova arquitetura de multiplicador analógico de quatro quadrantes em tecnologia CMOS IBM 0,13 μm é apresentada, com tensões de alimentação de ±0,6 V. Ele é baseado no comportamento do MOSFET na região linear (dispositivo de entrada),

podendo todos os dispositivos operar de inversão fraca a forte. O multiplicador proposto possui uma entrada em tensão e a outra em corrente e a saída em corrente. A Distorção Harmônica Total (THD) foi avaliada por meio de simulação, tendo-se observado valores inferiores a aproximadamente –43 dB (0,7%) para toda a gama de tensões de entrada, mantendo-se constante a corrente de entrada, e valores inferiores a –34 dB (2%) para todo o intervalo de correntes de entrada, mantendo-se constante a tensão de entrada. O multiplicador proposto é adequado para implementação de sinapses compactas para CNN e os resultados obtidos por simulação exibiram baixo consumo de energia e baixa distorção.

- Em (SAATLO et al, 2015), um novo multiplicador de quatro quadrantes baseado em uma nova configuração simétrica, projetado em tecnologia CMOS é proposto. O circuito é adequado para aplicações de baixa potência e baixa tensão. Comparado com alguns trabalhos análogos publicados, as faixas dinâmicas de entrada e saída do circuito são melhoradas pelo fato de que os dispositivos operam na região de saturação, mas não em inversão fraca. Uma grande vantagem desse circuito é a alta precisão. A sua tensão de alimentação é de 1,5 V, a faixa de variação da entrada é de ±400 mV, a potência total é de 44 μW e a não-linearidade é abaixo de 1,5%.

- Em (SATAPATHY et al, 2015) um somador de tensão de cinco transistores, consistindo de um seguidor de tensão do tipo *flipped*, projetado para trabalhar com uma baixa tensao de alimentação, é utilizado como bloco de construção principal no projeto do mutiplicador analógico. Quatro dessas células foram usadas para polarização e processamento dos sinais. Este multiplicador foi projetado usando a tecnologia CMOS GPDK de 90 nm, assumindo tensão de alimentação de1 V. No pior caso, o multiplicador apresenta 178 μW de potência e trabalha satisfatoriamente até 454,56 MHz com menos de 1,5% de distorção harmônica total (THD).

- Em (BAHARMAST et al, 2016) multiplicadores analógicos em tecnologia CMOS em modo corrente são brevemente revisados e categorizados e um novo multiplicador analógico de quatro quadrantes é proposto. A nova estrutura do circuito é baseada em laços translineares (do inglês: translinear loops) e é empregada em três novos circuitos quadradores

- compactos. As vantagens do circuito proposto são: estrutura mais simples, baixa potência (89,2 µW), baixa THD (1,01%), grande largura de banda (840 MHz) e resistência de entrada independente da corrente de entrada.

- Em (RENGE et al, 2016) é apresentado um multiplicador de quatro quadrantes em modo corrente, constituído de quatro circuitos quadradores, que, de acordo com os autores, consistem de espelhos de corrente operando a uma tensão de alimentação de 2 V. No projeto do circuito proposto, todos os transistores das células quadradoras estão operando na região de saturação. A potência do multiplicador é de 146,48 μW. Os parâmetros utilizados para a otimização do desempenho do multiplicador proposto são: elevada faixa do sinal de entrada, baixa tensão de alimentação e baixa potência. Nenhuma análise para avaliar a distorção no multiplicador foi apresentada.

- Em (TIJARE e DAKHOLE, 2017) foram relatadas duas diferentes implementações de circuitos multiplicadores analógicos de quatro quadrantes em tecnologia CMOS, ambas em modo corrente. Quadradores de corrente e laços translineares são blocos básicos nestas estruturas, que são embasadas por equações matemáticas e são de fácil realização. As estruturas dos multiplicadores propostos foram projetadas em tecnologia CMOS de 180 nm com tensões de alimentação de 1,8 V e 1,2 V. Elas apresentam, respectivamente, larguras de banda de 493 MHz e 75 MHz e potências de 146,78 μW e 36,08 μW. Nenhuma análise para avaliar a distorção no multiplicador foi apresentada.

- Em (BAXEVANAKIS e SOTIRIADIS, 2017) é apresentado um multiplicador de quatro quadrantes em tecnologia CMOS, visando servir como bloco autônomo para processamento de sinais de baixa frequência. O principal propósito do circuito é reduzir o ruído na saída por meio de um *chopper* de estabilização, enquanto a operação do multiplicador é baseada no princípio translinear. A técnica de *chopper* de estabilização tem sido bastante utilizada em amplificadores para suprir o *offset* DC e reduzir o ruído de baixas frequências. Foi utilizada a linearidade para avaliar a distorção do multiplicador.

- Em (ALTHOMALI, 2017) é proposto um novo multiplicador EPDM ("Exponential Pulse Decay Modulation Technique") baseado na técnica

de carga dinâmica. A estrutura alternativa de multiplicador EPDM proposta neste trabalho utiliza resistores emulados pela dupla configuração diferencial MOS (do inglês: double MOS differential configuration). Estes resistores ativos compreendem dispositivos casados polarizados na região triodo e possibilitam um aumento da linearidade de saída. A técnica proposta remove as influências das tensões substratofonte e dreno-fonte sobre a resistência do circuito, levando em consideração os efeitos da modulação do comprimento do canal. Este novo multiplicador é adequado para várias arquiteturas de redes neuronais analógicas VLSI. Nenhuma análise para avaliar a distorção no multiplicador foi apresentada.

- Em (ALOUI et al, 2018), reporta-se que, devido ao uso recorrente dos multiplicadores analógicos em processamento de sinais analógicos, muitos estudos foram realizados e desenvolvidos para se obter multiplicadores de alto desempenho. Esse artigo apresenta um multiplicador analógico de quatro quadrantes em modo corrente, sendo ele baseado nas características da lei quadrática do transistor MOS em região de saturação. As características do circuito multiplicador proposto são analisadas por meio do simulador ELDO, com a tecnologia CMOS de 0,18 μm e com uma tensão de alimentação de ±0,75 V. Os resultados do multiplicador analógico mostram que a potência máxima é de 0,8 mW e a THD é de 1,2 % em 1 MHz.

- Em (PAWARANGKOON e SAWIGUN, 2018) é apresentado um multiplicador de quatro quadrantes de baixas potência e tensão. A estrutura proposta, utiliza seis transistores e duas fontes de corrente para formar uma conexão de acoplamento cruzado de quatro células exponenciais excitadas pelo terminal de substrato. O circuito é simulado no CADENCE e utiliza a tecnologia CMOS de 0,35 μm, com potência de 480 nW e tensão de alimentação de 0,8 V. Os componentes harmônicos indesejados localizamse 54,77 dB abaixo das componentes fundamentais.

- Em (CRACAN et al, 2018), apresenta-se uma estrutura baseada em um transistor MOS polarizado em inversão fraca que pode ser utilizada para construir multiplicadores analógicos, divisores, entre outras aplicações. O circuito proposto, produz na saída uma corrente proporcional à tensão

- porta-fonte ( $V_{GS}$ ), que possui, inversamente uma dependência logarítmica da corrente de dreno, a qual é configurada como a corrente de entrada. As operações lineares no domínio logarítmico correspondem a exponenciação, multiplicação ou divisão no domínio antilogarítmico. Nenhuma análise para avaliar a distorção no multiplicador foi identificada.

- Segundo (KANAPYANOV e KRESTINSK. 2018). circuitos multiplicadores analógicos em tecnologia CMOS convencionais, utilizados em diferentes arquiteturas, apresentam problemas linearidade, baixa velocidade de processamento, baixa precisão, grande área e alto consumo de energia. Uma das soluções possíveis para superar esses problemas é utilizar componentes memristivos no projeto dos multiplicadores analógicos, sendo essa a solução proposta pelo artigo. O objetivo do trabalho é comparar a potência e as características gerais dos circuitos multiplicadores que contêm os componentes memristivos com os circuitos multiplicadores convencionais. O circuito proposto é projetado usando tecnologia TSMC CMOS de 180 nm e as simulações foram realizadas no SPICE. Para analisar o nível de distorção no circuito, foi utilizada umas das figuras de mérito clássicas, a THD.

- Em (BOONCHU,2018) é apresentado um multiplicador analógico de quatro quadrantes, com baixa tensão e baixa potência. O projeto é baseado num amplificador de tensão em tecnologia CMOS operando no regime de sub-limiar e num somador de tensão. O circuito, projetado em tecnologia CMOS de 0,18 μm pode operar com faixa de tensão de ±25 mV nas duas entradas, com distorção harmônica de 1.3 %, tensão de alimentação de 0,8 V, consumo de potência de 0,78 μm e largura de banda de 650 kHz.

- Em (SOUSA et al, 2019) o artigo apresenta uma arquitetura de um multiplicador analógico em tecnologia CMOS para aplicações como sinapses em redes neuronais celulares analógicas. O circuito, é composto de duas entradas em modo tensão e um saída em modo corrente. As características de desempenho simuladas foram obtidas do projeto de circuito em tecnologia CMOS de 130 nm e incluem: tensão de entrada de ± 100 mV, potência estática de 23 μW, uma máxima THD de -32dB e banda larga de -3 dB de 51,2 kHz.

- Em (VLASSIS et al, 2019) o artigo apresenta projetos de um quadrador de corrente e de um multiplicador de quatro quadrantes em tecnologia CMOS de 0,18 μm, capazes de operar com tensão de alimentação ultra baixa de 0,5 V e com potência estática muito baixa. No projeto, os dispositivos operam em inversão fraca. A largura de banda é de 0,1 MHz para os dois circuitos (quadrador e multiplicador). A distorção total harmônica (THD) no multiplicador é de -36 dB em 50 kHz, -34 dB em 80 kHz e -32 dB em 100 kHz.

- Em (DANESH et al, 2019) é proposto um circuito multiplicador analógico de quatro quadrantes em modo corrente com uma ampla faixa dinâmica, que utiliza o princípio translinear. O multiplicador proposto é projetado na tecnologia CMOS de 65 nm com os transistores operando em inversão fraca. A potência do multiplicador é de 0,48 μW, aferida por simulação. Ele suporta tensões na entrada de ±200 nA enquanto opera com uma tensão de alimentação de 0,8 V e a THD média é de 1,12 %.

- Em (KONGPOON, 2019) é descrito um multiplicador de corrente classe AB que apresenta boa linearidade, ganho de conversão linearmente ajustável e robustez. O multiplicador proposto é simulado utilizando a tecnologia CMOS AMS de 0,35 μm. Para analisar o nível de distorção no circuito, foi utilizada umas das figuras de mérito clássicas, a THD.

#### 2.1.1.1 Resumo

A tabela 2.1 relaciona os artigos apresentados anteriormente com as figuras de méritos utilizadas para analisar a distorção nos circuitos multiplicadores.

Tabela 2.1 – Multiplicadores x Figuras de mérito

| Artigo                         | <u>Figura de mérito</u>   |  |  |  |

|--------------------------------|---------------------------|--|--|--|

| HASAN, 2005                    | THD                       |  |  |  |

| HUANG et al, 2006              | THD                       |  |  |  |

| AL-ABSI et al, 2012            | THD e erro de linearidade |  |  |  |

| SANTANA et al, 2012            | THD                       |  |  |  |

| SAATLO et al, 2015             | Não linearidade           |  |  |  |

| SATAPATHY et al, 2015          | THD                       |  |  |  |

| BAHARMAST et al, 2016          | THD                       |  |  |  |

| RENGE et al, 2016              | Nenhuma                   |  |  |  |

| TIJARE e DAKHOLE, 2017         | Nenhuma                   |  |  |  |

| BAXEVANAKIS e SOTIRIADIS, 2017 | Linearidade               |  |  |  |

| ALTHOMALI, 2017                | Nenhuma                   |  |  |  |

| ALOUI et al,2018               | THD                       |  |  |  |

| PAWARANGKOON e SAWIGUN,2018    | Análise espectral         |  |  |  |

| CRACAN et al,2018              | Nenhuma                   |  |  |  |

| KANAPYANOV e KRESTINSK, 2018   | THD                       |  |  |  |

| BOONCHU,2018                   | THD                       |  |  |  |

| SOUSA et al, 2019              | THD                       |  |  |  |

| VLASSIS et al, 2019            | THD                       |  |  |  |

| DANESH et al, 2019             | THD                       |  |  |  |

| KONGPOON,2019                  | THD                       |  |  |  |

#### 2.2 Critérios e Métodos para Análise de Distorção

#### 2.2.1Critérios Clássicos para Análise de Distorção

A análise de distorção é um requisito obrigatório para avaliar o desempenho geral de grande parte dos circuitos analógicos. É também muito importante para circuitos integrados analógicos e mistos que utilizam a tecnologia CMOS (LACERDA et al., 2009) (ANDRADE, 2011) (SOUSA, 2010)

As figuras de mérito clássicas mais empregadas para estimar as não linearidades de um circuito são: a THD, que compreende a HD<sub>n</sub> (distorção harmônica de enésima ordem), e a IM<sub>n</sub> (intermodulação de enésima ordem) à qual está associado o IP<sub>n</sub> (ponto de intermodulação de enésima ordem) (CERDEIRA et al, 2004). Uma das características desses métodos é a necessidade de realizar as medições por meio de análise espectral (ou seja, utilizando um analisador de espectros). Alternativamente, podem-se fazer medições no domínio do tempo e o posterior tratamento dos dados por análise de Fourier (LACERDA et al., 2009) (CERDEIRA et al, 2004) (ANDRADE, 2011).

A distorção de enésima ordem (HD<sub>n</sub>) é definida como:

$$HD_{n} = \frac{|C_{n}|}{|C_{1}|}, \qquad (2.7)$$

onde  $C_1$  é a amplitude da componente na frequência fundamental na saída e  $C_n$  é a amplitude da enésima harmônica também na saída (CERDEIRA; ALEMÁN; ESTRADA, 2004) (ANDRADE, 2011).

A THD considera a contribuição das potências de todas as componentes harmônicas na distorção do sinal de saída, sendo calculada pela seguinte equação, na qual aparece também sua relação com a HD<sub>n</sub>:

THD =

$$\frac{\sqrt{\sum_{i=2}^{\infty} |C_i|^2}}{|C_1|} = \sqrt{\sum_{n=2}^{\infty} HD_n^2}$$

(2.8)

Na prática é considerado um número finito de harmônicas para o cálculo da THD, o que é razoável, uma vez que as componentes de frequências muito altas são filtradas pelo próprio sistema de banda limitada.

Com a inclusão da componente DC do sinal de saída C<sub>0</sub>, introduzida pela característica não-linear do circuito, a definição da distorção harmônica total se modifica para (CERDEIRA; ALEMÁN; ESTRADA, 2004) (ANDRADE, 2011) (SOUSA, 2010):

$$THD_{0} = \sqrt{\frac{\left|C_{0}\right|^{2} + \sum_{i=2}^{\infty} \left|C_{i}\right|^{2}}{\left|C_{1}\right|^{2}}}$$

(2.9)

A intermodulação é largamente utilizada em análise de potência, amplificadores RF (radiofrequências) (PEDERSON; MAYARAM, 1991) (VAN DER HEIJDEN, 2002) e em sistemas de comunicações. É particularmente adequada para sistemas de banda estreita, para os quais as componentes harmônicas dos sinais situam-se na banda de rejeição e, por esta razão, são bastante atenuadas. Tais sistemas são considerados de distorção fraca. Contudo, quando a soma de dois ou mais sinais senoidais (tons) de frequências próximas é aplicada a uma mesma entrada de um circuito não linear de banda estreita, surgem componentes em frequências compreendidas dentro da banda de passagem. Nesse caso, o espectro de frequências do sinal de saída contém as frequências fundamentais, as harmônicas (múltiplas das fundamentais) e combinações lineares das mesmas. São as componentes nas frequências correspondentes às diferenças entre as fundamentais e entre as harmônicas que podem se inscrever na banda de passagem do sistema. Na definição de IM<sub>n</sub>, são considerados dois sinais de entrada de frequências angulares  $\omega_1$  e  $\omega_2$  e amplitudes  $A_1$  e  $A_2$ . Existem relações fixas entre IM<sub>n</sub> e HD<sub>n</sub>, válidas para uma larga faixa da amplitude do sinal de entrada (CERDEIRA; ALEMÁN; ESTRADA, 2004) (ANDRADE, 2011):

i. A intermodulação de segunda ordem, considerando as componentes de frequências  $\omega_1 \pm \omega_2$  na saída, é dada por:

$$IM_2 = 2.HD_2$$

(2.10)

ii. A intermodulação de terceira ordem utilizada para amplificadores de banda larga, considerando as componentes de frequências  $\omega_1 \pm 2\omega_2$  e  $\omega_2 \pm 2\omega_1$  na saída e admitindo  $A_1$  e  $A_2$  pequenas e iguais, é dada por:

$$IM_3 = 3.HD_3$$

(2.11)

iii. A intermodulação de terceira ordem utilizada para receptores, admitindo a amplitude  $A_1$  pequena e a amplitude do sinal de interferência  $A_2$  grande, para as componentes de frequências  $\omega_1 \pm 2\omega_2$ , é dada por:

$$IM'_3 = 3.HD_3. \left(\frac{A_2}{A_1}\right)^2$$

(2.12a)

Por outro lado, para as componentes de frequências  $\omega_2 \pm 2\omega_1$ , é dada por:

$$IM_3'' = 3.HD_3.\left(\frac{A_2}{A_1}\right)$$

(2.12b)

O conceito de IP<sub>n</sub>, outro parâmetro ou figura para analisar a distorção, é frequentemente utilizado em amplificadores ou circuitos de comunicação analógicos (PEDERSON; MAYARAM, 1991). Em geral está associado à IM<sub>n</sub>. Consiste no ponto de intersecção entre as extrapolações das partes retilíneas das curvas que representam a potência de saída da componente em uma das frequências de entrada e a potência da enésima componente de intermodulação, traçadas contra a potência de entrada da componente em uma das frequências de entrada, ambas em escalas logarítmicas. Portanto, é um ponto com coordenadas do tipo potência de saída e potência de entrada. O mais utilizado é o IP<sub>3</sub>. Quando traduzido em termos de amplitudes de tensões (supostas iguais entre os dois tons de entrada), o ponto de intersecção de enésima ordem é designado VIP<sub>n</sub> (CERDEIRA et al, 2004).

# 2.2.2 Distorção Harmônica Total com Sinais Senoidais nas Duas Entradas — THD<sub>2in</sub>

As análises realizadas pela figura de mérito clássica da THD consistem em aplicar um sinal senoidal em apenas uma das entradas do multiplicador, a outra sendo mantida constante, logo, avalia-se tão somente o nível de linearidade da resposta dos circuitos a uma das entradas separadamente. É razoável supor que para analisar o grau de distorção de um multiplicador analógico de forma mais confiável e segura, deva-se considerar variações nos dois sinais de entrada ao mesmo tempo (GONÇALVES, 2015) (LACERDA et al, 2009)

A equação que descreve a operação de um multiplicador ideal é:

$$z_{ideal} = K.x.y \tag{2.13}$$

onde  $z_{ideal}$  é o sinal de saída ideal, x e y são os sinais de entrada e K é a constante de multiplicação (ganho).

Na presença de não idealidades, o sinal de saída z de um multiplicador de duas entradas pode ser expandido em série de potências (LACERDA et al, 2009) (ANDRADE, 2011):

$$z = \sum_{m=1}^{m \to \infty} \left[ \frac{1}{m!} \sum_{r=0}^{m} {m \choose r} \frac{\partial^m z}{\partial x^r \partial y^{m-r}} x^r y^{m-r} \right]$$

(2.14)

Aplicando-se tons diferentes,  $f_1$  e  $f_2$ , nas duas entradas do multiplicador ideal, devem resultar na saída apenas duas componentes de frequências: uma na soma das frequências,  $f_1 + f_2$ , e outra na diferença entre as frequências,  $f_1 - f_2$ . Havendo distorção, outras combinações lineares desses dois tons devem aparecer na saída:  $a.f_1 + b.f_2$ , sendo a e b números inteiros, tais que se |a| = 1,  $|b| \neq 1$  e vice-versa, e de tal modo que cada combinação resulte em um número real não negativo (GONÇALVES, 2015).

O número de componentes de frequências  $a.f_1 + b.f_2$  que podem aparecer dentro da banda do multiplicador pode ser muito grande, tornando o processo de detecção por análise espectral difícil e fastidioso (LACERDA et al., 2009). Por exemplo, consideremos o caso em que o multiplicador tenha uma banda de passagem de 1 MHz e as frequências dos sinais de entrada sejam:  $f_1 = 2 \text{ kHz}$  e  $f_2 = 13 \text{ kHz}$ . Neste caso, o número de componentes presentes na banda do multiplicador pode chegar a 1000, sendo que nem todas apresentam potência significativa o bastante para serem discriminadas do ruído, mas não se pode saber *a priori* quantas e quais.

De acordo com (GONÇALVES 2015), a definição da distorção harmônica total considerando sinais senoidais nas duas entradas de um multiplicador analógico, então designada THD<sub>2in</sub>, é dada por:

$$THD_{2in} = \sqrt{\frac{\sum_{a}^{\pm \infty} \sum_{b}^{\pm \infty} A_{a,b}^{2}}{\frac{|ab| \neq 1|ab| \neq 1}{A_{1,1}^{2} + A_{-1,1}^{2}}}}$$

(2.15)

em que  $A_{a,b}$  é a amplitude da componente do sinal de saída na frequência  $a.f_1 + b.f_2$ , excluindo-se a frequência zero. Note-se que  $A_{1,1}$  e  $A_{-1,1}$  são as amplitudes das únicas componentes presentes na saída do multiplicador ideal.

#### 2.2.3 Métodos da Função Integral - IFM

#### 2.2.3.1 Função Não Linear Integral - INLF

Um critério mais recente para avaliação da linearidade é a INLF (CERDEIRA et al, 2001), (CERDEIRA et al, 2004), utilizada em vários trabalhos, seja para o caso de dispositivos ou de circuitos. Pelo fato de a INLF ser obtida diretamente das características DC dos elementos sob teste, este critério dispensa os procedimentos de análise espectral direta ou de análise temporal seguida da aplicação de análise de Fourier, ambos comprometidos pelas limitações em frequência dos instrumentos de medida e pela presença de ruído do sinal AC. Particularmente, a análise espectral ainda está sujeita à interferência humana, pois demanda a busca de todas as componentes de frequência de potência significativa na resposta AC do circuito, o que depende da percepção subjetiva na discriminação entre sinal e ruído.

A INLF é obtida a partir de integração da característica DC de um circuito e pode ser aplicada a dispositivos e a circuitos, tanto em modo de corrente como em modo tensão.

#### 2.2.3.2 Função Não Linear Integral em Duas Dimensões – 2D-INLF

O método da 2D-INLF, contribuição de (GONÇALVES, 2015)(LACERDA et al, 2009)(GONÇALVES et al, 2016)(GONÇALVES et al, 2019), é uma extensão do conceito da INLF para sistemas de duas entradas, que envolve a variação dos sinais nestas duas entradas simultaneamente, realizando uma avaliação mais abrangente das não linearidades do circuito (LACERDA et al, 2009). É definida particularmente para o caso de circuitos multiplicadores analógicos, embora possa ser definida para outros sistemas de duas entradas dos quais se conheça a função de transferência ideal.

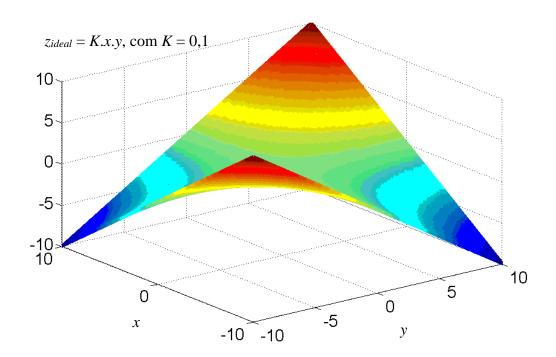

Diferentemente da INLF, na 2D-INLF, uma integral dupla é realizada ao longo de uma superfície, sendo que cada entrada é representada em um eixo do sistema de coordenadas. A superfície de transferência ideal no caso de multiplicadores é dada analiticamente por (2.13). Esta superfície tem a forma de um paraboloide hiperbólico, conforme a ilustração da Figura 2.19

A definição da função não-linear integral em duas dimensões (2D-INLF) para o caso de multiplicadores de um quadrante é, na forma normalizada:

$$2D-INFL = \frac{\int_0^{y_{max}} \int_0^{x_{max}} |z - K.x.y| dx dy}{\int_0^{y_{max}} \int_0^{x_{max}} K.x.y dx dy}$$

(2.16)

Em (2.16),  $x_{max}$  e  $y_{max}$  são os limites superiores dos sinais de entrada e z é o sinal de saída real do multiplicador (ANDRADE, 2011).

Figura 2.7– Representação da superfície característica de transferência de um multiplicador analógico ideal (paraboloide hiperbólico), para o caso de constante de multiplicação igual a 0,1.

Fonte: [GONÇALVES, 2015].

De acordo com (2.16), medições DC devem fornecer a superfície experimental em função dos sinais aplicados a ambas as entradas. Esta superfície experimental deve ser decrementada da superfície do paraboloide hiperbólico que representa a operação do

multiplicador ideal. O valor absoluto desta diferença é então duplamente integrado em relação aos valores dos sinais de entrada e normalizado em relação ao volume compreendido entre a superfície ideal e o plano *x-y*, gerando desta forma a 2D-INLF. (GONÇALVES, 2015, 2016)

A definição da 2D-INLF apresentada em (GONÇALVES, 2015, 2016) é ligeiramente diferente daquela apresentada em (LACERDA et al., 2009), na qual é determinado o valor absoluto do volume entre as superfícies experimental e ideal (integral dupla da diferença entre as superfícies). Este volume pode resultar positivo ou negativo, conforme a superfície experimental se situe acima ou abaixo da superfície ideal. Isto poderia gerar pontos de inflexão da função módulo, portanto, um comportamento visivelmente não monotônico da 2D-INLF. A estratégia aqui proposta de realizar a integração do valor absoluto da diferença entre as superfícies permite suavizar a variação da 2D-INLF com as amplitudes na entrada. Isto ocorre porque a integração atua como um filtro sobre as inflexões da função módulo.

Além disto, a definição em (2.16) pode ser facilmente estendida para multiplicadores de quatro quadrantes, sem necessidade de translação da origem do sistema como efetuado em (LACERDA et al., 2009), resultando em:

$$2D-INFL = \frac{\int_{y_{min}}^{y_{max}} \int_{x_{min}}^{x_{max}} |z - K.x.y| dx dy}{\int_{y_{min}}^{y_{max}} \int_{x_{min}}^{x_{max}} |K.x.y| dx dy},$$

(2.17)

onde  $x_{min}$  e  $y_{min}$  são os valores mínimos dos sinais de entrada, que podem ser negativos.

# 2.3 Expressões Teóricas das Figuras de Distorção em termos dos Coeficientes de Distorção