## UNIVERSIDADE FEDERAL DA BAHIA ESCOLA POLITÉCNICA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Lauê Rami Souza Costa de Jesus

# IMPLEMENTAÇÃO DE UM SISTEMA DE PROCESSAMENTO EM TEMPO REAL PARA A DETECÇÃO DE OBJETOS EM UMA CENA FIXA EM VÍDEOS DIGITAIS USANDO FPGA

DISSERTAÇÃO DE MESTRADO

Salvador Outubro de 2020

### Página em branco

#### Lauê Rami Souza Costa de Jesus

# IMPLEMENTAÇÃO DE UM SISTEMA DE PROCESSAMENTO EM TEMPO REAL PARA A DETECÇÃO DE OBJETOS EM UMA CENA FIXA EM VÍDEOS DIGITAIS USANDO FPGA

Dissertação de Mestrado apresentada ao Programa de Pós-graduação em Engenharia Elétrica, PPGEE, da Universidade Federal da Bahia, como parte dos requisitos necessários à obtenção do título de Mestre em Engenharia Elétrica.

Orientadores: Wagner L. A. de Oliveira Paulo C. M. de Abreu Farias

Salvador Outubro de 2020

Ficha catalográfica elaborada pelo Sistema Universitário de Bibliotecas (SIBI/UFBA), com os dados fornecidos pelo(a) autor(a).

Souza Costa de Jesus, Lauê Rami

Implementação de um Sistema de Processamento em Tempo Real para a Detecção de Objetos em uma Cena Fixa em Vídeos Digitais usando FPGA / Lauê Rami Souza Costa de Jesus. -- Salvador, 2021.

126 f. : il

Orientador: Wagner Luiz Alves de Oliveira. Coorientador: Paulo Cesar Machado de Abreu Farias. Dissertação (Mestrado - Programa de Pós-Graduação em Engenharia Elétrica) -- Universidade Federal da Bahia, Escola Politécnica, 2021.

1. Processamento Digital de Imagens. 2. Microeletrônica. 3. Visão Computacional. 4. Detecção de Objetos. 5. FPGA. I. Luiz Alves de Oliveira, Wagner. II. Machado de Abreu Farias, Paulo Cesar. III. Título.

#### Lauê Rami Souza Costa de Jesus

### Implementação de um Sistema de Processamento em Tempo Real para a Detecção de Objetos em uma Cena Fixa em Vídeos Digitais usando FPGA

Dissertação apresentada ao Programa de Pósgraduação em Engenharia Elétrica da Universidade Federal da Bahia como requisito parcial para obtenção do título de Mestre em Engenharia Elétrica.

Trabalho aprovado. Salvador, 27 de novembro de 2020:

**Professor Doutor**

Wagner Luiz Alves de Oliveira (Orientador)

**Professor Doutor**

Paulo César Machado de Abreu Farias (Coorientador)

Professor Doutor

Acbal Rucas Andrade Achy

Universidade Federal do Recôncavo da Bahia

**Professor Doutor**

Edson Pinto Santana Universidade Federal da Bahia

> Salvador novembro, 2020

### Agradecimentos

Agradeço, primeiramente, aos meus pais, pelo irrestrito esforço para me proporcionar uma educação de qualidade.

À minha esposa Ana Caroline Correia de Almeida.

Aos meus orientadores, Prof. Dr. Wagner L. Alves de Oliveira e Prof. Dr. Paulo Cesar.

Resumo da Dissertação apresentada à PPGEE/UFBA como parte dos requisitos

necessários para a obtenção do grau de Mestre em Engenharia Elétrica (M.Sc.)

IMPLEMENTAÇÃO DE UM SISTEMA DE PROCESSAMENTO EM TEMPO

REAL PARA A DETECÇÃO DE OBJETOS EM UMA CENA FIXA EM

VÍDEOS DIGITAIS USANDO FPGA

Lauê Rami Souza Costa de Jesus

Outubro/2020

Orientadores: Wagner L. A. de Oliveira

Paulo C. M. de Abreu Farias

Departamento: Engenharia Elétrica e de Computação

O processamento de vídeos e imagens digitais é uma área que possui muitas

aplicações que precisam de desempenho em tempo real, por exemplo, vigilância por

vídeo e segurança automotiva. Uma aplicação de processamento de imagens em

tempo real visa manipular, analisar e processar uma grande quantidade de dados

relacionados aos pixels de uma imagem em um tempo estipulado. Essas aplicações

incluem técnicas de processamento de imagens como análise, aprimoramento e seg-

mentação, bem como a detecção de objetos e outras. A extração das informações

de uma imagem é uma tarefa intensiva com alto custo computacional e através do

uso de um dispositivo FPGA é possível obter uma implementação mais adequada.

Este trabalho discute a implementação de um sistema de processamento em

tempo real para detecção de objetos em vídeos digitais usando FPGA. Todas as

etapas do fluxo de projeto do FPGA foram desenvolvidas. Nesta abordagem foram

incluídas as etapas de especificação do projeto, modelagem do sistema, microarqui-

tetura, codificação RTL, verificação funcional, síntese lógica, simulação em nível de

porta (lógica pós-síntese), análise de tempo e programação de dispositivos FPGA.

iii

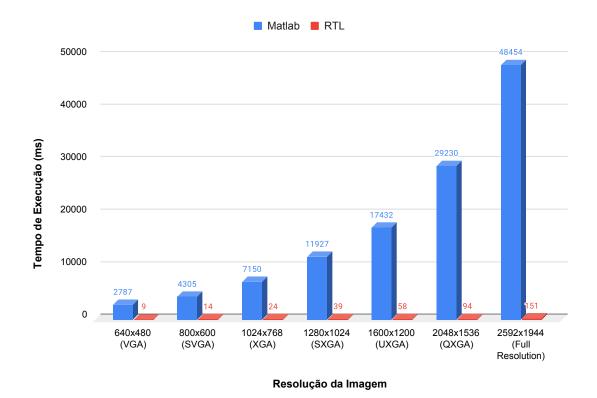

A arquitetura de hardware proposta foi projetada e sintetizada para o kit FPGA Altera DE2-115. Os resultados são verificados em tempo real com um vídeo de entrada advindo do sensor Terasic CMOS TRDB-D5M, do dispositivo FPGA DE2-115 e do monitor VGA para a exibição de imagens. A partir dos testes foram obtidos resultados com um *speedup* de 310x para a implementação do algoritmo de detecção de objetos em FPGA, quando comparada à implementação no software Matlab. Além disso, os resultados de síntese lógica mostraram que a arquitetura de hardware implementada teve uma baixa utilização dos recursos do FPGA, possibilitando que o sistema seja implementado em um dispositivo de baixo custo.

Abstract of Dissertation presented to PPGEE/UFBA as a partial fulfillment of the

requirements for the degree of Master of Science (M.Sc.)

IMPLEMENTATION OF A REAL-TIME PROCESSING SYSTEM FOR

OBJECT DETECTION IN A FIXED SCENE IN DIGITAL VIDEOS USING

**FPGA**

Lauê Rami Souza Costa de Jesus

October/2020

Advisors: Wagner L. A. de Oliveira

Paulo C. M. de Abreu Farias

Department: Electrical and Computer Engineering

Digital video and image processing is an area that finds many applications that

need real-time performance, for example, Video Surveillance and Automotive Safety.

A real-time image processing application aims to manipulate, analyze and process a

large amount of data related to the pixels of an image in a stipulated time. These ap-

plications includes image processing techniques like image analysis, image enhance-

ment, image segmentation, object detection and others. Extracting the resources of

an image is an intensive task with high computational cost and through the use of

an FPGA device it is possible to achieve a more suitable implementation.

This work discusses the implementation of a Real-Time Processing System for

Object Detection in Digital Videos using FPGA. All the steps of the FPGA design

flow were developed. In this approach the steps of project specification, system

modeling, microarchitecture, RTL coding, functional verification, logic synthesis,

gate level simulation (logic post-synthesis), time analysis and FPGA device pro-

gramming were included.

The proposed hardware architecture was designed and synthesized for Altera

DE2-115 FPGA kit. The results are verified in real time with an input video from

v

TRDB-D5M Terasic CMOS sensor, DE2-115 FPGA kit and VGA monitor for displaying images. The tests results were obtained with a 310x speedup for the object detection algorithm implementation in FPGA, when compared to the Matlab implementation. In addition, the logic synthesis results have shown that the hardware architecture implemented had a low FPGA resources utilization, enabling the system to be developed in a low cost device.

### Sumário

| Li | ista c               | le Figu | ras                                                |  | X  |

|----|----------------------|---------|----------------------------------------------------|--|----|

| Li | Lista de Tabelas xiv |         |                                                    |  |    |

| 1  | Inti                 | odução  | 0                                                  |  | 1  |

|    | 1.1                  | Objeti  | vos                                                |  | 2  |

|    | 1.2                  | Organ   | ização da Dissertação                              |  | 3  |

|    | 1.3                  | Result  | ados em Publicações                                |  | 4  |

| 2  | Pro                  | cessan  | nento Digital de Imagens e Vídeos                  |  | 5  |

|    | 2.1                  | Etapas  | s Fundamentais no Processamento Digital de Imagens |  | 5  |

|    | 2.2                  | Image   | m                                                  |  | 6  |

|    |                      | 2.2.1   | Amostragem e Quantização da Imagem                 |  | 7  |

|    |                      | 2.2.2   | Representação de Imagens Digitais                  |  | 9  |

|    |                      | 2.2.3   | Vizinhança de um <i>Pixel</i>                      |  | 9  |

|    |                      | 2.2.4   | Operações Orientadas a Vizinhança                  |  | 10 |

|    |                      | 2.2.5   | Tipos de Processamento Digital de Imagens          |  | 11 |

|    |                      | 2.2.6   | Segmentação de Imagem                              |  | 12 |

|    |                      | 2.2.7   | Detecção de Descontinuidade                        |  | 12 |

|    |                      | 2.2.8   | Detecção de Linha                                  |  | 13 |

|    |                      | 2.2.9   | Detecção de Borda                                  |  | 13 |

|    |                      | 2.2.10  | Thresholding                                       |  | 15 |

|    |                      | 2.2.11  | Resolução de Imagem                                |  | 16 |

|    |                      | 2.2.12  | Tipos de Imagens Digitais                          |  | 16 |

|    |                      | 2.2.13  | Tamanho dos Dados de uma Imagem                    |  | 18 |

|    | 2.3                  | Vídeo   |                                                    |  | 19 |

|   |     | 2.3.1   | $Scanning \dots \dots$ | 20 |

|---|-----|---------|------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | 2.3.2   | Sinais de Temporização do Fluxo de Vídeo                                                                                     | 20 |

|   | 2.4 | Proces  | ssamento de Imagens em Tempo Real                                                                                            | 21 |

|   | 2.5 | Métod   | los para a Detecção de Objetos                                                                                               | 22 |

|   | 2.6 | Traba   | lhos Correlatos                                                                                                              | 24 |

| 3 | Me  | todolog | gia do Projeto de Circuitos Integrados Digitais                                                                              | 27 |

|   | 3.1 | Arquit  | tetura de Hardware Reconfigurável                                                                                            | 28 |

|   | 3.2 | Fluxo   | de Projeto em FPGA                                                                                                           | 29 |

|   |     | 3.2.1   | Especificação do Sistema                                                                                                     | 31 |

|   |     | 3.2.2   | Modelagem do Algoritmo de Processamento de Imagem                                                                            | 34 |

|   |     | 3.2.3   | Microarquitetura                                                                                                             | 35 |

|   |     | 3.2.4   | Codificação RTL                                                                                                              | 35 |

|   |     | 3.2.5   | Verificação Funcional                                                                                                        | 39 |

|   |     | 3.2.6   | Síntese Lógica, Síntese Física, Simulação em Nível de Portas                                                                 |    |

|   |     |         | e Geração do <i>Bitstream</i>                                                                                                | 42 |

| 4 | Des | crição  | do Sistema de Detecção de Objetos em uma Cena Fixa                                                                           | l  |

|   | em  | Vídeos  | s Digitais                                                                                                                   | 45 |

|   | 4.1 | Proces  | sso de Aquisição de Imagens                                                                                                  | 45 |

|   | 4.2 | Descri  | ção do Algoritmo de Detecção de Objetos em uma Cena Fixa  .                                                                  | 47 |

|   | 4.3 | Desen   | volvimento do Algoritmo de Detecção de Bordas                                                                                | 52 |

|   | 4.4 | Projet  | o da Arquitetura do Algoritmo de Comparação entre Quadros                                                                    |    |

|   |     | de Ima  | agens Digitais                                                                                                               | 56 |

| 5 | Arc | luitetu | ra de Hardware Desenvolvida                                                                                                  | 59 |

|   | 5.1 | Visão   | Geral da Arquitetura do Sistema                                                                                              | 59 |

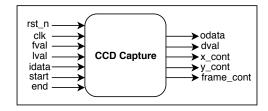

|   |     | 5.1.1   | CCD Capture                                                                                                                  | 61 |

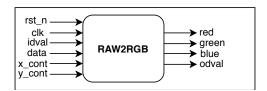

|   |     | 5.1.2   | RAW2RGB                                                                                                                      | 62 |

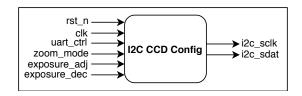

|   |     | 5.1.3   | I2C CCD Config                                                                                                               | 62 |

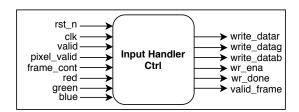

|   |     | 5.1.4   | Input Handler Ctrl                                                                                                           | 63 |

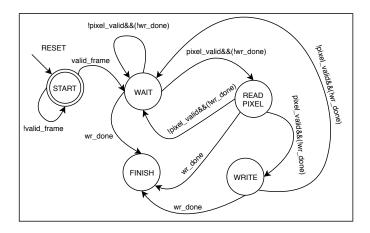

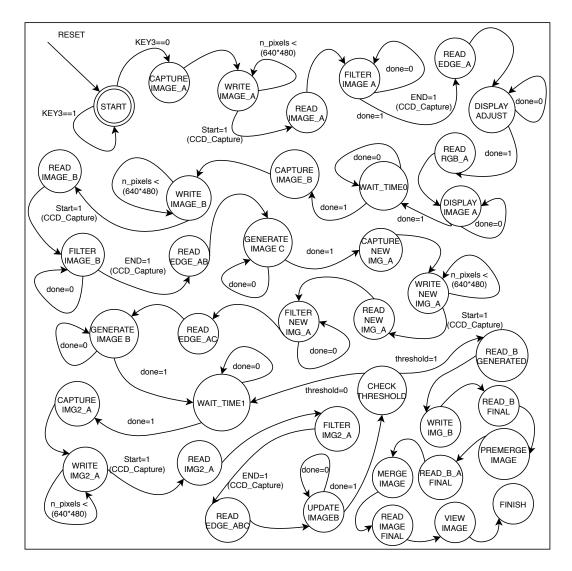

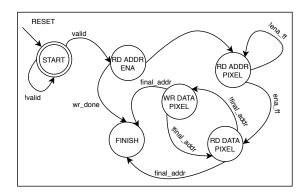

|   |     | 5.1.5   | FSM Control                                                                                                                  | 64 |

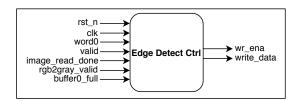

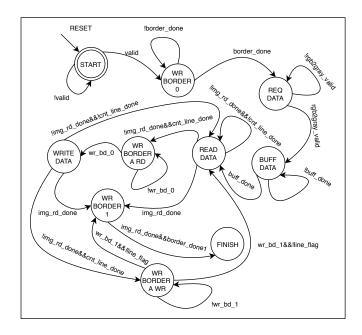

|   |     | 5.1.6   | EDGE DETECT CTRL                                                                                                             | 71 |

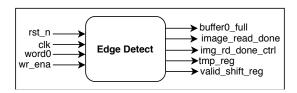

|   |     | 5.1.7   | EDGE DETECT                                                                                                                  | 73 |

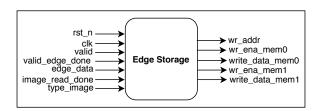

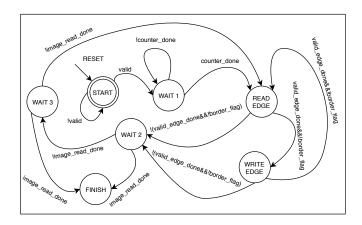

|              |                                                              | 5.1.8 EDGE STORAGE                                                 | 74  |

|--------------|--------------------------------------------------------------|--------------------------------------------------------------------|-----|

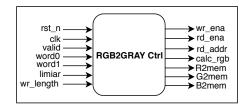

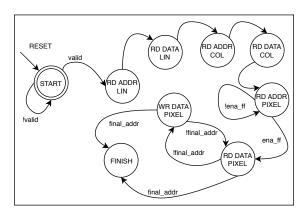

|              |                                                              | 5.1.9 RGB2GRAY CTRL                                                | 75  |

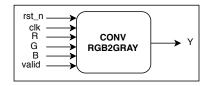

|              |                                                              | 5.1.10 CONV RGB2GRAY                                               | 76  |

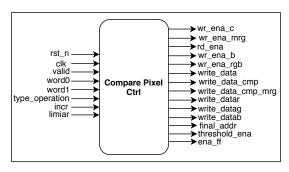

|              |                                                              | 5.1.11 COMPARE PIXEL CTRL                                          | 76  |

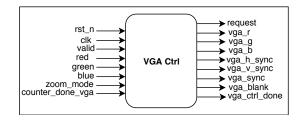

|              |                                                              | 5.1.12 VGA CTRL                                                    | 77  |

|              |                                                              | 5.1.13 Organização da Memória                                      | 77  |

| 6            | Am                                                           | biente de Verificação Funcional Desenvolvido                       | 81  |

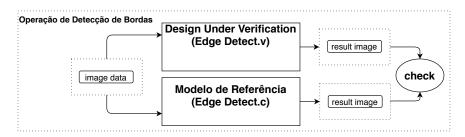

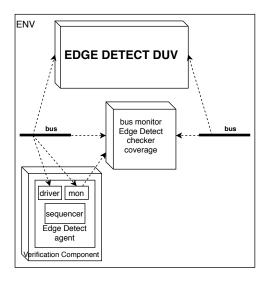

|              | 6.1                                                          | Ambiente de Verificação do EDGE DETECT                             | 81  |

|              | 6.2                                                          | Ambiente de Verificação do Compare Pixel CTRL                      | 83  |

|              | 6.3                                                          | Ambiente de Verificação do CONV RGB2GRAY                           | 83  |

|              | 6.4                                                          | Ambientes de Verificação dos Módulos de Controle de Leitura / Es-  |     |

|              |                                                              | crita na Memória                                                   | 84  |

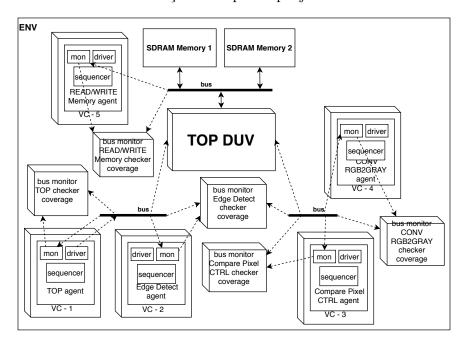

|              | 6.5                                                          | Ambiente de Verificação do Topo do Projeto                         | 86  |

|              | 6.6                                                          | Assertions                                                         | 86  |

| 7            | Res                                                          | ultados                                                            | 88  |

|              | 7.1                                                          | Restrições de Tempo Real                                           | 89  |

|              |                                                              | 7.1.1Resultados da Cobertura Funcional e Cobertura de Código $.$ . | 90  |

|              | 7.2                                                          | Resultados da Simulação Funcional                                  | 91  |

|              | 7.3                                                          | Resultados da Síntese Lógica                                       | 94  |

|              | 7.4                                                          | Resultados de Desempenho                                           | 95  |

|              | 7.5                                                          | Resultados da Prototipação em FPGA                                 | 96  |

| 8            | Cor                                                          | nclusões                                                           | 99  |

| Re           | eferê                                                        | ncias Bibliográficas                                               | 101 |

| $\mathbf{A}$ | Artigo apresentado no Workshop on Circuits and System Design |                                                                    |     |

|              | - W                                                          | CAS 2019                                                           | 105 |

### Lista de Figuras

| 2.1  | Etapas fundamentais no processamento digital de imagens [10] | 5  |

|------|--------------------------------------------------------------|----|

| 2.2  | Coordenadas, convenção e imagem [11]                         | 7  |

| 2.3  | Amostragem [12]                                              | 8  |

| 2.4  | Função de mapeamento para quantização uniforme [11]          | 8  |

| 2.5  | Pixel dentro de uma vizinhança [11]                          | 10 |

| 2.6  | Máscara de convolução $3x3$                                  | 11 |

| 2.7  | Processamento de vizinhança para o caso de filtragem linear  | 11 |

| 2.8  | Tipos de processamento digital de imagens [14]               | 12 |

| 2.9  | Detecção de borda                                            | 14 |

| 2.10 | Histograma [10]                                              | 16 |

| 2.11 | Imagem binária [15]                                          | 17 |

| 2.12 | Imagem em escala de cinza [15]                               | 17 |

| 2.13 | Imagem no formato RGB [15]                                   | 18 |

| 2.14 | Sequência de vídeo digital [12]                              | 19 |

| 2.15 | Sinais de temporização do fluxo de vídeo [12]                | 21 |

| 2.16 | Métodos para a detecção de objetos                           | 22 |

| 2.17 | Conceito geral do método Background Subtraction              | 23 |

| 2.18 | Conceito geral do método frame differencing                  | 23 |

| 3.1  | Bloco lógico configurável FPGA [28]                          | 28 |

| 3.2  | Estrutura conceitual de um dispositivo FPGA                  | 29 |

| 3.3  | Fluxo de projeto de hardware digital                         | 32 |

| 3.4  | Visão geral do sistema proposto                              | 32 |

| 3.5  | Fluxo da modelagem do algoritmo de processamento de imagens  | 35 |

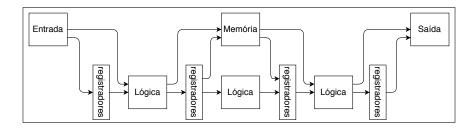

| 3.6  | Estrutura de um circuito lógico digital                      | 38 |

| 3.7  | Estrutura básica de uma máquina de estados finita [37] 39                              |    |  |  |

|------|----------------------------------------------------------------------------------------|----|--|--|

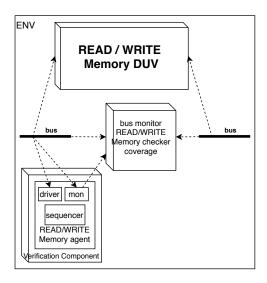

| 3.8  | Estrutura do ambiente de verificação                                                   |    |  |  |

| 4.1  | Câmera TRDB-D5M terasic sensor CMOS                                                    | 45 |  |  |

| 4.2  | Estrutura de matriz de pixels e o bayer pattern                                        | 46 |  |  |

| 4.3  | Interface padrão do sensor CMOS                                                        | 46 |  |  |

| 4.4  | Processo de aquisição de imagens                                                       | 47 |  |  |

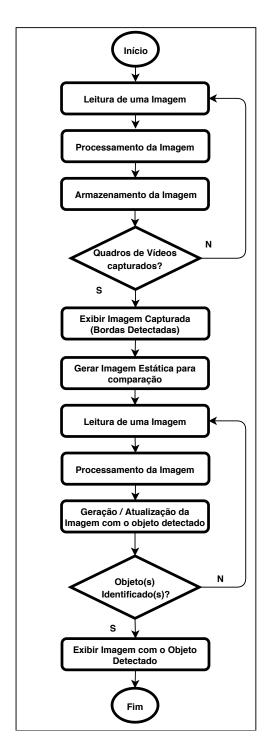

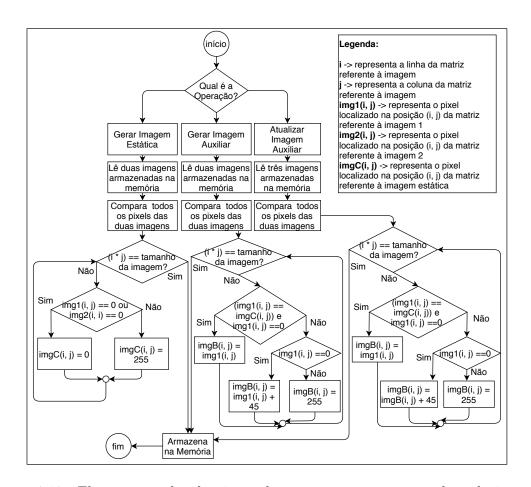

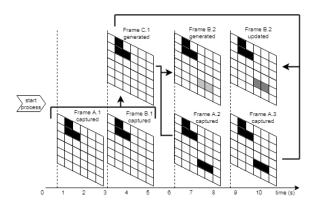

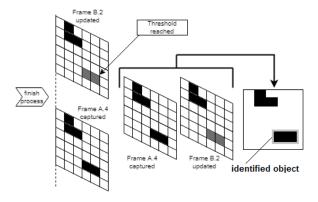

| 4.5  | Processo de detecção de objetos em uma cena fixa                                       | 48 |  |  |

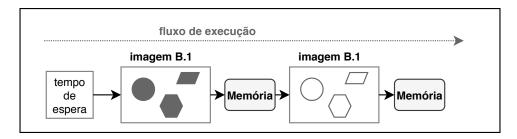

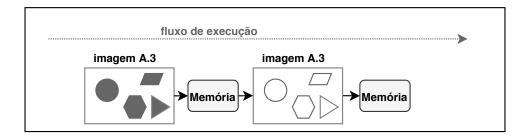

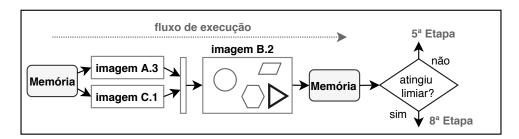

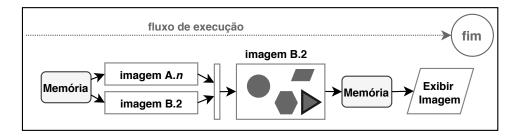

| 4.6  | 1ª etapa do fluxo do algoritmo de detecção de objetos                                  | 49 |  |  |

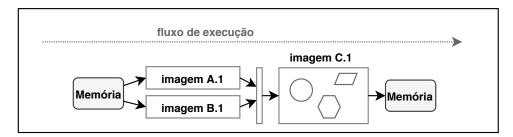

| 4.7  | $2^a$ etapa do fluxo do algoritmo de detecção de objetos. $\ \ldots \ \ldots \ \ldots$ | 49 |  |  |

| 4.8  | 3ª etapa do fluxo do algoritmo de detecção de objetos                                  | 49 |  |  |

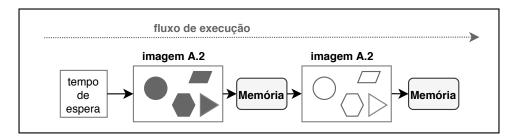

| 4.9  | 4ª etapa do fluxo do algoritmo de detecção de objetos                                  | 50 |  |  |

| 4.10 | $5^{\rm a}$ etapa do fluxo do algoritmo de detecção de objetos                         | 50 |  |  |

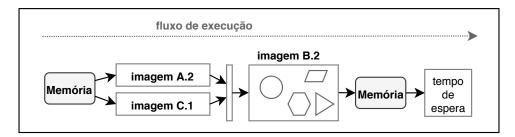

| 4.11 | 6ª etapa do fluxo do algoritmo de detecção de objetos                                  | 51 |  |  |

| 4.12 | 7ª etapa do fluxo do algoritmo de detecção de objetos                                  | 51 |  |  |

| 4.13 | $8^a$ etapa do fluxo do algoritmo de detecção de objetos                               | 52 |  |  |

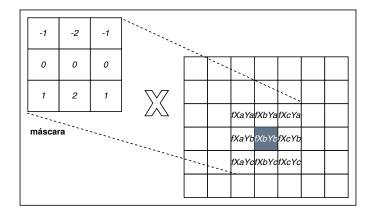

| 4.14 | Convolução de uma máscara com uma imagem                                               |    |  |  |

| 4.15 | Resultado da aplicação dos operadores de Roberts, Prewitt e Sobel à                    |    |  |  |

|      | uma imagem.                                                                            | 53 |  |  |

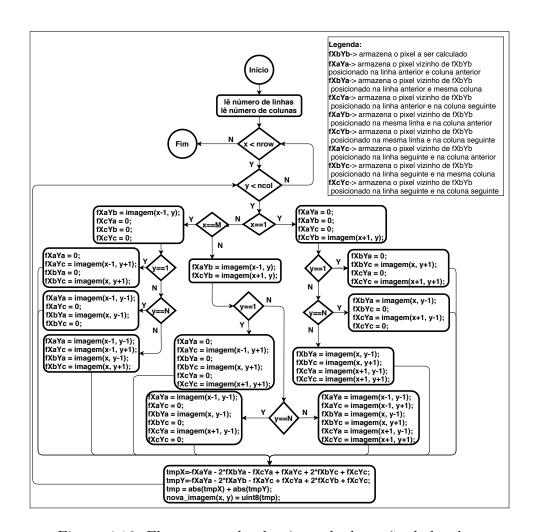

| 4.16 | Fluxograma do algoritmo de detecção de bordas                                          | 55 |  |  |

| 4.17 | Variáveis que armazenam o pixel a ser calculado e seus vizinhos                        | 55 |  |  |

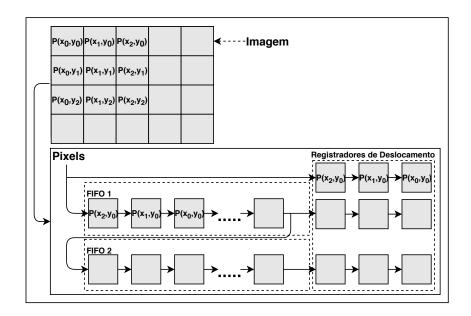

| 4.18 | Arquitetura de hardware para o algoritmo de detecção de borda                          | 56 |  |  |

| 4.19 | Fluxograma do algoritmo de comparação entre quadros de imagens                         |    |  |  |

|      | digitais.                                                                              | 58 |  |  |

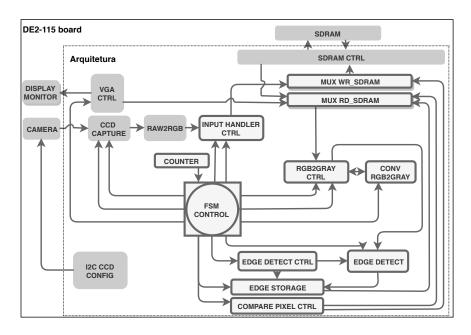

| 5.1  | Arquitetura de hardware                                                                | 60 |  |  |

| 5.2  | Módulo CCD capture                                                                     | 61 |  |  |

| 5.3  | Módulo RAW2RGB                                                                         | 62 |  |  |

| 5.4  | Módulo I2C CCD config                                                                  | 63 |  |  |

| 5.5  | Módulo input handler ctrl                                                              | 63 |  |  |

| 5.6  | FSM - input handler ctrl                                                               |    |  |  |

| 5.7  | FSM - control                                                                          | 71 |  |  |

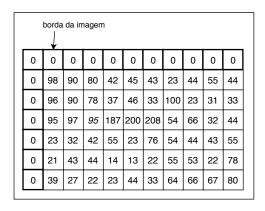

| 5.8  | Adição das bordas da imagem                                                            | 72 |  |  |

| 5.9  | Módulo edge detect ctrl                                               | 72 |

|------|-----------------------------------------------------------------------|----|

| 5.10 | FSM - edge detect ctrl                                                | 73 |

| 5.11 | Módulo edge detect.                                                   | 73 |

| 5.12 | Módulo edge storage                                                   | 74 |

| 5.13 | FSM - edge storage                                                    | 74 |

| 5.14 | Módulo RGB2GRAY ctrl                                                  | 75 |

| 5.15 | FSM - RGB2GRAY ctrl                                                   | 75 |

| 5.16 | Módulo CONV RGB2GRAY                                                  | 76 |

| 5.17 | Módulo compare pixel ctrl                                             | 76 |

| 5.18 | FSM - compare pixel ctrl                                              | 77 |

| 5.19 | Módulo VGA ctrl                                                       | 77 |

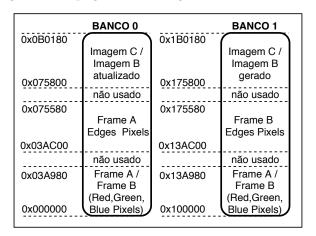

| 5.20 | Organização da memória                                                | 78 |

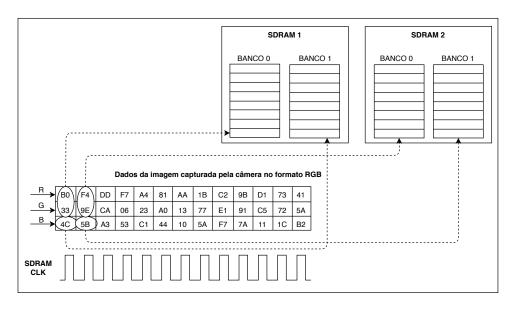

| 5.21 | Armazenamento dos dados do quadro de imagem no formato RGB            |    |

|      | na memória                                                            | 79 |

| 6.1  | Modelo de referência do ambiente de verificação do edge detect        | 82 |

| 6.2  | Ambiente de verificação do edge detect                                | 82 |

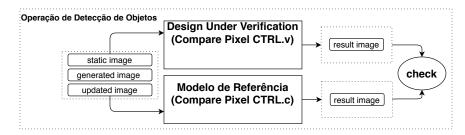

| 6.3  | Modelo de referência do ambiente de verificação do compare pixel ctrl | 83 |

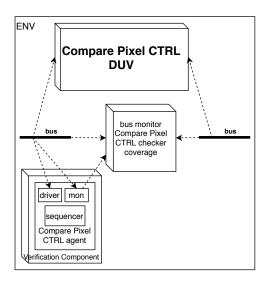

| 6.4  | Ambiente de verificação do compare pixel ctrl                         | 84 |

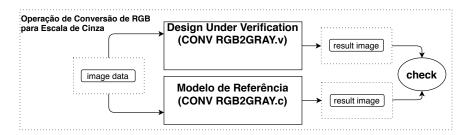

| 6.5  | Modelo de referência do ambiente de verificação do CONV RGB2GRAY      | 84 |

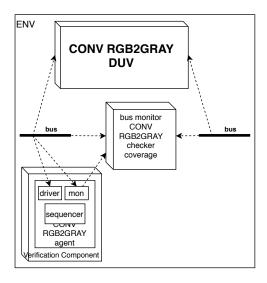

| 6.6  | Ambiente de verificação do CONV RGB2GRAY                              | 85 |

| 6.7  | Ambiente de verificação dos módulos de controle de leitura / escrita  |    |

|      | na memória                                                            | 85 |

| 6.8  | Ambiente de verificação do topo do projeto                            | 86 |

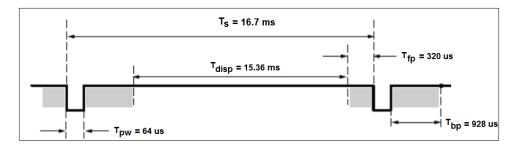

| 7.1  | Tempo de controle VGA com atualização de 60 Hz e $pixel\ clock$ de    |    |

|      | 25 MHz                                                                | 89 |

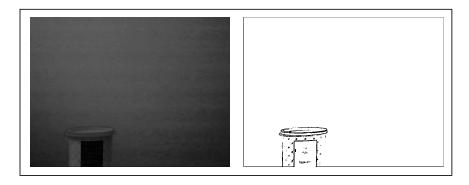

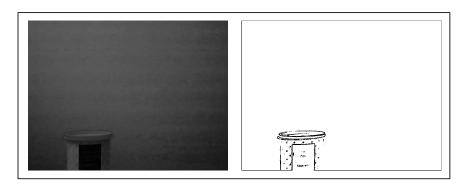

| 7.2  | $1^{\circ}$ quadro de imagem de vídeo capturado                       | 92 |

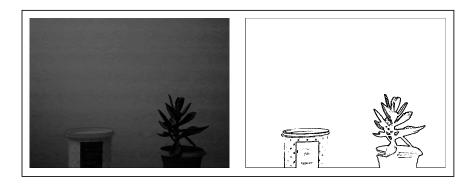

| 7.3  | $2^{\circ}$ quadro de imagem de vídeo capturado                       | 93 |

| 7.4  | $3^\circ$ quadro de imagem de vídeo capturado                         | 93 |

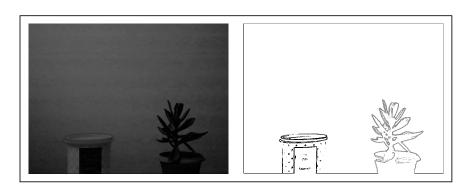

| 7.5  | $7^{\circ}$ quadro de imagem de vídeo capturado                       | 93 |

| 7.6  | Resultado da detecção do objeto em uma cena fixa                      | 94 |

| 77   | Resultados de desempenho                                              | 96 |

| 7.8  | $1^\circ$ quadro de imagem de vídeo capturado (FPGA)    | 96 |

|------|---------------------------------------------------------|----|

| 7.9  | $3^\circ$ quadro de imagem de vídeo capturado (FPGA)    | 97 |

| 7.10 | Resultado da detecção do objeto em uma cena fixa (FPGA) | 98 |

### Lista de Tabelas

| 2.1 | Padrões de resoluções de vídeo    | 16 |

|-----|-----------------------------------|----|

| 7.1 | Resultados da cobertura funcional | 90 |

| 7.2 | Resultados da cobertura de código | 91 |

| 7.3 | Resultado da síntese para FPGA    | 94 |

Dedico esse trabalho a minha esposa Ana Caroline Correia de Almeida de Jesus e aos meus pais, Nagilson Costa de Jesus e Maria Zenaide de Souza

### Capítulo 1

### Introdução

A detecção de objetos é o ato de encontrar um objeto em uma imagem. Hoje, os algoritmos de detecção de objetos são usados em aplicações como a vigilância por vídeo [1] e segurança, rastreamento de objetos, reconhecimento facial [2], inspeção industrial [3], processamento e análise de imagens médicas [4], carros autodirigidos e outros.

As estratégias de visão computacional para detecção de objetos são comumente desenvolvidas em software. Existem diferentes trabalhos como o de [5], [6] e [7] que estudam a implementação de diversos algoritmos de detecção de objetos em software. Nestes trabalhos os algoritmos de processamento de imagem são implementados em Matlab ou OpenCV, no entanto poderiam ser otimizados em termos de desempenho e consumo de potência utilizando outras abordagens para implementação. Muitas técnicas de detecção de objetos usam operadores de detecção de bordas como uma etapa do processamento de dados de imagem. Os métodos de detecção de bordas consistem em análise de imagem e extração de informações estruturais. Essa informação extraída referente à borda reduz a quantidade de dados a ser processada. No entanto, o processo de detecção de bordas é computacionalmente exaustivo, pois para cada pixel operado pelo detector de borda, cerca de 20 operações lógicas e aritméticas são executadas. Além disso, para a realização dessas operações, devem ser consideradas as sobrecargas de armazenamento e recuperação de dados dos pixels da imagem. Portanto, a restrição de tempo é o maior desafio neste tipo de aplicação.

O FPGA é uma plataforma reconfigurável, que fornece grandes matrizes de recursos lógicos programáveis. O FPGA também oferece o paralelismo temporal e

espacial, e essa característica torna o FPGA adequado para a implementação de algoritmos de processamento de imagem em tempo real. O aumento na capacidade de dispositivos FPGA, com relação a recursos e desempenho, tem resultado em projetos muito mais complexos, levando ao desenvolvimento de aplicações utilizando o fluxo de projeto em FPGA. De acordo com [8], a utilização de arquiteturas de hardware reconfigurável tem crescido entre os projetistas de diferentes áreas como robótica, telecomunicações, processamento digital de sinais e imagens, equipamentos médicos e automotiva, bem como na área de projetos de circuitos integrados. Segundo [9], foram obtidos avanços com a utilização de dispositivos FPGA para a aceleração da computação de alto desempenho.

O uso de dispositivos FPGA está aumentando à medida que fornecem um baixo tempo de colocação no mercado e custo mínimo de desenvolvimento de hardware, recursos muito procurados pela rápida mudança tecnologias. Além disso, o processo de verificação funcional contido no fluxo de projeto em FPGA permite maior robustez ao projeto, além de diminuir o tempo gasto para encontrar falhas. No entanto, essa melhora na produtividade do projeto somente será alcançada com a aplicação de uma metodologia de projeto adequada.

### 1.1 Objetivos

O principal objetivo deste trabalho é desenvolver uma arquitetura de hardware, para a detecção de objetos em tempo real, e prototipar a solução desenvolvida em FPGA.

Para isso, foram utilizados conceitos e técnicas de processamento de imagens, como segmentação e detecção de bordas. O desenvolvimento dessa solução levou em consideração a aplicação do fluxo de projeto de hardware digital, desde a especificação do sistema até a geração do bitstream, para a prototipação em FPGA.

Como objetivos específicos desse projeto, cita-se:

- Estudar conceitos e técnicas de processamento digital de imagens relacionados à segmentação e detecção de bordas.

- 2. Compreender o fluxo de projeto de hardware digital para utilização como metodologia de implementação.

- Especificar o sistema de detecção de objetos em uma cena fixa em vídeos digitais.

- 4. Modelar o sistema de detecção de objetos em uma cena fixa em vídeos digitais em uma linguagem de alto nível.

- Descrever o hardware de forma a atender os requisitos da especificação funcional.

- Desenvolver a verificação funcional visando garantir o funcionamento do hardware.

### 1.2 Organização da Dissertação

No Capítulo 2, são apresentados os conceitos e técnicas relacionadas ao processamento digital de imagens e vídeos. Estes são conceitos fundamentais para o entendimento da aplicação desse projeto.

O Capítulo 3, apresenta a metodologia de desenvolvimento deste projeto, descrevendo todas as etapas do fluxo de projeto de hardware digital (especificação e modelagem do sistema, microarquitetura, codificação RTL, verificação funcional, síntese lógica, síntese física, simulação em nível de portas e geração do bitstream. As principais técnicas e ferramentas utilizadas em cada estágio serão detalhadas neste capítulo.

No Capítulo 4, são apresentados os projetos de arquitetura dos principais algoritmos desenvolvidos e utilizados neste trabalho. O fluxo de execução do algoritmo, análise de outras soluções e as técnicas de implementação, que proporcionaram a elaboração dos algoritmos de detecção de bordas e de objetos, também são discutidos.

No Capítulo 5, são apresentados a arquitetura de hardware desenvolvida, a descrição da funcionalidade, diagramas e a lógica de controle de cada bloco implementado em código RTL. No Capítulo 7 é realizada uma análise sobre a restrição de tempo real empregada no projeto, além da discussão de resultados da simulação funcional, síntese lógica, desempenho e prototipação em FPGA, relativos ao sistema de detecção de objetos em uma cena fixa. Os resultados da verificação funcional,

bem como da cobertura funcional também são reportados.

No Capítulo 8 são apresentadas as conclusões deste trabalho. Por fim, no apêndice A encontra-se o texto completo do artigo publicado e apresentado no WCAS 2019.

### 1.3 Resultados em Publicações

A partir do desenvolvimento, implementação e prototipação em FPGA da arquitetura de hardware, para a detecção de objetos em tempo real, foram obtidos resultados que foram apresentados e publicados no Workshop on Circuits and System Design (WCAS 2019), no evento internacional de microeletrônica Chip-in-Sampa 2019, sediado no Brasil.

Abstract: This paper discusses the implementation of a Real-Time Processing System for Object Detection in Digital Videos. The system consists of real-time image processing and this application is suitable for implementation in FPGA due to the algorithm features and the device resources. The proposed hardware architecture was designed and synthesized for Intel DE2-115 FPGA. The main concepts, techniques, the methodology used for development the design will be presented. The results are verified in real time with an input video from TRDB-D5M Terasic CMOS sensor, DE2-115 FPGA device and VGA monitor for displaying images.

JESUS, L. R. S. C., OLIVEIRA, W. L. A., FARIAS, P. C. M. A. Implementation of a Real-Time Processing System for Object Detection in Digital Videos using FPGA. Workshop on Circuits and System Design (WCAS 2019), São Paulo, Brazil. O Artigo completo publicado no WCAS 2019 está anexado à dissertação.

### Capítulo 2

### Processamento Digital de Imagens e Vídeos

## 2.1 Etapas Fundamentais no Processamento Digital de Imagens

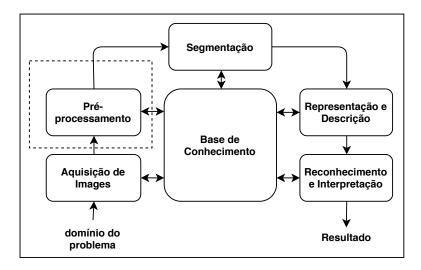

Como pode ser visualizado na Figura 2.1, as etapas fundamentais no Processamento Digital de Imagens são organizadas da seguinte forma [10]:

Figura 2.1: Etapas fundamentais no processamento digital de imagens [10].

Aquisição de Imagens. Um dispositivo físico, sensível a uma banda do espectro eletromagnético, produzirá um sinal elétrico como saída proporcional ao nível de energia percebida. Em seguida, um digitalizador realizará a conversão da saída elétrica do dispositivo físico para a forma digital.

- Pré-processamento. Este processamento pode incluir etapas distintas como, por exemplo: Melhoria da Imagem, Restauração da Imagem, Processamento de Imagem Colorida, Wavelets e processamento multi-resolução, Compressão e Processamento Morfológico. Em resumo, técnicas de processamento de imagens são aplicadas visando a melhoria da imagem, para extração de informações.

- Segmentação. Os procedimentos de segmentação dividem uma imagem em seus componentes ou objetos. A segmentação é uma das etapas mais complexas no processamento de imagens digital. Quanto melhor for o algoritmo de segmentação, maior a chance de sucesso no reconhecimento da imagem.

- Representação e Descrição. A escolha de uma representação é apenas parte da solução, para transformar dados brutos em uma forma adequada para o processamento subsequente do computador. Um método deve ser especificado para descrever os dados, de modo que os recursos de interesse sejam destacados.

- Reconhecimento de Objetos. O reconhecimento é o processo que atribui um rótulo a um objeto com base nos seus descritores.

### 2.2 Imagem

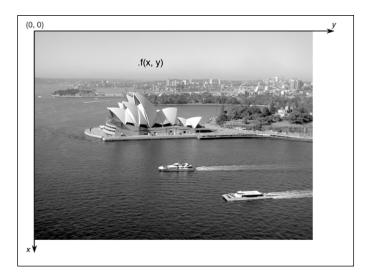

Segundo [10], uma imagem pode ser definida como uma função bidimensional, f(x,y), onde x e y são coordenadas espaciais (planas), e a amplitude de f em qualquer par de coordenadas (x,y), é chamada intensidade ou nível de cinza da imagem nesse ponto. Quando x, y, e os valores de amplitude de f são todos finitos e quantidades discretas, tem-se uma imagem digital.

O campo de processamento de imagem digital refere-se ao processamento de imagens por meio de um computador. Uma imagem digital é composta por um número finito de elementos, cada um dos quais com uma localização particular e valor. Estes elementos são referidos como elementos de imagem. *Pixel* é o termo mais utilizado para denotar os elementos de uma imagem digital [10].

A convenção do eixo usada para representar a imagem é mostrada na Figura 2.2. A origem está localizada no canto superior esquerdo. A linha horizontal e a linha vertical na origem são definidas como eixos y e x, respectivamente.

Figura 2.2: Coordenadas, convenção e imagem [11].

### 2.2.1 Amostragem e Quantização da Imagem

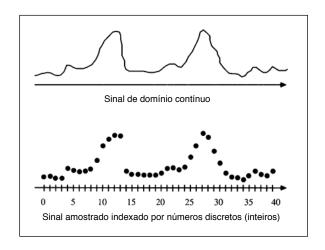

Para criar uma imagem digital, é preciso converter os dados sensíveis contínuos em formato digital, o que envolve dois processos que são chamados de Amostragem e Quantização [10].

Uma imagem pode ser contínua em relação às coordenadas x e y, bem como em amplitude. Para convertê-la em forma digital, tem-se que amostrar a função em ambas as coordenadas e amplitude. A discretização dos valores das coordenadas é chamada de amostragem. A discretização dos valores das amplitudes é chamada de quantização.

Amostragem é o processo de conversão de um espaço contínuo (ou sinal de espaço/tempo contínuo) em um sinal de espaço discreto (ou espaço/tempo discreto). Ao adquirir a imagem a função contínua é amostrada e sua amplitude quantizada, a Figura 2.3 ilustra o resultado da amostragem de um sinal unidimensional de domínio contínuo.

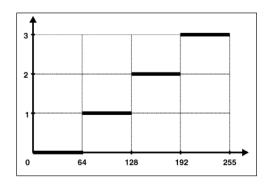

A quantização pode ser definida como a aproximação do valor obtido pelo processo de amostragem, para o nível mais próximo dentre um número finito de níveis de quantização.

Figura 2.3: Amostragem [12].

No caso de imagens monocromáticas, a função é f(x,y) e os níveis de quantização são também conhecidos como níveis de cinza. É comum adotar N níveis de quantização para digitalização de imagens, onde N é geralmente uma potência de 2, ou seja,  $N=2^n$ , sendo n o número de bits necessários para codificar cada valor de pixel.

A quantização de imagens pode ser descrita como um processo de mapeamento pelo qual grupos de pontos de dados (vários *pixels* dentro de uma faixa de valores cinza) são mapeados para um único ponto (ou seja, um único nível de cinza). Este processo pode ser visualizado na Figura 2.4. Neste caso, os valores no intervalo de 0 a 255 são representados por apenas 4 níveis de quantização.

Figura 2.4: Função de mapeamento para quantização uniforme [11].

#### 2.2.2 Representação de Imagens Digitais

Assumindo que uma imagem f(x, y) é amostrada, tem-se que o resultado da imagem digital possui M linhas e N colunas.

$$f(x,y) = \begin{bmatrix} f(0,0) & f(0,1) & \dots & f(0,N-1) \\ f(1,0) & f(1,1) & \dots & f(1,N-1) \\ \vdots & \vdots & & \vdots \\ f(M-1,0) & f(M-1,1) & \dots & f(M-1,N-1) \end{bmatrix}$$

(2.1)

O lado direito da equação 2.1 é por definição uma imagem digital. Cada elemento desta matriz é chamado de elemento de imagem ou *pixel*.

Seja Z e R o conjunto de números inteiros e o conjunto de números reais, respectivamente. O processo de amostragem pode ser visto como um particionamento do plano xy em uma grade, com as coordenadas do centro de cada grade sendo um par de elementos do produto cartesiano  $Z^2$ , que é o conjunto de todos os pares ordenados de elementos  $(z_i, z_j)$ , com  $z_i$  e  $z_j$  sendo inteiros de Z.

Portanto, f(x,y) é uma imagem digital se (x,y) são inteiros de  $Z^2$ , e f é uma função que atribui um valor de intensidade (ou seja, um número que pertence ao conjunto de números reais R) para cada par distinto de coordenadas (x,y) [10]. Se os níveis de cinza também são números inteiros, Z substitui R e uma imagem digital torna-se uma função 2-D cujas coordenadas e valores de amplitude são inteiros.

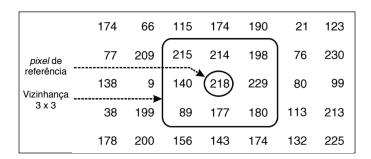

#### 2.2.3 Vizinhança de um *Pixel*

Um  $pixel\ p$  nas coordenadas (x,y) tem quatro vizinhos horizontais e verticais, cujas coordenadas podem ser visualizadas na seguinte forma:

$$(x+1,y), (x-1,y), (x,y+1), (x,y-1)$$

(2.2)

Este conjunto de pixels é chamado de 4-vizinhança de p. Cada pixel está a uma unidade de distância de (x, y), e alguns dos vizinhos de p estão fora da imagem digital se (x, y) estiver na borda da imagem. Os quatro vizinhos que estão na diagonal de p, têm as seguintes coordenadas [13]:

$$(x+1,y+1),(x+1,y-1),(x-1,y+1),(x-1,y-1)$$

(2.3)

Este conjunto de pixels, somado ao conjunto citado em 2.2, formam a 8-vizinhança de p. A maioria das vizinhanças usadas em algoritmos de processamento de imagem são matrizes relativamente pequenas, com o número de linhas igual ao número de colunas, e com um número ímpar de pixels como, por exemplo, a vizinhança 3x3 mostrada na Figura 2.5.

Figura 2.5: Pixel dentro de uma vizinhança [11].

#### 2.2.4 Operações Orientadas a Vizinhança

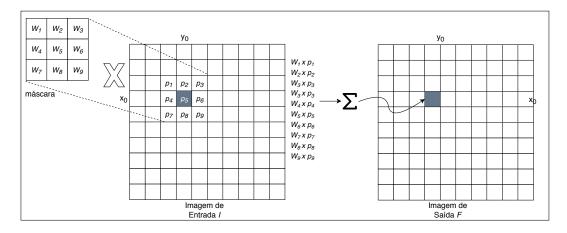

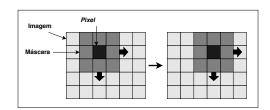

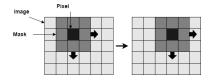

As operações orientadas a vizinhança (também conhecidas como locais ou de área) consistem em determinar o valor de um pixel resultante em coordenadas (x, y) como uma função de seu valor original e o valor de seus vizinhos, geralmente usando uma operação de convolução [11]. A convolução entre uma imagem e um array 2D (conhecido como janela, máscara ou kernel) produz uma imagem de destino, na qual cada valor de pixel depende de seu valor original e do valor dos seus vizinhos. A máscara de convolução determina quais vizinhos são usados, bem como o peso relativo de seus valores originais.

Cada coeficiente da máscara  $(W_1, ..., W_9)$  pode ser interpretado como um peso. A máscara pode ser considerada como uma pequena janela, a qual é sobreposta na imagem para executar o cálculo em um *pixel* por vez. À medida que cada *pixel* é processado, a janela se move para o próximo *pixel* na imagem, e o processo é repetido até que o último *pixel* tenha sido processado.

A convolução é uma operação matemática fundamental, envolvida em algoritmos de processamento de imagem, orientados para a vizinhança linear. A operação pode ser visualizada na Figura 2.7.

| W <sub>1</sub> | W <sub>2</sub> | W <sub>3</sub> |

|----------------|----------------|----------------|

| W <sub>4</sub> | W <sub>5</sub> | W <sub>6</sub> |

| W <sub>7</sub> | W <sub>8</sub> | W <sub>9</sub> |

Figura 2.6: Máscara de convolução 3x3.

Fonte: Adaptado de [11].

Figura 2.7: Processamento de vizinhança para o caso de filtragem linear.

Fonte: Adaptado de [11].

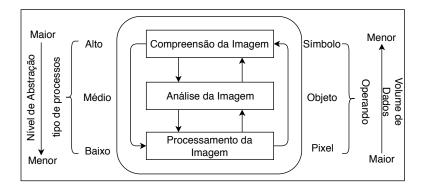

### 2.2.5 Tipos de Processamento Digital de Imagens

No campo de processamento de imagem digital, é possível considerar três tipos de processos informatizados: processos de baixo, médio e alto nível. Processos de baixo nível envolvem operações primitivas, como o pré-processamento de imagens para reduzir o ruído, o aumento do contraste e a nitidez da imagem. Um processo de baixo nível é caracterizado pelo fato de que as entradas e as saídas são imagens.

O processamento de nível médio em imagens envolve tarefas como a segmentação, a descrição desses objetos para reduzi-los a uma forma adequada para processamento computacional e a classificação de objetos individuais. Um processo de nível médio é caracterizado, geralmente, pelo fato de que suas saídas são atributos extraídos dessas imagens (por exemplo, arestas, contornos e a identidade dos objetos individuais). Finalmente, o processamento de alto nível envolve um conjunto de objetos reconhecidos, como na interpretação de imagens [10]. A Figura 2.8 apresenta a estrutura dos processos.

Figura 2.8: Tipos de processamento digital de imagens [14].

### 2.2.6 Segmentação de Imagem

A Segmentação subdivide uma imagem em suas regiões ou objetos constituintes. A Segmentação deve parar quando os objetos de interesse em uma aplicação forem isolados. Os algoritmos de segmentação de imagens geralmente são baseados em uma das duas propriedades básicas de valores de intensidade: descontinuidade e similaridade.

Na primeira categoria, a abordagem é dividir uma imagem com base em mudanças abruptas de intensidade, como bordas em uma imagem. As abordagens principais na segunda categoria são baseadas na partição de uma imagem, em regiões que são semelhantes de acordo com um conjunto de critérios predefinidos. O limiar, o crescimento da região e a divisão e fusão de regiões são exemplos de métodos nessa categoria [10].

### 2.2.7 Detecção de Descontinuidade

A maneira mais comum de procurar descontinuidade é executar uma máscara através da imagem da maneira descrita na seção 2.2.4. Para uma máscara 3x3, como a vista na Figura 2.6, este procedimento envolve a computação da soma dos produtos dos coeficientes, com os níveis de cinza contidos na região abrangida pela máscara [10].

A resposta da máscara em qualquer ponto na imagem é dada por:

$$R = W_1 Z_1 + W_2 Z_2 + \ldots + W_9 Z_9 \tag{2.4}$$

onde  $Z_i$  é o nível de cinza do pixel associado com o coeficiente da máscara  $W_i$ . A resposta da máscara é definida em relação à sua localização central.

#### 2.2.8 Detecção de Linha

Considerando as máscaras mostradas na equação 2.5, da esquerda para direita, caso a primeira máscara fosse movida em torno de uma imagem, ela responderia mais fortemente a linhas (um *pixel* de espessura) orientadas horizontalmente. Com um fundo constante, a resposta máxima teria resultado quando a linha passasse através da linha do meio da máscara. A segunda máscara responde melhor a linhas orientadas a  $+45^{\circ}$ ; a terceira máscara a linhas verticais; e a quarta máscara para linhas na direção  $-45^{\circ}$ . Vale ressaltar que os coeficientes em cada máscara somam zero, indicando uma resposta zero das máscaras em áreas de nível de cinza constante [10].

$$\begin{bmatrix} -1 & -1 & -1 \\ 2 & 2 & 2 \\ -1 & -1 & -1 \end{bmatrix} \begin{bmatrix} -1 & -1 & 2 \\ -1 & 2 & -1 \\ 2 & -1 & -1 \end{bmatrix} \begin{bmatrix} -1 & 2 & -1 \\ -1 & 2 & -1 \\ -1 & 2 & -1 \end{bmatrix} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix}$$

(2.5)

#### 2.2.9 Detecção de Borda

A detecção de bordas é a abordagem mais comum para detectar descontinuidades significativas no nível de cinza. Uma borda é um conjunto de *pixels* conectados que se encontram na fronteira entre duas regiões. As bordas são regiões da imagem onde ocorre uma mudança de intensidade em certo intervalo do espaço, em determinada direção. Isto corresponde a regiões de alta derivada espacial, que contêm alta frequência espacial [10].

Um operador que é sensível às variações abruptas de intensidade, operará como um detector de bordas. Um operador de derivada faz exatamente esta função. Uma interpretação de derivada seria a taxa de mudança de uma função, pois a proporção de variação dos níveis de cinza em uma imagem é maior perto das bordas e menor em áreas constantes. Ao obter os valores de intensidade da imagem e calcular os pontos onde a derivada é um ponto de máximo, tem-se a marcação das bordas [11].

Dado que as imagens são representadas em duas dimensões, é importante considerar mudanças nos níveis de cinza em várias direções. Por esta razão, derivadas parciais das imagens são usadas, com as respectivas direções X e Y. Uma estimativa da direção atual da borda pode ser obtida usando as derivadas X e Y como os componentes da direção ao longo dos eixos, computando-se a soma dos resultados

(a) Imagem de Entrada

(b) Imagem de Saída

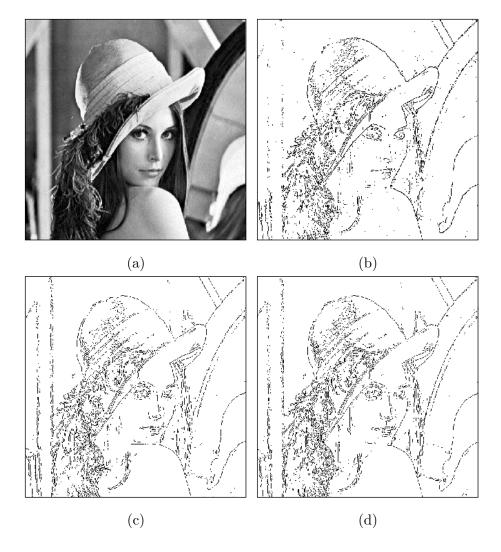

Figura 2.9: Detecção de borda.

parciais. O operador envolvido é o gradiente: se a imagem é vista como uma função de duas variáveis f(x,y), então o gradiente é definido como:

$$\nabla f(x,y) = \left(\frac{\partial f}{\partial x}, \frac{\partial f}{\partial y}\right) \tag{2.6}$$

A magnitude do gradiente é dada por:

$$|\nabla f(x,y)|^2 = \left(\frac{\partial f}{\partial x}\right)^2 + \left(\frac{\partial f}{\partial y}\right)^2$$

(2.7)

Conforme a equação 2.7, a utilização da função magnitude do gradiente na detecção de bordas é computacionalmente muito custosa. O que se faz na prática é a aproximação da equação acima para a forma:

$$\nabla f \approx |Gradiente_x| + |Gradiente_y|$$

(2.8)

Geralmente, a magnitude do gradiente tem um valor alto na borda e baixo no interior da região, o que possibilita a determinação do contorno de uma imagem.

Na Figura 2.9a é mostrada uma imagem fonte à qual será aplicada a operação de detecção de borda. Na Figura 2.9b é mostrado o resultado da operação de detecção de borda, neste caso, o gradiente da imagem,  $|G_x| + |G_y|$ .

O operador de Roberts, aproxima o gradiente de uma imagem por meio de diferenciação discreta [10]. A máscara de Roberts é uma matriz 2x2. Para realizar a detecção de borda com a máscara de Roberts nas direções horizontal e vertical, a imagem inteira é convoluída com os operadores definidos na equação 2.9.

$$\begin{bmatrix} 1 & 0 \\ 0 & -1 \end{bmatrix} \begin{bmatrix} 0 & 1 \\ -1 & 0 \end{bmatrix} \tag{2.9}$$

A máscara de Prewitt é um operador de diferenciação discreta. Este operador usa duas máscaras 3x3 para calcular os valores derivados aproximados nas direções horizontal e vertical. Na equação 2.10 podem ser visualizados os operadores de Prewitt.

$$\begin{bmatrix}

1 & 0 & -1 \\

1 & 0 & -1 \\

1 & 0 & -1

\end{bmatrix}

\begin{bmatrix}

-1 & -1 & -1 \\

0 & 0 & 0 \\

1 & 1 & 1

\end{bmatrix}$$

(2.10)

A máscara de Sobel é similar a máscara de Prewitt. A diferença está relacionada ao peso dos valores de *pixel* em torno da região da borda, aumentando a intensidade da borda. Na equação 2.11 podem ser visualizados os operadores de Sobel.

$$\begin{bmatrix}

1 & 0 & -1 \\

2 & 0 & -2 \\

1 & 0 & -1

\end{bmatrix}

\begin{bmatrix}

-1 & -2 & -1 \\

0 & 0 & 0 \\

1 & 2 & 1

\end{bmatrix}$$

(2.11)

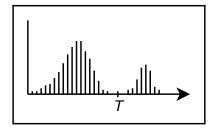

### $2.2.10 \quad Thresholding$

Suponha que o histograma de nível de cinza mostrado na Figura 2.10, corresponde a uma imagem, f(x,y), composta de objetos claros sobre um fundo escuro, de modo que os *pixels* do objeto e do fundo têm níveis de cinza agrupados em dois modos dominantes. Vale ressaltar que os níveis de cinza variam entre o preto como a menor intensidade f(x,y) e o branco como a maior intensidade. Uma maneira de extrair os objetos do fundo é selecionar um *threshold* (limiar) T que separa esses modos. Então qualquer ponto (x,y) para qual f(x,y) > T é chamado de ponto do objeto; caso contrário, o ponto é chamado de ponto de fundo [10].

Figura 2.10: Histograma [10].

#### 2.2.11 Resolução de Imagem

O número de *pixels* contidos numa imagem digital é expresso usando um termo chamado resolução. Este termo refere se ao número de *pixels* contidos na imagem, incorporando a largura e a altura. A resolução dá às imagens digitais suas dimensões 2D.

A resolução de imagem é expressa usando dois números (a largura ou x e a altura ou y) com um sinal de versus (x) no meio. Por exemplo, a resolução VGA comum seria expressa como 640x480. Na tabela 2.1 pode-se visualizar alguns padrões de resoluções de vídeo.

Tabela 2.1: Padrões de resoluções de vídeo

| Padrão de Vídeo | Resolução |

|-----------------|-----------|

| VGA             | 640x480   |

| SVGA            | 800x600   |

| XGA             | 1024x768  |

| SXGA            | 1280x1024 |

| UXGA            | 1600x1200 |

| QXGA            | 2048x1536 |

| Full Resolution | 2592x1944 |

| Tan Resonanon   | 209211944 |

### 2.2.12 Tipos de Imagens Digitais

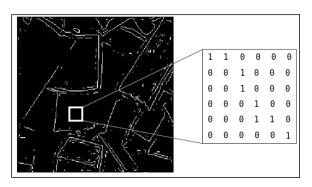

Uma imagem pode ser classificada em 4 tipos: Binária, Escala de Cinza, RGB (*True Color*) e Indexada. Na imagem binária cada *pixel* é somente preto ou branco. Como existem apenas dois valores possíveis para cada *pixel*, têm-se apenas um bit por *pixel*.

Essas imagens podem, portanto, ser muito eficientes em termos de armazenamento. Uma imagem binária pode ser visualizada na Figura 2.11, na qual têm-se 2 cores, branco para as bordas e preto para o fundo.

Figura 2.11: Imagem binária [15].

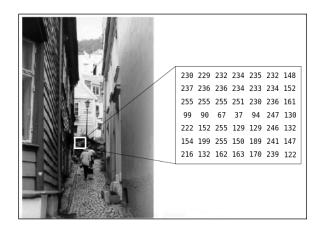

Na imagem em escala de cinza cada *pixel* é um tom de cinza, normalmente de 0 (preto) a 255 (branco). Esse intervalo significa que cada *pixel* pode ser representado por oito bits ou exatamente um byte. Esse é um intervalo muito natural para o manuseio do arquivo de imagem. Na Figura 2.12 é mostrada uma imagem em escala de cinza.

Figura 2.12: Imagem em escala de cinza [15].

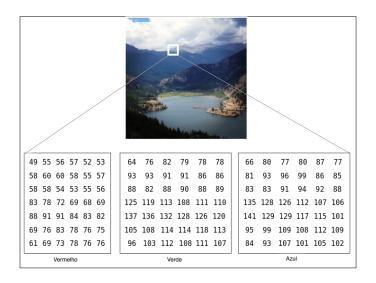

Na imagem RGB cada *pixel* tem uma cor específica. Essa cor pode ser descrita por uma quantidade de vermelho, verde e azul. Se cada um desses componentes tiver um intervalo de 0 a 255, isso dará um total de 256<sup>3</sup> = 16.777.216 cores possíveis diferentes na imagem. Como o número total de bits necessários para cada *pixel* é 24, essas imagens também são chamadas de imagens coloridas de 24 bits. Na figura 2.13 é mostrada uma imagem no formato RGB.

Figura 2.13: Imagem no formato RGB [15].

Uma imagem indexada tem uma matriz de mapa de cores associada. Os valores de *pixel* na imagem são índices diretos em um mapa de cores. Cada posição do mapa de cores armazena três valores em ponto flutuante no intervalo [0,1], especificando os componentes vermelho, verde e azul de uma única cor. Geralmente, as paletas possuem 2, 4, 16 ou 256 cores, representadas, respectivamente, por 1, 2, 4 ou 8 bits.

#### 2.2.13 Tamanho dos Dados de uma Imagem

A quantidade de dados em uma imagem é relativamente grande, e isso afeta quase todos os aspectos do processamento de imagens e vídeos. O volume de dados é um grande problema no processamento, armazenamento, transmissão e exibição de informações de imagem e vídeo.

Considerando uma imagem binária com resolução de 512x512, têm-se que o número de bits pode ser expresso por:

$$nbits = 512 * 512 * 1$$

(2.12)

Dessa forma, pode-se afirmar que a imagem possui 262.144 bits, ou 32.768 bytes. Considerando uma imagem em escala de cinza com resolução 512x512, têm-se que o número de bits pode ser expresso por:

$$nbits = 512 * 512 * 8$$

(2.13)

Dessa forma, pode-se afirmar que a imagem possui 2.097.152 bits, ou 262.144 bytes. Considerando uma imagem no formato RGB ( $True\ Color$ ) com resolução 512x512, têm-se que o número de bits pode ser expresso por:

$$nbits = 512 * 512 * 24$$

(2.14)

Dessa forma, pode-se afirmar que a imagem possui 6.291.456 bits, ou 786.432 bytes.

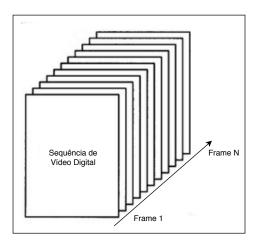

#### 2.3 Vídeo

Um vídeo analógico pode ser representado como um sinal contínuo que varia ao longo do tempo, o qual pode ser expresso por I(x,y,t), sendo x e y as coordenadas espaciais contínuas e t o tempo contínuo. Um vídeo digital pode ser expresso por F(x,y,t), sendo x e y as coordenadas espaciais discretas do quadro de número t, também discreto. O conteúdo de um vídeo digital é uma sequência de imagens digitais chamadas de frames ou quadros, como pode ser visto na Figura 2.14. Assim como para a imagem digital, mostrado na seção 2.2.1, os frames são obtidos por amostragem e quantização do vídeo analógico [11].

Figura 2.14: Sequência de vídeo digital [12].

Um vídeo digital pode ser obtido usando uma câmera de vídeo. A maioria das câmeras de vídeo digitais atuais usa sensores CCD. As câmeras digitais reproduzem a imagem ao longo do tempo, resultando em quadros discretos. Cada quadro consiste

em valores de saída de uma matriz CCD, que é por natureza discreta nas dimensões horizontal e vertical.

Um sinal de vídeo digital pode ser caracterizado por [11]:

- A taxa de *frames* ou quadros;

- O número de linhas; e

- O número de amostras por linha.

A taxa de *frames* define o intervalo de amostragem temporal ou intervalo de quadros. O número de linhas define o intervalo de amostragem vertical, ou seja, a altura da imagem. O número de amostras por linha define o intervalo de amostragem horizontal, ou seja, a largura da imagem.

#### 2.3.1 Scanning

Scanning é um método usado pelos sistemas de vídeo, como parte do processo de conversão de imagens ópticas em sinais elétricos. Este método realiza uma varredura por toda imagem, iniciando no canto superior esquerdo da mesma, movendo-se na direção horizontal através do frame, formando uma linha de varredura. Em seguida, ocorre o retorno para a borda esquerda do frame, iniciando a varredura da próxima linha. Depois que a última linha for varrida, ou seja, quando o ponto de detecção atingir a parte inferior da imagem, o processo de varredura retorna ao canto superior esquerdo da imagem.

Este método pode ser realizado através de duas técnicas:

- Progressive scanning, na qual cada imagem é digitalizada em uma única passagem, chamada frame.

- *Interlaced scanning*, onde cada quadro é digitalizado em duas passagens verticais sucessivas, intercalando-se linhas pares com ímpares.

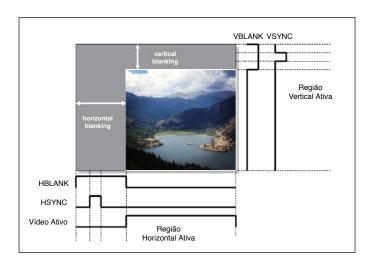

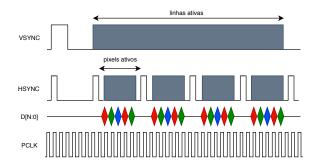

## 2.3.2 Sinais de Temporização do Fluxo de Vídeo

Fluxo de vídeo é uma série de imagens sucessivas. Cada quadro de vídeo consiste em pixels ativos e em branco. O sinal de sincronização horizontal hsync indica o início

da próxima linha. Começando do topo, todas as linhas ativas na área de exibição são escaneadas desta forma. Depois que todo o *frame* de vídeo ativo for escaneado, o sinal de sincronização vertical *vsync* indicará o início de um novo quadro de vídeo.

O intervalo de tempo ao final de cada linha, durante o qual o sinal de vídeo deve ser desativado, antes de uma nova linha ser escaneada, é conhecido como *Blanking Interval*. A taxa na qual as imagens são exibidas é conhecida como *frame rate*. A Figura 2.15 apresenta os sinas de temporização do fluxo de vídeo.

Figura 2.15: Sinais de temporização do fluxo de vídeo [12].

## 2.4 Processamento de Imagens em Tempo Real

Um Sistema de Tempo Real é um sistema computacional que deve reagir a estímulos oriundos do seu ambiente em prazos específicos [16]. A reação dos sistemas de tempo real aos eventos vindo do ambiente externo ocorre em tempos compatíveis com as exigências do ambiente e mensuráveis na mesma escala de tempo. A concepção do sistema de tempo real é diretamente relacionada com o ambiente no qual está relacionado e com o comportamento temporal do mesmo [16].

Na perspectiva de processamento de imagens, um sistema de geração de imagens em tempo real é aquele que captura imagens regularmente, analisa essas imagens para obter alguns dados e, em seguida, usa esses dados para controlar alguma atividade, respeitando uma restrição temporal. Esse sistema envolve o processamento de grandes quantidades de dados de imagem em tempo hábil, com o objetivo de extrair informações úteis. Imagens digitais e vídeo são essencialmente sinais multi-

dimensionais, apresentando um grande volume de dados, exigindo uma quantidade significativa de recursos de computação e memória para seu processamento. Um dos desafios em sistemas de processamento de imagens em tempo real é como lidar com a quantidade de processamento e cálculos.

Os sistemas em tempo real são categorizados em dois tipos [17]:

- O sistema de tempo real crítico (hard real time), é considerado falho, caso a saída não seja produzida dentro do intervalo de tempo predefinido.

- O sistema de tempo real não-crítico (soft real time), define que o sistema não é considerado falho, caso a saída não seja produzida dentro do intervalo de tempo predefinido, porém o desempenho se deteriora.

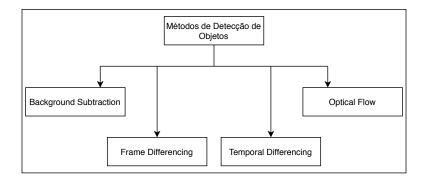

## 2.5 Métodos para a Detecção de Objetos

De acordo com [18], as principais abordagens utilizadas para a detecção de objetos são *Background Subtraction*, *Frame Differencing*, *Temporal Differencing* e *Optical Flow*, como pode ser visualizado na Figura 2.16.

Figura 2.16: Métodos para a detecção de objetos.

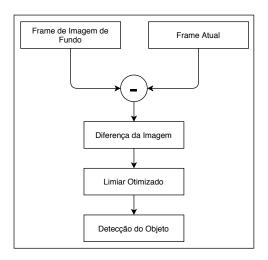

Background Subtraction é o método mais usado para a detecção de objetos, o qual consiste no processo de separação de objetos em foreground (primeiro plano) e background (imagem de fundo) em uma sequência de quadros de vídeo. O conceito fundamental é a diferença entre o quadro atual e o quadro de referência. O quadro de referência também é chamado como imagem de fundo [18]. Embora esse método forneça um bom contorno dos objetos, ele é baseado em um plano de fundo estático, portanto, qualquer alteração na imagem será marcada como primeiro plano. Além

disso, o modelo de imagem de fundo deve ser atualizado ao longo do tempo, para se adaptar às mudanças dinâmicas da cena. Na Figura 2.17 pode ser visualizado o fluxograma do método *Background Subtraction*.

Figura 2.17: Conceito geral do método Background Subtraction.

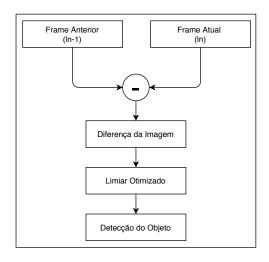

Segundo [19], o Frame Differencing é o método que identifica a presença de um objeto considerando a diferença entre dois quadros, subtraindo a segunda imagem do primeiro quadro de imagem, usando o operador de subtração de imagem nos quadros consecutivos, para obter a saída desejada. O algoritmo pode ser subdividido em três partes. O passo inicial é a seleção de opções de imagem de fundo. O segundo passo é a operação de subtração aritmética e o terceiro passo é a seleção de limiar adequado. O método deve retornar o contorno do objeto identificado. Na Figura 2.18 pode ser visualizado o fluxograma do método Frame Differencing.

Figura 2.18: Conceito geral do método frame differencing.

De acordo com [20], a diferenciação temporal ou *Temporal Differencing* é baseada na diferença de quadros, que tenta detectar regiões em movimento usando a diferença de quadros consecutivos (dois ou três), em uma sequência de vídeo. Este método é adequado para o caso de objeto movimentando-se em um cenário de fundo estático. Portanto, a diferenciação temporal é boa em fornecer informações iniciais de áreas de movimento, no entanto as regiões convergentes podem ser detectadas como objetos em movimento, portanto, a saída pode conter ruídos devido a um erro de estimativa de movimento.

O método Optical Flow baseia-se no cálculo do campo de fluxo óptico do quadro de imagem ou vídeo. O agrupamento é realizado com base nas informações de distribuição de fluxo óptico obtidas da imagem. Para cada pixel, um vetor de velocidade é calculado, dependendo da direção do movimento do objeto e da rapidez com que o pixel se move pela imagem. Este método permite obter o conhecimento completo sobre o movimento do objeto, sendo útil para determinar o movimento do objeto a partir da imagem de fundo. A desvantagem deste método é a grande quantidade de cálculos que são necessários para obter informações sobre o fluxo óptico.

# 2.6 Trabalhos Correlatos

A detecção de objetos é um componente essencial para várias aplicações de visão computacional e processamento de imagem. Nesse contexto, alguns trabalhos correlatos já foram desenvolvidos, com a utilização de algoritmos encontrados na literatura. Nesta seção, serão abordados alguns destes trabalhos que apresentam conceitos e técnicas similares às utilizadas neste projeto.

No trabalho proposto em [21] foi desenvolvido um sistema que detecta e classifica objetos numa imagem. O projeto implementa o algoritmo SIFT (*Scale Invariant Feature Transform*) como uma aplicação executada no sistema operacional Ubuntu Linux, na placa de desenvolvimento Zedboard FPGA. Com a estrutura apresentada, foi possível realizar a detecção e classificação de objetos usando a biblioteca OpenCV. O sistema é composto por funções desenvolvidas tanto em software (algoritmo SIFT), quanto em hardware. O autor não informa os dados referentes ao desempenho, quando comparado ao processamento serial usando uma CPU, tampouco os dados

da resolução da imagem ou frequência máxima do circuito em hardware.

Segundo [22], foi desenvolvido um sistema que implementa o rastreamento de objetos, implementando o algoritmo de Canny para detecção de bordas, usando o FPGA Xilinx Spartan-III XC3S500E. O papel do algoritmo de rastreamento é a análise dos quadros de vídeo, para estimar o movimento dos parâmetros. Esses parâmetros caracterizam a localização do objeto. O sistema suporta o processamento de imagens com a resolução de 640x480 pixels. A taxa de quadros de vídeo processados é de 1 quadro por segundo. O autor não cita os dados referentes ao desempenho, quando comparado ao processamento serial usando uma CPU ou a frequência máxima do circuito em hardware.

De acordo com [23], foi proposto e implementado um sistema de detecção de objetos no Xilinx MicroBlaze soft-core processor. O sistema implementa a técnica background subtraction, que permite que o objeto seja identificado através da diferença da imagem atual e o plano de fundo da imagem. Neste projeto foi utilizada a ferramenta XPS (Xilinx Platform Studio), para escrever o algoritmo usando a linguagem C. A ferramenta XPS é usada para a integração entre o software e o Xilinx MicroBlaze soft-core processor. O dispositivo FPGA utilizado neste trabalho foi o SPARTAN-3 XC3S200TQ-144. As imagens são obtidas no dispositivo FPGA através do protocolo RS-232. O sistema suporta o processamento de imagens com as resoluções de 320x240 pixels e 160x120 pixels. A taxa de quadros de vídeo capturados pode ser de 15 quadros por segundo ou 30 quadros por segundo. O autor não cita os dados referentes ao desempenho, quando comparado ao processamento serial usando uma CPU ou a frequência máxima do circuito em hardware.

No trabalho proposto em [24], foi desenvolvida uma arquitetura de hardware para a detecção de objetos, usando a linguagem de descrição de hardware VHDL e implementada usando o dispositivo FPGA Spartan-6 XC6SLX45-2csg324. O sistema implementa a técnica background subtraction modificada. Neste método, a segmentação de objetos é feita usando a subtração. Esta técnica calcula a diferença de duas imagens usando pixel por pixel, e continua por todos os pixels no quadro de vídeo. O sistema suporta o processamento de imagens com a resolução de 256x256 pixels, podendo operar com uma frequência máxima de 164 MHz. O autor não cita os dados referentes ao desempenho, quando comparado ao processamento serial

usando uma CPU.

O diferencial deste trabalho em comparação aos trabalhos correlatos é a implementação do sistema de detecção de objetos em FPGA utilizando conceitos abordados nos métodos Frame differencing, Temporal Differencing e Background subtraction. O projeto de circuito digital foi codificado usando a linguagem Verilog, o ambiente de verificação foi desenvolvido e estruturado com a metodologia UVM e System Verilog e a prototipação realizada no kit FPGA Intel DE2-115. Com relação ao desempenho foram obtidos resultados com um speedup de 310x para a implementação do algoritmo de detecção de objetos em FPGA, quando comparada à implementação no software Matlab.

# Capítulo 3

# Metodologia do Projeto de Circuitos Integrados Digitais

O tradicional fluxo de projeto, para a implementação de um sistema completo em um dispositivo FPGA (Field-Programmable Gate Array), adota uma abordagem top-down, que apresenta uma divisão em níveis bem definidos. Segundo [25], atualmente os fornecedores de FPGA provêm um conjunto completo de ferramentas que permitem a automatização de tarefas, abrangendo desde as etapas de especificação do projeto até a geração do bitstream, para a programação do dispositivo FPGA.

O aumento na capacidade com relação à recursos e desempenho de dispositivos FPGA tem possibilitado o uso de tais dispositivos em projetos muito mais complexos, visando o desenvolvimento das aplicações utilizando o fluxo de projeto em FPGA. De acordo com [26], a utilização de arquiteturas de hardwares reconfiguráveis tem crescido entre os projetistas de diferentes áreas como robótica, telecomunicações, processamento digital de sinais e imagens, equipamentos médicos e automotiva, bem como na área de projetos de circuitos integrados (emulação/verificação). Segundo [9], foram obtidos avanços com a utilização de dispositivos FPGAs para a aceleração da computação de alto desempenho.

A facilidade para reconfigurar e recompilar um circuito digital, descrito em código RTL no dispositivo FPGA, reduz o tempo gasto para identificação e correção de erros, proporcionando mais tempo de verificação funcional no sistema. Essa característica pode acelerar o ciclo de verificação do projeto, bem como o ciclo de integração do sistema, ocasionando uma redução no tempo de desenvolvimento do

projeto. No entanto, essa melhora na produtividade somente será alcançada com a aplicação de uma metodologia de projeto adequada.

# 3.1 Arquitetura de Hardware Reconfigurável

Segundo [25], um FPGA é um dispositivo lógico que contém uma matriz bidimensional de células lógicas genéricas e programáveis. Uma célula lógica pode ser programada para executar uma função simples, bem como uma configuração pode ser personalizada, para prover interconexões entre as células lógicas. Um dispositivo FPGA pode fornecer diversos blocos de entrada/saída e suporte para vários padrões de entrada/saída. Estes circuitos fazem a interface entre os blocos internos da FPGA e os pinos externos.

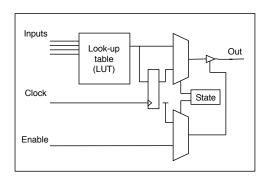

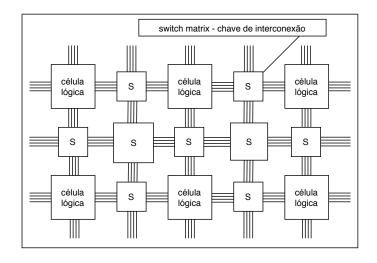

FPGA usa o conceito de um bloco lógico complexo. A CLB (*Configurable Logic Blocks*), consiste num circuito para implementar a lógica e um CLB típico é mostrado na Figura 3.1. Cada bloco lógico é contornado por canais de roteamento, conectados por meio de matriz de chaveamento ou de interconexões. A matriz de chaveamento conecta os fios nos canais adjacentes, através de transistores de passagem ou *buffers* bidirecionais [27].

Figura 3.1: Bloco lógico configurável FPGA [28].

O CLB possui uma *look-up table* (LUT) que pode ser configurada para fornecer um tipo específico de função lógica, quando programado. Existe também um *flip-flop* do tipo D com *clock*, que permite que o CLB seja combinacional (sem *clock*) ou síncrono (com *clock*), além de um sinal de habilitação.

Um FPGA típico terá centenas ou milhares de CLB, de diferentes tipos, em um único dispositivo, permitindo que dispositivos muito complexos sejam implementados em um único *chip*, bem como configurados facilmente. A estrutura conceitual de um dispositivo FPGA pode ser vista na Figura 3.2.

Figura 3.2: Estrutura conceitual de um dispositivo FPGA.

Fonte: Adaptado de [27].

Um projeto de circuito digital personalizado pode ser implementado especificando a função de cada célula lógica, possibilitando a conexão de cada chave programável. Uma vez que o projeto e a síntese são concluídos, pode-se usar um cabo adaptador simples, para baixar a configuração para o dispositivo FPGA e obter o circuito personalizado. Esta característica torna o dispositivo FPGA reprogramável.

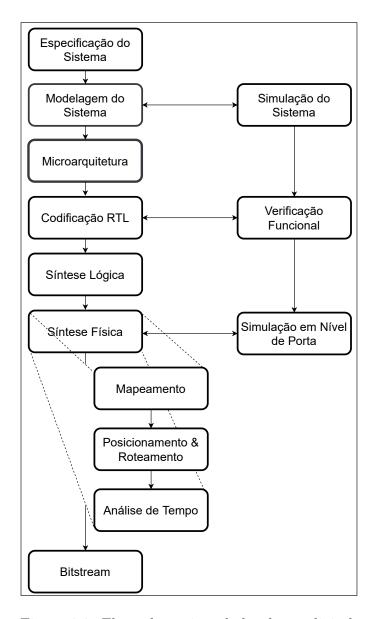

# 3.2 Fluxo de Projeto em FPGA

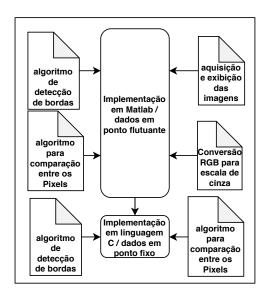

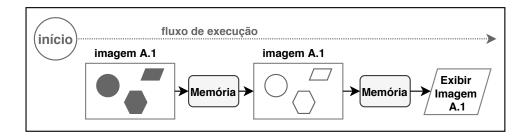

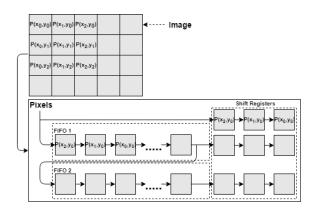

Inicialmente é desenvolvido o documento de especificação, onde são definidas todas as funcionalidades do sistema, as interfaces internas e externas, os objetivos da aplicação e as restrições (constraints) que devem ser cumpridas para que o objetivo seja alcançado. Paralelamente à especificação do projeto, segundo [29], o sistema pode ser modelado e representado em uma ferramenta dedicada de alto nível como Matlab, ou linguagens de programação como C/C++. Esta modelagem é utilizada para a validação dos conceitos, e posteriormente poderá ser usada como Modelo de Referência, para a verificação funcional.

O próximo nível é o desenvolvimento da microarquitetura e nesta etapa são especificados os detalhes da arquitetura, estrutura dos blocos, funções e interfaces. Alguns recursos como diagramas de blocos, fluxogramas e gráficos, podem ser usados

para obter uma melhor representação da microarquitetura.

Baseado na microarquitetura desenvolvida, é iniciado o estágio de codificação RTL (Register-Transfer Level), através de uma HDL (Hardware Description Language). Esse processo, resulta numa forma de descrição da operação do circuito digital, na qual o comportamento do sistema é definido, em termos do fluxo de sinais entre registradores e das operações realizadas, mediante etapas de controle definidas através de pulsos de clock. Nesta etapa, os projetistas podem utilizar módulos proprietários codificados em RTL disponibilizados por diversas empresas com o objetivo de otimizar o desenvolvimento, chamados de IP (Intellectual Property). De acordo com [30], a detecção de uma função incorreta, tem se tornado um dos grandes desafios de todo o fluxo de projeto em FPGA.

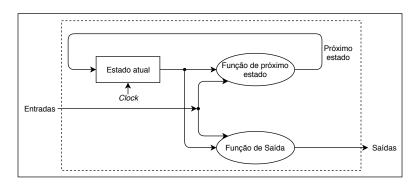

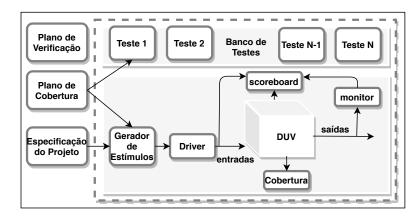

A verificação funcional garante que o projeto de circuito digital execute as tarefas como pretendido pela arquitetura geral do sistema. A execução desta fase pode ser realizada de forma paralela ao estágio de codificação RTL. Inicialmente é elaborado um Plano de Verificação que inclui os objetivos, componentes e detalhes da estratégia de verificação. Baseado no plano de verificação, é desenvolvido um ambiente de verificação funcional e, através destes componentes, são criados mecanismos que visam a automatização de tarefas, referentes à ampla atividade de verificação. Atualmente é recomendado o uso de uma metodologia de verificação, como a metodologia UVM (Universal Verification Methodology) [31].

A próxima etapa é a síntese lógica, na qual é gerada uma netlist descrevendo todos os elementos combinacionais (portas lógicas simples e agregadas), sequenciais (flip-flops) e de interconexão (fios) que representam logicamente o circuito. As entradas desta etapa são o RTL e as restrições de desempenho (área, consumo e tempo). Segundo [27], esse processo pode ser otimizado, com o intuito de obter o menor consumo de energia, a menor área ou a maior velocidade. A etapa de síntese física abrange as seguintes fases: mapeamento, posicionamento e roteamento. A etapa de mapeamento determina como a lógica é mapeada para os diferentes tipos de componentes específicos disponíveis no FPGA. A etapa de posicionamento associa efetivamente componentes físicos do FPGA aos mapeamentos genéricos realizados na etapa anterior. A etapa de roteamento consiste no processo em que é feita a configuração das chaves comutadoras dos fios metálicos, que interconectam as células

lógicas, de armazenamento e de E/S do FPGA. No entanto, somente nos casos de projeto de circuitos digitais com alta complexidade, o projetista tem a necessidade de executar a etapa de síntese física de forma avançada, caso contrário a ferramenta é encarregada de realizar este procedimento, de forma automática e otimizada. O resultado deste estágio é um modelo do sistema em nível de portas, portanto o objeto gerado é novamente verificado funcionalmente, considerando o resultado da etapa de análise de tempo. Uma checagem sobre as restrições de tempo é realizada, a partir da especificação do arquivo SDC (Synopsys Design Constraints).

A última etapa é a geração do bitstream. Nesta fase são usadas ferramentas que executam tarefas automatizadas visando o mapeamento, alocação e roteamento do design, resultando no bitstream usado para programar a lógica e as interconexões do dispositivo FPGA. Após a configuração do FPGA, são feitos testes operacionais iniciais, bem como o monitoramento das funções implementadas. Na Figura 3.3 é mostrado o diagrama do fluxo de projeto.

#### 3.2.1 Especificação do Sistema

Nesta etapa deve ser elaborado o documento de especificação do projeto. Uma especificação é um conjunto de requisitos que devem ser atendidos por um material, produto ou serviço. O documento de especificação é um balizador para todas as etapas seguintes do fluxo de projeto em FPGA. Alguns modelos [32] sugerem que o documento de especificação, contenha as seguintes informações: visão geral do projeto, objetivos, principais características, requisitos funcionais, requisitos não-funcionais, restrições, dentre outros tópicos relevantes.

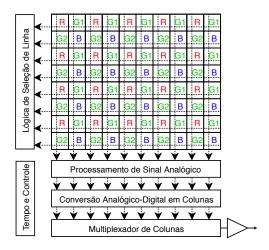

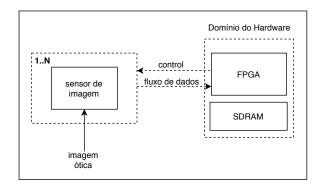

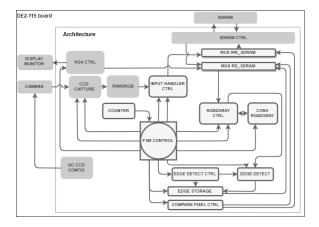

Para a utilização do Fluxo de Projeto de Hardware Digital no sistema proposto neste trabalho, é necessário obter uma visão geral da aplicação proposta e determinar seus principais requisitos. O sistema de detecção de objetos em uma cena fixa em vídeos digitais, tem como propósito capturar imagens de vídeos, através da interface da câmera TRDB-D5M Terasic CMOS sensor, bem como processar e armazenar os quadros das imagens de vídeo e, por fim, apresentar os resultados através do monitor VGA (Video Graphics Array), utilizando o kit FPGA Intel DE2-115. A partir de um conjunto de quadros de imagens recebidos como entrada, o sistema poderá identificar os objetos realizando a comparação entre um quadro de imagem capturado, num

Figura 3.3: Fluxo de projeto de hardware digital.

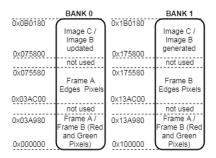

período de tempo mais recente, com um quadro de imagem capturado, num período de tempo mais antigo. Na Figura 3.4, é apresentada uma visão geral do sistema proposto.

Figura 3.4: Visão geral do sistema proposto.

Os requisitos funcionais devem ser listados, para que o projetista prossiga com o

desenvolvimento do sistema. Para esta aplicação, alguns requisitos funcionais mais relevantes foram selecionados:

- O processo de identificação de objetos é aplicado somente a um único quadro de imagem de vídeo capturado. A cada período de tempo determinado, um novo quadro de imagem de vídeo é capturado.

- A identificação dos objetos é realizada através do processo de detecção de borda, utilizando o operador de Sobel.

- O resultado obtido com a identificação do objeto é apresentado no monitor VGA, sendo o quadro da imagem de vídeo em RGB e o objeto visualmente destacado.