# UNIVERSIDADE FEDERAL DA BAHIA ESCOLA POLITÉCNICA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Igo Amauri dos Santos Luz

# SISTEMA ONLINE EM FPGA PARA REDUÇÃO DA SOBREPOSIÇÃO DE SINAIS NUM DETECTOR DE PARTÍCULAS

DISSERTAÇÃO DE MESTRADO

Salvador Dezembro de 2016

### Página em branco

#### Igo Amauri dos Santos Luz

# SISTEMA ONLINE EM FPGA PARA REDUÇÃO DA SOBREPOSIÇÃO DE SINAIS NUM DETECTOR DE PARTÍCULAS

Dissertação de Mestrado apresentada ao Programa de Pós-graduação em Engenharia Elétrica, PPGEE, da Universidade Federal da Bahia, como parte dos requisitos necessários à obtenção do título de Mestre em Engenharia Elétrica.

Orientadores: Eduardo F. de Simas Filho Paulo C. M. de Abreu Farias

Salvador Dezembro de 2016

Luz, Igo Amaurí dos Santos Sistema Online em FPGA para Redução da Sobreposição de Sinais num Detector de Partículas / Igo Amaurí dos Santos Luz. --Salvador, 2016.

Orientador: Eduardo Furtado de Simas Filho. Coorientador: Paulo Cesar Machado de Abreu Farias. Dissertação (Mestrado - Programa de pós-graduação em Engenharia Elétrica) -- Universidade Federal da Bahia, Escola Politécnica, 2016.

130 f. : il

1. Instrumentação Eletrônica. 2. Processamento Digital de Sinais. 3. Filtro Digital. 4. Deconvolução. 5. FPGA. I. Filho, Eduardo Furtado de Simas. II. Farias, Paulo Cesar Machado de Abreu. III. Título.

# SISTEMA ONLINE EM FPGA PARA REDUÇÃO DA SOBREPOSIÇÃO DE SINAIS NUM DETECTOR DE PARTÍCULAS

Igo Amauri dos Santos Luz

DISSERTAÇÃO SUBMETIDA AO CORPO DOCENTE DO PROGRAMA DE PÓS-GRADUAÇÃO E PESQUISA DE ENGENHARIA (PPGEE) DA UNIVERSIDADE FEDERAL DA BAHIA COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE MESTRE EM CIÊNCIAS EM ENGENHARIA ELÉTRICA.

| A | provada | por: |

|---|---------|------|

|   |         | P    |

Prof. Eduardo F. Simas Filho, D.Sc. - Orientador

Prof. Paulo Cesar M. Abreu Farias, D.Sc. - Coorientador

Harris

Prof Amauri Oliveira, D.Sc. - Avaliador UFBA

Prof Edson Pinto Santana, D.Eng. - Avaliador UFBA

Prof Herman Pessoa Lima Jr , D.Sc. - Avaliador CBPF

SALVADOR, BA – BRASIL DEZEMBRO DE 2016 dos Santos Luz, Igo Amauri

Sistema Online em FPGA para Redução da Sobreposição de Sinais num Detector de Partículas/Igo Amauri dos Santos Luz. — Salvador: UFBA/PPGEE, 2016.

XVII, 112 p.: il.; 29,7cm.

Orientadores: Eduardo F. de Simas Filho

Paulo C. M. de Abreu Farias

Dissertação (mestrado) – UFBA/PPGEE/Programa de Engenharia Elétrica, 2016.

Referências Bibliográficas: p. 90 – 97.

- Instrumentação Eletrônica.

Processamento

Digital de Sinais.

Filtro Digital.

Deconvolução.

- 5. FPGA. 6. Física de Partículas. 7. Calorímetro.

- 8. ATLAS. I. de Simas Filho, Eduardo F. *et al.*. II. Universidade Federal da Bahia, PPGEE, Programa de Engenharia Elétrica. III. Título.

## Agradecimentos

Agradeço, primeiramente, aos meus pais, pelo irrestrito esforço para me proporcionar uma educação de qualidade.

A Rafael Ramos, pelo constante apoio e incentivo.

Aos meus amigos, em especial à Nildo Mascarenhas, Leilane Paixão, Eudes Benicio, Rosileide Santos, Edjane Moreira, Nelson Alves e Camila Pinheiro.

Aos meus orientadores, Prof. Dr. Eduardo Simas e Prof. Dr. Paulo Cesar. Obrigado por todo o ensinamento e contribuições para o meu crescimento enquanto pesquisador. À todos os professores e funcionários do PPGEE/UFBA.

Agradeço, também, aos pesquisadores da Colaboração do ATLAS, em especial à Me. João Paulo Duarte, Prof. Dr. Luciano Andrade e Prof. Dr. José Seixas, pelas contribuições essenciais no desenvolvimento desse trabalho.

E, por fim, à FAPESB, FAPERJ, CAPES, CNPq e RENAFAE (MCTI) pelo apoio financeiro.

Resumo da Dissertação apresentada à PPGEE/UFBA como parte dos requisitos necessários para a obtenção do grau de Mestre em Engenharia Elétrica (M.Sc.)

SISTEMA ONLINE EM FPGA PARA REDUÇÃO DA SOBREPOSIÇÃO DE SINAIS NUM DETECTOR DE PARTÍCULAS

Igo Amauri dos Santos Luz

Dezembro/2016

Orientadores: Eduardo F. de Simas Filho

Paulo C. M. de Abreu Farias

Programa: Engenharia Elétrica

A sobreposição de sinais pode ocorrer em diversos sistemas de instrumentação. Esse fenômeno está relacionado à taxa de ocorrência dos eventos e ao tempo de resposta dos sensores. No âmbito dos detectores de partículas, que caracterizamse por possuírem altas taxas de ocorrência de eventos, o sistema responsável pela medição de energia (calorímetro) possui limitações em termos do tempo de resposta, provocando restrições em relação ao aumento na taxa de ocorrência das colisões das partículas. Essa situação apresenta-se como um desafio quando o avanço nas pesquisas está atrelado ao aumento da taxa de colisões gerada pelos aceleradores de partículas, como é o caso do Large Hadron Collider (LHC). O ATLAS é um dos detectores do LHC e seu sistema de instrumentação não está preparado para lidar com o aumento da taxa de ocorrência de eventos, pois isso irá gerar sobreposição entre eventos sequenciais. Para atenuar esse problema, torna-se necessário realizar, de modo online, o processamento digital da informação. Nesse sentido, esse trabalho propõe a implementação de um circuito eletrônico dedicado em plataforma digital reconfigurável utilizando técnicas de filtragem de sinais. Cada filtro é uma aproximação da inversa da resposta ao impulso do canal de medição, realizando a deconvolução dos sinais medidos. A avaliação do funcionamento e desempenho dos

iv

filtros foi realizada através de um conjunto de dados simulados, que consideram o funcionamento real do detector. A partir dos resultados alcançados, pôde-se constatar que as técnicas implementadas atenderam aos requisitos de funcionamento exigido.

Abstract of Dissertation presented to PPGEE/UFBA as a partial fulfillment of the requirements for the degree of Master of Science (M.Sc.)

# FPGA-BASED ONLINE SYSTEM TO REDUCE THE SIGNAL PILEUP EFFECT IN A PARTICLE DETECTOR

Igo Amauri dos Santos Luz

December/2016

Advisors: Eduardo F. de Simas Filho

Paulo C. M. de Abreu Farias

Department: Electrical Engineering

The pileup effect can occur in several instrumentation systems. This phenomenon is related to the rate of occurrence of the events and the response time of the sensors. In the particle detectors, the electronic system responsible for measuring energy (calorimeter) has limitations in terms of response time when it operates with high rate of occurrence of events. This situation represents a challenge when the advance in the research is linked to the increase of the collision rate generated by the particle accelerators, such as the LHC. ATLAS is one of the LHC detectors and its instrumentation system is not prepared to deal with the increase rates of occurrence of events, because it will generate superimposition of information from subsequent events. To mitigate this problem it is necessary to perform an online digital signal processing. So, this work proposes a dedicated signal processing system embedded on a digital high-performance reconfigurable electronic platform that implements digital signal filtering techniques. Each filter is an inverse approximation of the inverse impulse response of the measuring channel, performing the deconvolution of the measured signals. The evaluation of the operation and performance of the implemented filters was performed through the use of a simulated data set, which considers the actual operation of the detector. From the achieved results, it was verified that the implemented techniques met the system operating requirements.

# Sumário

| Li | sta c | le Figuras                                                               | ix         |

|----|-------|--------------------------------------------------------------------------|------------|

| Li | sta d | le Tabelas                                                               | xiii       |

| Li | sta d | le Abreviaturas                                                          | xiv        |

| 1  | Inti  | rodução                                                                  | 1          |

|    | 1.1   | Objetivos                                                                | 3          |

|    | 1.2   | Resultados em Publicações                                                | 4          |

|    | 1.3   | Organização da Dissertação                                               | 7          |

| 2  | Inti  | rodução à Física de Partículas e ao Acelerador LHC                       | 8          |

|    | 2.1   | Histórico da Física de Partículas                                        | 8          |

|    | 2.2   | O LHC                                                                    | 11         |

|    | 2.3   | O Detector ATLAS                                                         | 14         |

|    |       | 2.3.1 A Calorimetria do ATLAS                                            | 16         |

|    |       | 2.3.2 O Sistema Online de Seleção de Eventos ( <i>Trigger</i> ) do ATLAS | 20         |

| 3  | Atu   | alização do LHC e os Métodos de Estimação de Energia                     | <b>2</b> 3 |

|    | 3.1   | Introdução                                                               | 23         |

|    | 3.2   | Sistema Eletrônico Atual do Primeiro Nível de Trigger Baseado em         |            |

|    |       | Calorimetria                                                             | 26         |

|    | 3.3   | Sistema Eletrônico que será Utilizado após a Atualização do LHC $$       | 29         |

|    | 3.4   | Técnica Atual de Estimação de Energia                                    | 32         |

|    |       | 3.4.1 O Filtro Casado                                                    | 33         |

|    |       | 3.4.2 Detector de Picos                                                  | 35         |

|    | 3.5   | Proposta de Nova Técnica de Estimação de Energia                         | 37         |

|              |       | 3.5.1   | Filtros Digitais e a Teoria da Convolução          | 38         |

|--------------|-------|---------|----------------------------------------------------|------------|

|              |       | 3.5.2   | Método Determinístico                              | 43         |

|              |       | 3.5.3   | Método Iterativo                                   | 47         |

| 4            | Arq   | uitetu  | ra de Hardware Desenvolvida                        | 51         |

|              | 4.1   | Introd  | ução                                               | 51         |

|              | 4.2   | Proces  | ssamento Paralelo e Diferentes Domínios de $Clock$ | 55         |

|              | 4.3   | Imple   | mentação do Método Determinístico                  | 57         |

|              | 4.4   | Imple   | mentação do Gradiente Descendente Positivo         | 58         |

|              | 4.5   | Verific | eação Funcional                                    | 62         |

| 5            | Res   | ultado  | ${f s}$                                            | <b>6</b> 4 |

|              | 5.1   | Geraç   | ão dos Sinais Simulados                            | 64         |

|              | 5.2   | Métod   | lo Determinístico                                  | 66         |

|              |       | 5.2.1   | Simulação do Método Determinístico                 | 66         |

|              |       | 5.2.2   | Síntese FPGA do Método Determinístico              | 73         |

|              | 5.3   | Métod   | lo Iterativo: Gradiente Descendente Positivo       | 74         |

|              |       | 5.3.1   | Simulação do Método Iterativo                      | 75         |

|              |       | 5.3.2   | Síntese FPGA do Método Iterativo                   | 77         |

|              | 5.4   | Anális  | se dos Resultados                                  | 83         |

| 6            | Con   | clusõe  | es                                                 | 87         |

| Re           | eferê | ncias I | Bibliográficas                                     | 90         |

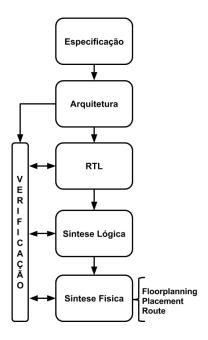

| $\mathbf{A}$ | Pro   | jeto de | e Hardware Digital                                 | 98         |

|              | A.1   | Introd  | ução                                               | 98         |

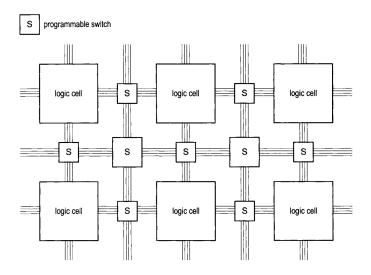

|              | A.2   | Field-  | Programmable Gate Arrays - FPGA                    | 100        |

|              |       | A.2.1   | Família Virtex-7 da Xilinx                         | 102        |

|              |       | A.2.2   | Estruturas de DSP                                  | 104        |

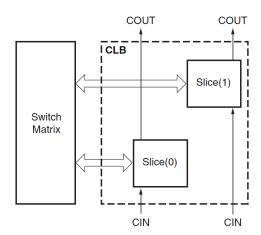

|              |       | Δ 2 3   | Bloco de Lógica Configurável                       | 105        |

# Lista de Figuras

| 2.1  | Esquema do aparelho usado para medir a deflexão elétrica e magnética      |    |

|------|---------------------------------------------------------------------------|----|

|      | dos raios catódicos [15]                                                  | 9  |

| 2.2  | Diagrama do modelo padrão [22]                                            | 12 |

| 2.3  | Fotografia do túnel do LHC [32]                                           | 13 |

| 2.4  | Ilustração da localização dos quatro maiores detectores do LHC ao         |    |

|      | longo do percurso do acelerador [22]                                      | 14 |

| 2.5  | Esquemático dos detectores do ATLAS [22]                                  | 15 |

| 2.6  | Eixo de coordenadas do ATLAS [22]                                         | 16 |

| 2.7  | Corte transversal do ATLAS [22]                                           | 18 |

| 2.8  | Diagrama dos calorímetro eletromagnético e hadrônico do ALTAS [42].       | 18 |

| 2.9  | Ilustração do formato do $TileCal$ [45]                                   | 19 |

| 2.10 | Exemplo de Segmentação de uma parte do TileCal [47]                       | 20 |

| 2.11 | Sistema de filtragem do ATLAS [22]                                        | 21 |

| 2.12 | Diagrama de Blocos do Nível 1 do <i>Trigger</i> [4]                       | 21 |

| 3.1  | Representação gráfica da Resposta ao Impulso Típica de um sensor [47].    | 24 |

| 3.2  | Representação gráfica do efeito de empilhamento de sinais medidos $[47].$ | 24 |

| 3.3  | Arquitetura do $\textit{Trigger}$ L1 baseado em calorimetria atual [47]   | 25 |

| 3.4  | Arquitetura do Trigger L1 baseado em calorimetria em desenvolvi-          |    |

|      | mento [47]                                                                | 25 |

| 3.5  | Representação gráfica do módulo do $\it TileCal~[32].~\dots$              | 26 |

| 3.6  | Esquemático da eletrônica de uma gaveta do TileCal [32]                   | 27 |

| 3.7  | Representação gráfica do caminho do sinal na arquitetura atual do         |    |

|      | TileCal [5]                                                               | 28 |

| 3.8  | Representação gráfica do caminho da informação na atualização dos            |    |

|------|------------------------------------------------------------------------------|----|

|      | sistemas eletrônicos do $TileCal$ [51]                                       | 29 |

| 3.9  | Protótipo da Proposta de Arquitetura de Modificação do Front-End             |    |

|      | Baseado no Cartão 3 em 1 [53]                                                | 30 |

| 3.10 | Diagrama do Fluxo do Sinal do $Front\text{-}End$ Baseado no Chip $QIE$ [52]. | 30 |

| 3.11 | Diagrama do Fluxo do Sinal do Front-End Baseado no Chip FATA-                |    |

|      | LIC [52]                                                                     | 31 |

| 3.12 | Protótipo $sROD$ para Atualização do Sistema Eletrônico [57]                 | 32 |

| 3.13 | Representação gráfica do sinal transmitido e recebido pela atual ar-         |    |

|      | quitetura do BCID [9]                                                        | 33 |

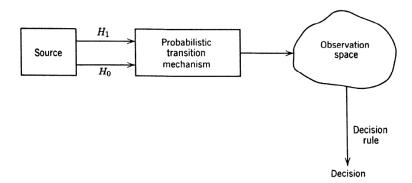

| 3.14 | Diagrama da representação do problema da teoria da decisão [58]              | 34 |

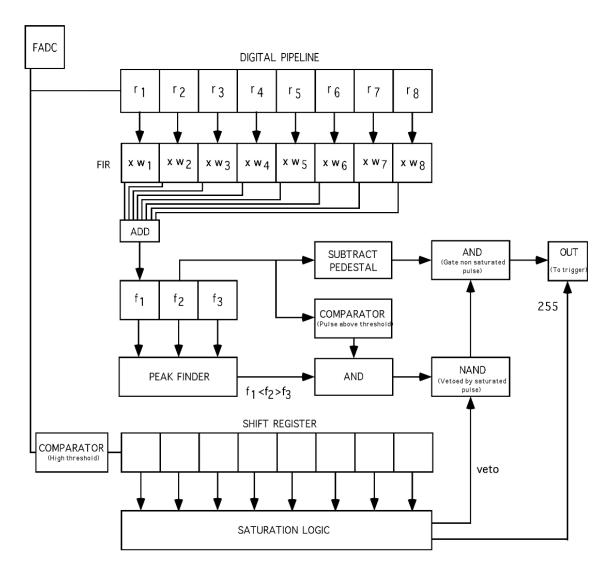

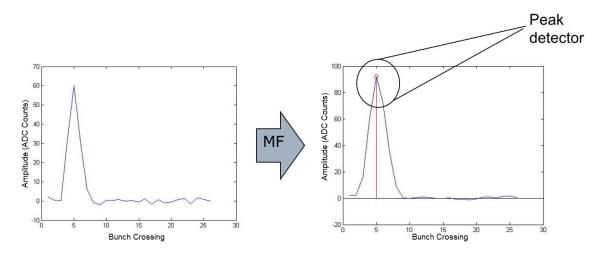

| 3.15 | Diagrama de blocos do sistema de BCID [9]                                    | 36 |

| 3.16 | Representação gráfica da detecção da energia no primeiro nível do            |    |

|      | Trigger na arquitetura atual do TileCal [12]                                 | 36 |

| 3.17 | Representação gráfica do efeito de sobreposição entre sinais adjacen-        |    |

|      | tes [6]                                                                      | 37 |

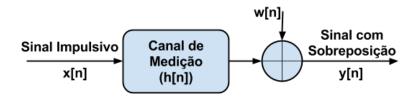

| 3.18 | Diagrama do modelo da sobreposição de sinais no Calorímetro $\ .\ .\ .$      | 38 |

| 3.19 | Diagrama de blocos da filtragem de um sinal digital                          | 39 |

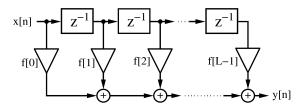

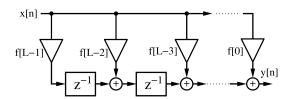

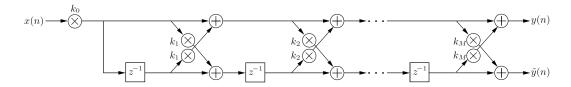

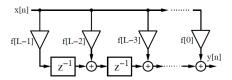

| 3.20 | Representação da Forma Direta do Filtro FIR [60]                             | 40 |

| 3.21 | Representação da Forma Transposta do Filtro FIR [60]                         | 40 |

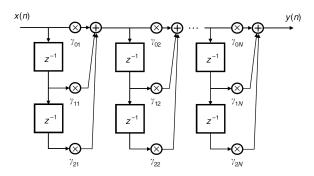

| 3.22 | Representação da Forma em Cascata do Filtro FIR [61]                         | 40 |

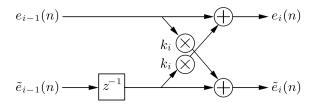

| 3.23 | Representação da Forma Treliça do Filtro FIR [61]                            | 41 |

| 3.24 | Representação do bloco básico utilizado na Forma Treliça [61]                | 41 |

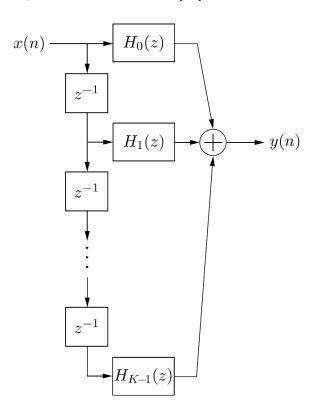

| 3.25 | Representação da Forma Polifásica [61]                                       | 42 |

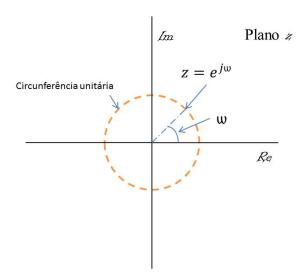

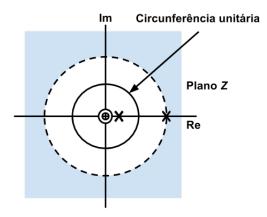

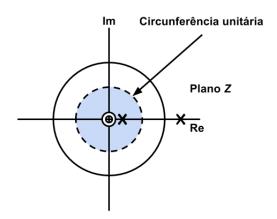

| 3.26 | Representação Gráfica do Plano $Z$ [12]                                      | 44 |

| 3.27 | Representação de duas possíveis RDCs para sistemas com função ra-            |    |

|      | cional                                                                       | 45 |

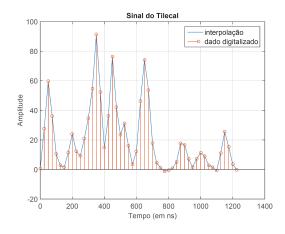

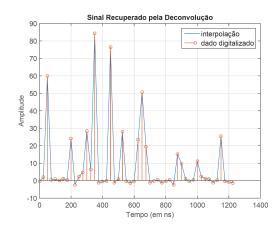

| 3.28 | Exemplo de recuperação do sinal do $\it TileCal$ usando o método deter-      |    |

|      | minístico                                                                    | 47 |

| 3.29 | Representação da lógica do Gradiente Descendente Positivo [12]               | 50 |

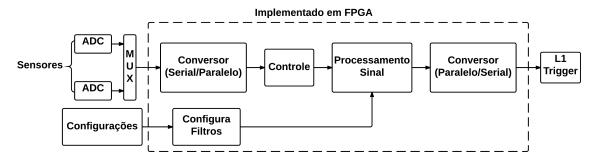

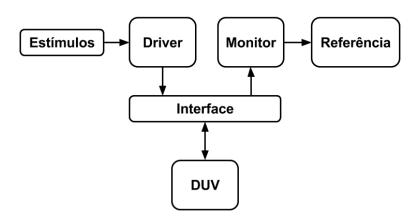

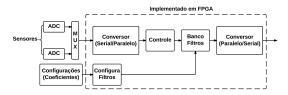

| 4.1  | Arquitetura do Sistema Eletrônico Implementado em FPGA                       | 52 |

| 4.2  | Diagrama do Bloco Configura Filtros                                          | 53 |

| 4.3  | Diagrama do Bloco Conversor Serial/Paralelo                                     | 54   |

|------|---------------------------------------------------------------------------------|------|

| 4.4  | Diagrama do Bloco Conversor Paralelo/Serial                                     | 54   |

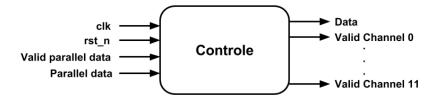

| 4.5  | Diagrama do Bloco Controle                                                      | 54   |

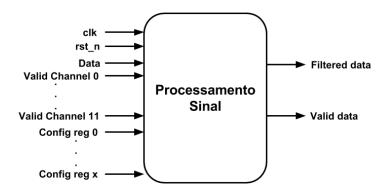

| 4.6  | Diagrama do Bloco Processamento Sinal                                           | 55   |

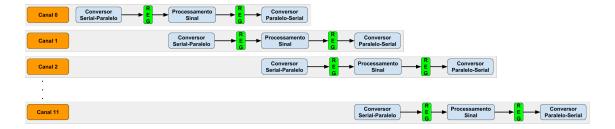

| 4.7  | Diagrama dos Estágios do Paralelismo                                            | 56   |

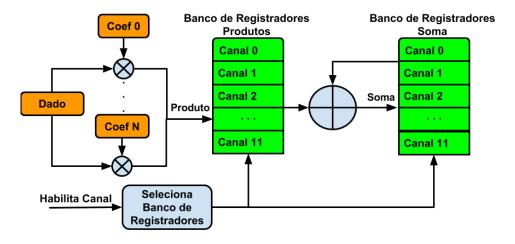

| 4.8  | Diagrama da Implementação em hardware do método determinístico.                 | 57   |

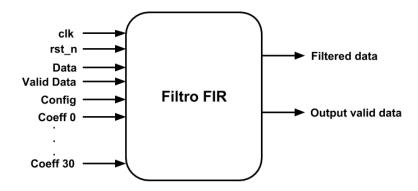

| 4.9  | Diagrama da arquitetura da implementação do filtro FIR                          | 58   |

| 4.10 | Diagrama da Máquina de Estados Finita utilizada para o método                   |      |

|      | iterativo                                                                       | 60   |

| 4.11 | Arquitetura da Verificação Funcional                                            | 62   |

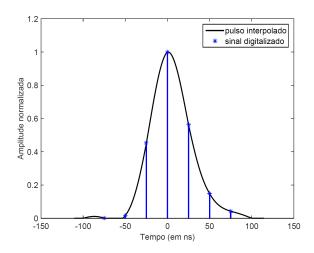

| 5.1  | Representação gráfica do pulso característico do TileCal [12]                   | 65   |

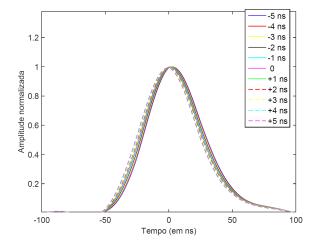

| 5.2  | Representação gráfica de exemplos do pulso característico do $\it TileCal$      |      |

|      | com desvio de fase [12]                                                         | 65   |

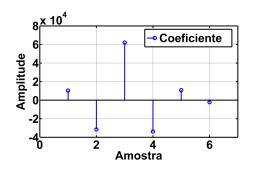

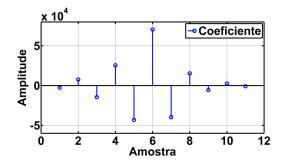

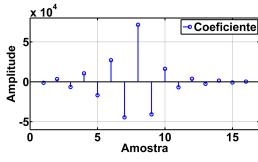

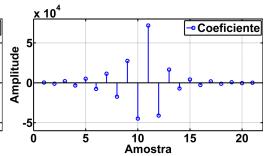

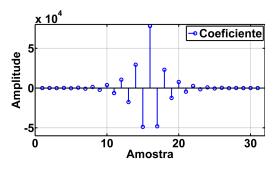

| 5.3  | Representação gráfica dos coeficientes nas diferentes ordens utilizadas         |      |

|      | na simulação                                                                    | 68   |

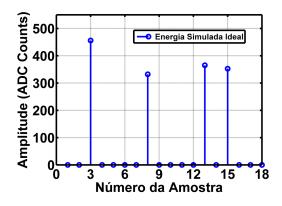

| 5.4  | Representação gráfica de sinais de energia simulados com e sem o                |      |

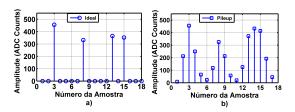

|      | efeito de empilhamento.                                                         | 69   |

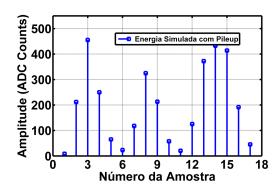

| 5.5  | Representação gráfica da aplicação do filtro com diferentes ordens no           |      |

|      | FPGA                                                                            | 70   |

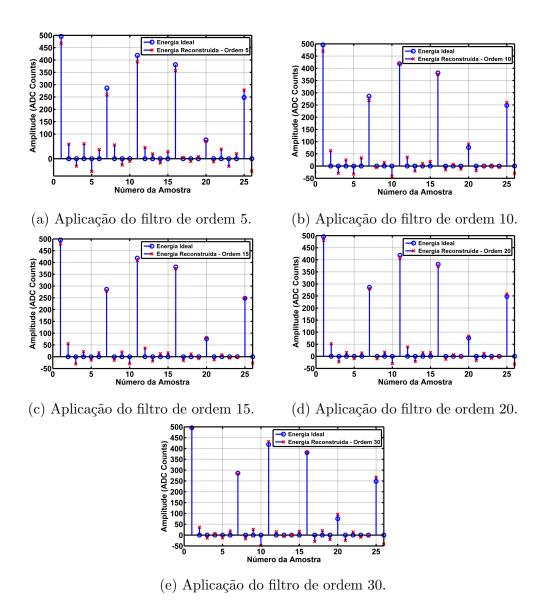

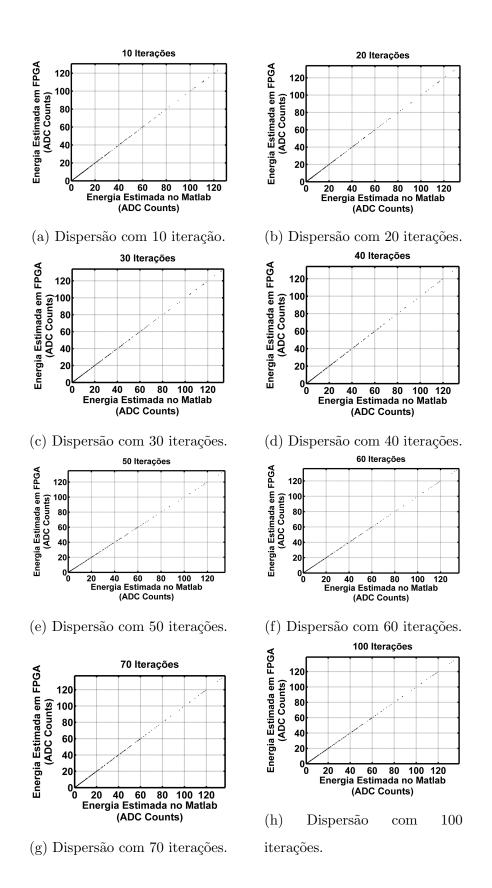

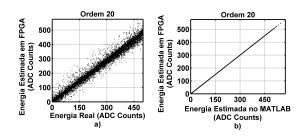

| 5.6  | Gráficos da dispersão entre a energia ideal e a estimada em FPGA.   .           | 71   |

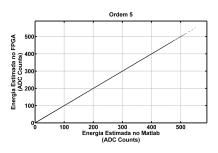

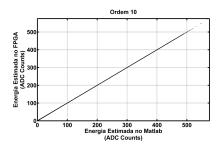

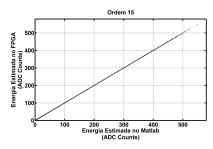

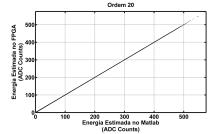

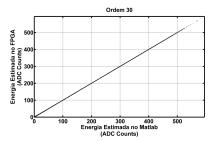

| 5.7  | Gráficos da dispersão entre a energia estimada no FPGA e no MATLAB $^\circledR$ | . 72 |

| 5.8  | Representação gráfica da utilização dos recursos lógicos na imple-              |      |

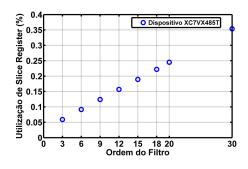

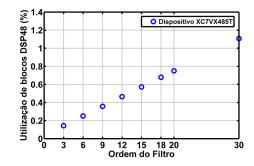

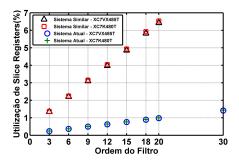

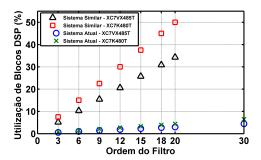

|      | mentação do método determinístico                                               | 74   |

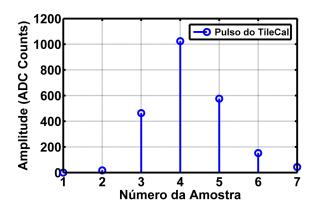

| 5.9  | Representação gráfica do pulso característico do TileCal utilizado na           |      |

|      | simulação do método iterativo                                                   | 76   |

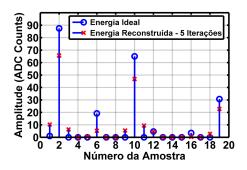

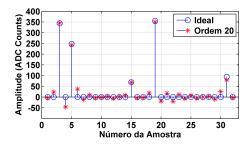

| 5.10 | Representação gráfica do sinal reconstruído com diferentes quantidade           |      |

|      | de iterações                                                                    | 76   |

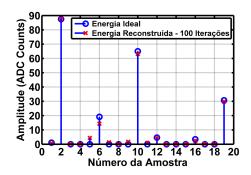

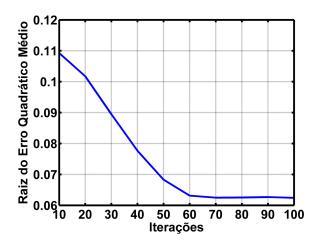

| 5.11 | Representação gráfica da relação entre a raiz quadrada do erro quadrático       |      |

|      | médio e o número de iterações.                                                  | 78   |

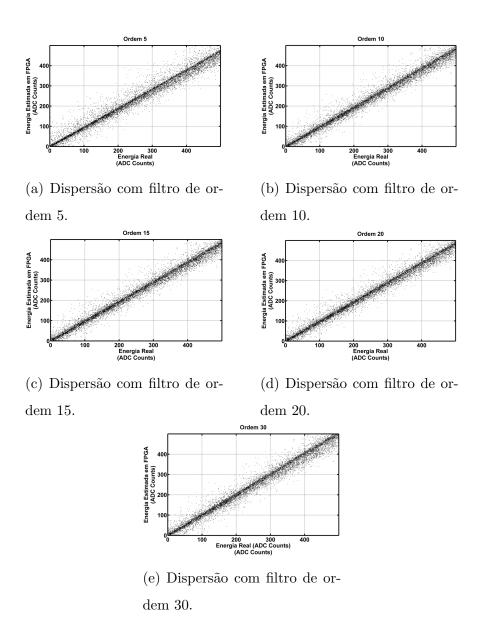

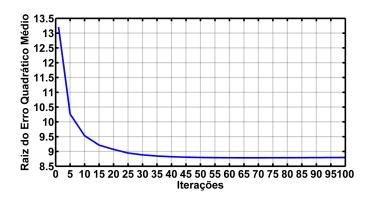

| 5.12 | Gráficos da dispersão entre a energia ideal e a estimada em FPGA                |      |

|      | no método iterativo.                                                            | 79   |

| 5.13 | Representação gráfica da relação entre a raiz quadrada do erro quadrático       |

|------|---------------------------------------------------------------------------------|

|      | médio e o número de iterações considerando o FPGA e o modelo de                 |

|      | referência                                                                      |

| 5.14 | Gráficos da dispersão entre a energia estimada no FPGA e no MATLAB $^\circledR$ |

|      | do método iterativo                                                             |

|      |                                                                                 |

| A.1  | Diagrama do fluxo de projeto digital                                            |

| A.2  | Diagrama conceitual da estrutura de um FPGA [77] 102                            |

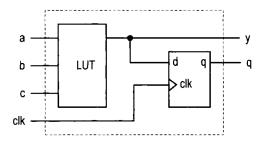

| A.3  | Diagrama conceitual de uma célula lógica [77]                                   |

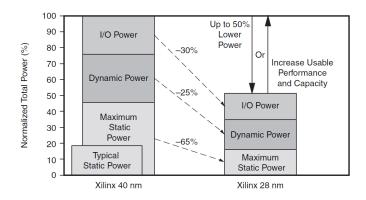

| A.4  | Otimização da família 7 da Xilinx [79]                                          |

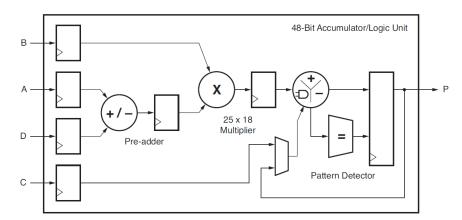

| A.5  | Diagrama das funcionalidades básicas do DSP48E1 [71] 105                        |

| A.6  | Diagrama das funcionalidades básicas do bloco de lógica configurável[81].106    |

# Lista de Tabelas

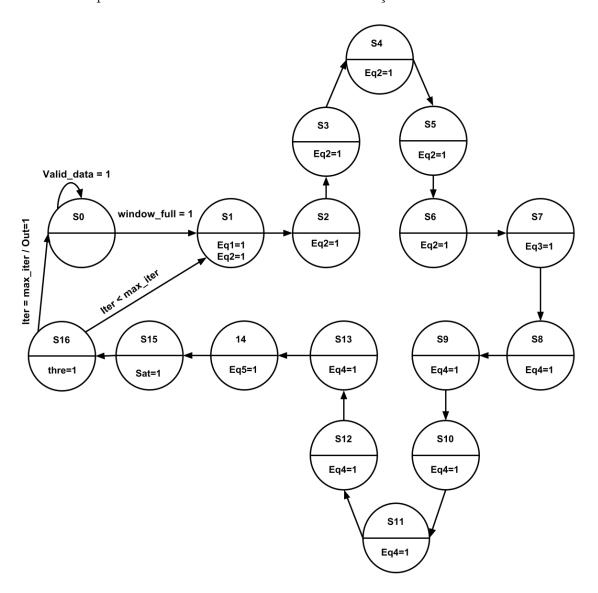

| 4.1 | Transição de Estados e Saídas                                                  | 61  |

|-----|--------------------------------------------------------------------------------|-----|

| 5.1 | Valores do erro dos resultados da simulação FPGA                               | 69  |

| 5.2 | Valores do erro entre os resultados da simulação FPGA e o modelo               |     |

|     | de referência (MATLAB®)                                                        | 72  |

| 5.3 | Relatório de potência na síntese                                               | 74  |

| 5.4 | Valores do erro dos resultados da simulação FPGA no método iterativo.          | 78  |

| 5.5 | Valores do erro entre os resultados da simulação FPGA e o modelo               |     |

|     | de referência (MATLAB®) do método iterativo $\ \ \ldots \ \ \ldots \ \ \ldots$ | 80  |

| 5.6 | Utilização dos recursos lógicos do FPGA no método iterativo                    | 86  |

| 5.7 | Relatório de potência na síntese do método iterativo                           | 86  |

| 5.8 | Comparação dos resultados obtidos com a implementação dos métodos.             | 86  |

| A.1 | Características dos dispositivos da família Virtex-7                           | .04 |

## Lista de Abreviaturas

| ADC  | Conversor Analógico Digital, do inglês Analog Digital Converter, p. 27                                       |

|------|--------------------------------------------------------------------------------------------------------------|

| ASIC | Circuito Integrado de Aplicação Específica, do inglês <i>Application Specific Integrated Circuit</i> , p. 31 |

| BCID | Identificação do Bunch Crossing, do inglês Bunch Crossing IDentification, p. 32                              |

| CERN | Centro Europeu para Pesquisas Nucleares, do francês Conseil Européen pour la Recherche Nucléaire, p. 1       |

| CI   | Circuito Integrado, p. 98                                                                                    |

| CLB  | Bloco de lógica configurável, do inglês Configurable Logic Block, p. 105                                     |

| DMU  | Unidade de gerenciamento de informações, do inglês Data Management Unit, p. 26                               |

| DSP  | Processador Digital de Sinais, do inglês Digital Signal Processor, p. 39                                     |

| FIR  | Resposta ao Impulso Finita, do inglês $Finite\ Impulse\ Response,$ p. 3                                      |

| FSM  | Máquina de Estados Finita, do inglês <i>Finite State Machine</i> , p. 60                                     |

| HDL  | Linguagem de Descrição de Hardware, do inglês <i>Hardware Description Language</i> , p. 99                   |

| HEP  | Física de Altas Energias, do inglês <i>High-Energy Physics</i> , p. 1                                  |

|------|--------------------------------------------------------------------------------------------------------|

| IIR  | Resposta ao Impulso Infinita, do inglês $\it Infinite\ Impulse\ Response,\ p.\ 39$                     |

| LHC  | Grande Colisor de Hádrons, do inglês ${\it Large~Hadron~Collider},$ p. 1                               |

| LUT  | Look-Up Table, p. 101                                                                                  |

| PMT  | Tubos Fotomultiplicadores, do inglês <i>Photomultipier Tubes</i> , p. 19                               |

| QSFP | Quad Small Form-factor Pluggable, p. 31                                                                |

| RDC  | Região de Convergência, p. 44                                                                          |

| ROD  | Drivers de Saída, do inglês Read-out Driver, p. 28                                                     |

| RTL  | Register-Transfer Level, p. 62                                                                         |

| SNR  | Relação sinal-ruído, do inglês Signal-to-Noise Ratio, p. 23                                            |

| VHDL | Linguaguem de Descrição de Hardware VHSIC, do inglês $\it VH-SIC$ Hardware Description Language, p. 99 |

## Capítulo 1

## Introdução

A Física de Partículas (em alguns casos chamada de Física de Altas Energias ou *High-Energy Physics* - HEP) é a área da ciência responsável por estudar a composição da matéria, em outras palavras, estuda as partículas subatômicas e suas formas de interação.

Desde a Grécia antiga já se desenvolviam teorias acerca dos elementos constituintes da matéria [1]. Desde então, diversos grupos de pesquisadores no mundo inteiro, vem desenvolvendo experimentos a fim de explorar questões relacionadas às partículas elementares. Mais recentemente, os experimentos de física de altas energias vêm sendo projetados para observar e caracterizar as partículas de interesse, que podem ser geradas por fontes naturais (ex. raios cósmicos) ou artificiais (aceleradores de partículas) [2]. Esses experimentos têm como objetivo comprovar os modelos teóricos previamente elaborados pelos pesquisadores e também fundamentar o desenvolvimento de novos modelos.

Nesse sentido, o Centro Europeu para Pesquisas Nucleares (CERN, da abreviação do nome em francês Conseil Européen pour la Recherche Nucléaire), um dos centros de pesquisa de referência em Física de Partículas, projetou e construiu o Grande Colisor de Hádrons (LHC, do inglês Large Hadron Collider) [3], sendo este o maior acelerador de partículas atualmente em operação. Ao longo da trajetória do LHC existem 6 detectores, cada um responsável por identificar características específicas das partículas. O ATLAS [4] é um desses equipamentos, caracterizado como de propósito geral, sendo constituído de alguns sub-detectores.

As informações dos sensores do ATLAS são processadas por sistemas eletrônicos

e computacionais dedicados, e, por fim, armazenadas em mídia permanente para análises posteriores [4]. Com o intuito de avançar nas pesquisas, o LHC está em processo de atualização para aumentar a quantidade de interações por  $cm^2$  por segundo (que se traduz no aumento de luminosidade) e também a energia de colisões [5]. Consequentemente, essa atualização acarretará uma taxa de eventos maior a serem detectados e processados. Considerando o ambiente de funcionamento do calorímetro, que é o sub-detector do ATLAS dedicado à medição de energia e à estimação da posição da interação, o aumento da ocorrência de eventos provoca sobreposição da informação de eventos subsequentes medidos, fenômeno conhecido como pileup, ou empilhamento [6, 5].

O problema da sobreposição está associado à alta taxa de ocorrência dos eventos e ao tempo de resposta dos equipamentos responsáveis pela detecção dos mesmos. Além do ambiente do ATLAS, esse fenômeno ocorre em outras áreas que possuem sistemas eletrônicos com alta taxa de geração de eventos. Aparelhos biomédicos, por exemplo, são equipamentos que exigem alta precisão em seus sistemas de aquisição, como é o caso dos tomógrafos por emissão de pósitrons (PET), que exigem altas resoluções no processamento das imagens [7]. Em outra aplicação, na espectroscopia Gama, o efeito do pileup afeta a identificação das fontes radioativas desconhecidas, pois provoca a distorção do histograma das energias de fótons. Nesse cenário, a sobreposição ocorre devido a alta atividade da fonte radioativa associada à limitada resolução dos detectores [8]. Outra área que merece destaque nesse cenário são os sistemas de comunicações ópticas, nos quais a sobreposição pode modificar a informação transmitida, afetando diretamente sua eficiência.

No atual sistema eletrônico em operação no ATLAS, o pulso gerado em cada célula do detector é digitalizado através de um conversor analógico-digital e enviado para um sistema eletrônico responsável por aplicar técnicas de processamento de sinais para extrair as informações de interesse. A atual técnica de estimação de energia utilizada no primeiro nível de seleção do ATLAS é o Filtro Casado, utilizado para detectar o pulso do calorímetro [9, 10]. Com o aumento da luminosidade, em função do processo de atualização do LHC, e a inerente alta taxa de ocorrência de eventos, a eletrônica e as técnicas de estimação atualmente utilizadas tornam-se ineficientes no processo de identificar os eventos de interesse. Por isso, os pesquisadores

que compõem a colaboração do ATLAS vem desenvolvendo alterações no sistema eletrônico do detector com o objetivo de atender aos requisitos das novas fases de atualização do LHC.

Nesse cenário, torna-se necessário desenvolver um sistema digital capaz de recuperar a informação dos sinais de energia afetados pelo *pileup* no primeiro nível de seleção de eventos. Dessa forma, este trabalho apresenta uma solução que atende aos requisitos eletrônicos da atualização do ATLAS. A solução proposta consiste no desenvolvimento de um sistema digital em *Field Programmable Gate Array* (FPGA) que implementa técnicas de filtragem para reduzir os efeitos do empilhamento dos eventos detectados.

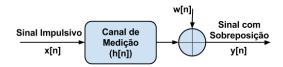

A partir da consideração do calorímetro como um sistema linear [11], o processo de sobreposição das informações foi interpretado como uma convolução do sistema de calorimetria com os sinais de interesse das colisões. Consequentemente, as técnicas de estimação das informações propostas baseiam-se na filtragem inversa, ou deconvolução. Dentre as soluções apontadas em [12], nesse trabalho foram implementadas duas abordagens: uma determinística e outra iterativa. A primeira baseou-se em filtro de resposta ao impulso finita (FIR, do inglês Finite Impulse Response) [13], que foi projetado para aproximar a função inversa da resposta em frequência do canal de medição e tende a utilizar poucos recursos lógicos do FPGA. A segunda é baseada na técnica de convergência de Van Cittert [14], através do Gradiente Descendente Positivo, que prioriza as amplitudes positivas, zerando as energias negativas a cada iteração. Esta solução utiliza mais recursos lógicos do FPGA devido a maior complexidade em suas operações, mas em contrapartida tende a ter melhor eficiência na reconstrução do sinal.

#### 1.1 Objetivos

Este trabalho tem como objetivo desenvolver uma solução em FPGA capaz de reduzir os efeitos de sobreposição de eventos (pileup) no calorímetro do ATLAS. Para isso, foram implementadas diferentes técnicas de estimação de energia em hardware capazes de recompor o sinal original das amostras afetadas pela sobreposição. O desenvolvimento dessa solução levou em consideração os requisitos de funciona-

mento da eletrônica embarcada no *TileCal*, considerando o tempo de processamento, ocupação de recursos lógicos do FPGA e análise do consumo de potência. Vale destacar que a contribuição deste trabalho está na implementação da solução em *hardware*, com a proposta de um sistema adequado a ser embarcado na eletrônica do *TileCal*, e baseou-se nos projetos e avaliações de filtros realizados em [12].

Como objetivos específicos desse projeto, cita-se:

- 1. Compreender o funcionamento do sistema de calorímetro do ATLAS.

- 2. Compreender o funcionamento do sistema de aquisição e seleção das informações.

- Compreender o funcionamento de diferentes abordagens de projeto de filtros digitais.

- 4. Descrever o *hardware* de forma a atender os requisitos de funcionamento do sistema eletrônico do ATLAS.

- Desenvolver a verificação funcional a fim de garantir o funcionamento do hardware.

- 6. Avaliar o desempenho na estimação do sinal de energia das técnicas implementadas.

- 7. Avaliar os resultados obtidos com a síntese em FPGA das soluções propostas.

### 1.2 Resultados em Publicações

Os resultados obtidos com essa pesquisa foram apresentados e publicados no Congresso Brasileiro de Automática (CBA2016) 2016, Encontro de Física 2016 e Encontro Nacional de Física de Partículas e Campos 2015. Abaixo seguem os resumos dos trabalhos apresentados, sendo que o artigo completo do CBA 2016 está anexado.

LUZ, I. A. S., SIMAS FILHO, E. F., FARIAS, P. C. M. A., BECK, M., AN-DRADE FILHO, L. M., DUARTE, J. P. B. S., de Seixas, José Manoel. Sistema para Redução da Sobreposição de Sinais em Calorimetria de Altas Energias em Operação com Alta Taxa de Eventos. Congresso Brasileiro de Automática CBA, 2016, Vitória. Anais do CBA 2016.

Resumo: Sistemas que funcionam em tempo real possuem diversos desafios em termos de desempenho que precisam ser atendidos em seu projeto, tais como: tempo de processamento, consumo de potência, área utilizada, entre outros. Dessa forma, para atender a essas restrições, esses projetos precisam ser desenvolvidos em hardware dedicado. Um problema que ocorre nos sistemas de processamento digital de sinais é a sobreposição entre informações provenientes de eventos subsequentes. Essa distorção do sinal é chamada empilhamento (do inglês pileup) e ocorre com muita frequência no âmbito dos detectores de partículas. Esse trabalho propõe um circuito eletrônico dedicado implementado em um sistema digital reconfigurável de alto desempenho para redução do empilhamento nos sinais medidos em um calorímetro. Para isso, são utilizados filtros digitais de resposta ao impulso finita implementados em paralelo. Cada filtro é uma aproximação da inversa da resposta ao impulso do canal de medição, realizando a desconvolução dos sinais medidos. Os resultados obtidos mostram a eficiência da técnica proposta e a adequação aos requisitos de tempo de processamento da aplicação.

DUARTE, J. P. B. S., HUFNAGEL, M., ANDRADE FILHO, L. M., LUZ, I. A. S., SIMAS FILHO, E. F., SEIXAS, J. M. Estimação de Energia Online para o Tilecal: comparação entre os métodos linear e não-linear. Encontro de Física, 2016, Natal. Anais do Encontro de Física 2016.

Resumo: A estimação de energia em calorímetros operando em ambientes de alta taxa de eventos pode sofrer com a sobreposição de informação devido à sensibilização do sistema de medição por eventos anteriores, esse fenômeno é conhecido como empilhamento de sinais (ou pileup). No calorímetro hadrônico do detector ATLAS (Tile calorimeter ou Tilecal), a ocorrência desse fenômeno se intensificará à medida que a luminosidade das colisões do LHC aumentar. O atual sistema de processamento de sinais do detector não está preparado para lidar com o pileup, o que pode ocasionar baixa eficiente para a detecção (trigger) de eventos. Para lidar com esse problema um novo sistema eletrônico (readout driver) baseado em field-programmable gate arrays (FPGA) está sendo projetado, permitindo a estimação de energia online antes do primeiro nível de trigger. Neste trabalho é proposta uma cadeia de processamento de sinais para ser embarcada nos readout drivers do Tilecal visando a redução do pileup. Para isso, está sendo utilizada a técnica da

de-convolução através de métodos lineares e não-lineares. A metodologia linear se baseia na aplicação de filtros digitais que aproximam o modelo inverso do canal de medição. Para modelar, também, não-linearidades existentes no problema, uma rede neural foi utilizada. Resultados com dados simulados possibilitam a comparação entre os métodos propostos considerando aspectos como a precisão na estimação e a complexidade computacional.

LUZ, I. A. S., BECK, M., SIMAS FILHO, E. F., FARIAS, P. C. M. A., AN-DRADE FILHO, L. M., SEIXAS, J. M. Implementação em FPGA do Sistema Digital para redução do Ruído de empilhamento dos Sinais do Calorímetro Tilecal do ATLAS. Encontro Nacional de Física de Partículas e Campos, 2015, Caxambu. Anais do ENFPC 2015.

Resumo: O LHC está em processo de atualização, de modo a aumentar sua luminosidade e energia de colisões, acarretando numa maior taxa de eventos para serem detectados e processados. O aumento da ocorrência de eventos pode provocar a sobreposição da informação de eventos subsequentes (fenômeno conhecido como empilhamento ou pileup). Este trabalho apresenta a implementação do sistema digital de processamento de sinais para reduzir os efeitos do ruído de pileup no principal calorímetro hadrônico do ATLAS (o TileCal). Um conjunto de filtros digitais foi implementado em FPGA de alta performance para garantir o cumprimento dos requisitos de tempo de processamento das amostras. Os filtros utilizados são do tipo Resposta ao Impulso Finita (FIR Finite Impulse Response), com implementação na forma direta ou transposta. O projeto dos filtros foi baseado na técnica da desconvolução da resposta do calorímetro. Para estimação da inversa da função de transferência do canal de medição foi utilizado um estimador ótimo (no sentido da minimização do erro quadrático médio). O sistema digital projetado é flexível e pode utilizar filtros de diferentes ordens, variando-se também a resolução de quantização dos coeficientes. Para atender aos requisitos de tempo de processamento, foram utilizadas técnicas de pipeline e de múltiplos domínios de clock no projeto do hardware. Para o desenvolvimento do trabalho utilizou-se o Verilog como linguagem de descrição de hardware (HDL Hardware Description Language) e o System Verilog como linguagem para verificação do sistema. O FPGA utilizado para o projeto é da família Kintex-7, da Xilinx. Utilizando-se um conjunto de dados simulados observou-se que o ruído de empilhamento é consideravelmente reduzido com a utilização dos filtros projetados. Um estudo a respeito do tempo de resposta do sistema proposto será apresentado.

#### 1.3 Organização da Dissertação

No Capítulo 2 é contextualizada a Física de partículas através do seu histórico e alguns conceitos fundamentais para o entendimento da aplicação desse projeto. Além desse ponto, nesse capítulo é apresentado o LHC e seus subsistemas, com ênfase no detector ATLAS.

O Capítulo 3 aborda a atualização do LHC e seus efeitos no atual sistema eletrônico. Pontua, também, a atualização da eletrônica do *TileCal* para suportar o aumento da luminosidade e os métodos de estimação propostos para a recuperação dos sinais de energia.

O Capítulo 4 apresenta o sistema em FPGA desenvolvido nesse trabalho, descrevendo a arquitetura para ambas as soluções propostas e também a técnica de verificação funcional adotada. No Capítulo 5 são apresentados os resultados obtidos com a abordagem determinística e iterativa.

No Capítulo 6 são apresentadas as conclusões deste trabalho. O Apêndice A apresenta uma breve descrição do desenvolvimento de um projeto de *hardware* digital, expondo as características do dispositivo FPGA utilizado nesse trabalho. Por fim, no final do documento foi anexado o texto completo do artigo apresentado no CBA 2016.

## Capítulo 2

# Introdução à Física de Partículas e ao Acelerador LHC

#### 2.1 Histórico da Física de Partículas

Desde o tempo dos filósofos gregos, pesquisa-se a respeito da composição da matéria, com a proposição de teorias que serviram de base para experimentos futuros. Na Grécia antiga, em torno de 600 a 400 a.C., acreditava-se que os elementos fundamentais eram fogo, água, terra e ar. Somente em 400 a.C, Leucipo e Demócrito, filósofos gregos, disseminaram a teoria atômica, ou do atomismo, a qual afirma que toda matéria é formada por elementos indivisíveis, por átomos [1]. Durante muito tempo, não foram realizadas pesquisas acerca desse tema, até que, em 1808, um pesquisador Inglês, chamado John Dalton, baseando-se na teoria de Leucipo e Demócrito, publicou um livro sobre a teoria atômica [15]. Nesse livro, Dalton definiu as características do primeiro modelo atômico: Toda matéria é composta por minúsculas partículas chamadas átomos; Todos os átomos de um mesmo elemento são idênticos; entre outras. Nesse estudo, John Dalton também definiu a lei das proporções definidas, afirmando que: "quando dois corpos A e B se combinam para formar um corpo C, as massas de A e de B necessárias para a reação estão numa razão definida" [15].

Além de Dalton, outros pesquisadores também propuseram modelos atômicos. Em 1897 o pesquisador J. J. Thomson abriu as portas para os estudos da Física de Partículas do século XX através do descobrimento do elétron. Essa descoberta

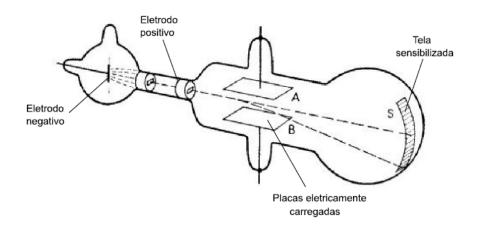

foi realizada através da análise do comportamento dos raios catódicos na presença de forças elétricas e magnéticas. Na Figura 2.1 apresenta-se o esquema do aparelho utilizado nesse experimento [15].

Figura 2.1: Esquema do aparelho usado para medir a deflexão elétrica e magnética dos raios catódicos [15].

A partir dessa descoberta, em 1904 Thomson apresenta um segundo modelo atômico. Nesse modelo, considera-se que o átomo neutro era constituído de uma esfera carregada positivamente e que possuía, também, elétrons. Esse modelo ficou popularmente conhecido como "Pudim de Ameixa", do inglês "Plum Pudding" [15].

Em 1911, Rutherford apresentou um terceiro modelo atômico, que acabou substituindo o modelo de Thomson. A partir das conclusões do segundo modelo atômico, e realizando experimentos com feixes de partículas  $\alpha$  sobre uma folha fina de ouro, Rutherford observou um comportamento diferente ao que havia sido definido por Thomson. Nesse novo modelo, o átomo é definido como consistindo de um núcleo carregado positivamente envolto por um sistema de elétrons, mantidos próximos um dos outros [15]. No ano de 1913, o pesquisador Niels Bohr aperfeiçoou o modelo de Rutherford e definiu que os elétrons circulam em torno do núcleo numa orbita de acordo a um nível de energia do átomo.

A partir do terceiro modelo atômico, em 1919, Rutherford realizou um experimento onde partículas  $\alpha$  colidiam com átomos de nitrogênio. A partir desse experimento, foi descoberta mais uma partícula elementar, o Próton [15].

Após a descoberta do próton, em 1923 Arthur Compton confirmou a existência da partícula chamada de Fóton [15], através de um experimento onde foi realizado

o espalhamento elástico de raios X em elétrons. Essa nova partícula pode ser interpretada como luz, sendo assim, é uma das mais notáveis partículas elementares, visto que está presente no dia-a-dia das pessoas.

Em 1932, Sir James Chadwick descobriu o nêutron. Essa partícula está diretamente relacionada às descobertas que foram realizadas durante a última década do século XIX [15]. A descoberta do nêutron foi estimulada a partir de um questionamento sobre o que mantém as cargas positivas confinadas em uma região espacial tão minúscula como a do núcleo atômico. Dessa forma, a partir de pesquisas da transmutação dos elementos com feixe de partículas  $\alpha$ , repetindo o experimento com uma variedade de gases, pode-se, então, atestar a existência e também definir a massa do nêutron.

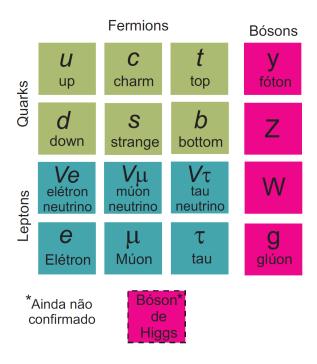

A partir das descobertas de elétrons, prótons e nêutrons, acreditava-se que esses eram os elementos fundamentais da constituição da matéria. Sendo os átomos constituídos pelos prótons e nêutrons como estrutura molecular e os elétrons como orbitais [15]. Contudo, ao longo dos anos novos estudos e experimentos foram realizados e constatou-se que os léptons e quarks são os verdadeiros elementos fundamentais, pois não possuem estrutura interna [16, 17]. Nesse sentido, foi constatado que os prótons e nêutrons são formados por quarks e que os elétrons são um tipo de lépton. Finalmente, chegou-se ao Modelo Padrão, o qual define as partículas quarks e léptons como constituintes fundamentais da matéria [16, 17].

Existem seis espécies de quarks conhecidos, são eles: u (up), d (down), c (charm), s (strange), b (bottom) e t (top) [18]. Cada uma dessas espécies pode assumir três cores: vermelho, verde e azul. Além disso, cada um possui sua antipartícula. Dessa forma, existem trinta e seis diferentes tipos de quarks [19]. Assim como os quarks, também existem seis tipos de léptons. São eles: elétron, múon, tau, neutrino do elétron, neutrino do múon e neutrino do tau [16]. Sendo que, cada um também possui sua antipartícula, resultando, assim, em um total de doze léptons.

A descoberta dos quarks ocorreu a partir das pesquisas acerca da constituição dos hádrons. Em 1964, os pesquisadores Gell-Mann e Zweig propuseram que todos os hádrons eram formados por elementos chamados quarks [20], sendo que suas partículas interagiam com as outras através de interação forte [18]. Os hádrons são partículas que possuem estrutura interna e são classificadas como: bárions,

quando formados por três quarks ou três antipartícula de quarks; e mesóns, quando constituído por um quark e uma antipartícula de quark [21]. Dessa forma, seguindo esse modelo, os prótons são formados por dois quarks do tipo u e um do tipo d (uud) e os nêutrons por dois do tipo d e um do tipo u (udd) [20].

Apesar do quark compor a maior parte da massa observada no universo, os léptons não são compostos de quarks. Essas partículas não participam de interações fortes, mas sim das interações eletromagnéticas e fracas. As massas dos léptons são menores do que as dos quarks, sendo que os neutrinos caracterizam-se por serem os mais leves [18].

Além do conhecimento sobre as partículas, para se ter noção da constituição da matéria, torna-se necessário, também, o conhecimento acerca das interações entre elas. Existem quatro tipos de interações fundamentais: eletromagnética, gravitacional, nuclear forte e nuclear fraca. Cada uma delas está relacionada a uma propriedade fundamental: carga elétrica, massa, cor e carga fraca, respectivamente [17]. A primeira pode ser exemplificada como sendo a interação entre um elétron e um núcleo atômico; A segunda regula o movimento dos corpos celestes, ocorre entre todas as partículas; a terceira ocorre entre os quarks; a quarta, e última, ocorre, por exemplo, quando um nêutron decai para um próton, devido a emissão de um elétron ou neutrino [19].

O modelo padrão define, ainda, as partículas mediadoras, ou virtuais, responsáveis pela transmissão da mensagem da força entre as partículas interagentes [17]. Esses elementos são chamados de virtuais pois não possuem massa, tem apenas energia. Cada interação possui uma determinada partícula mediadora: na eletromagnética temos os fótons, na forte os glúons, W e Z na interação fraca e os grávitons na gravitacional [17].

Na Figura 2.2 é apresentado um esquema resumido do modelo padrão, considerando tanto as partículas elementares como as interações fundamentais.

#### 2.2 O LHC

No cenário de estudo da física de partículas elementares, o acelerador de partículas apresenta-se como um equipamento fundamental para as pesquisas. Essa máquina

Figura 2.2: Diagrama do modelo padrão [22].

utiliza fontes de partículas de baixa energia e são responsáveis por aumentar a energia das partículas estáveis e carregadas eletricamente [22]. Os aceleradores, quanto às características construtivas, podem ser classificados como de alvo fixo ou colisionadores de feixes. Em relação ao percurso do feixe, podem ser classificados como lineares ou circulares [23]. As pesquisas envolvendo aceleradores de partículas normalmente requerem cooperação entre diversos pesquisadores de várias instituições do mundo, tornando-se experimentos de grandes proporções.

Os experimentos envolvendo aceleradores de partículas são compostos de diversos equipamentos, dentre eles os detectores de partículas. Os detectores precisam ter alta precisão para que as partículas detectadas possam ser adequadamente estudadas [23].

Para alcançar a precisão necessária nos experimentos, foram desenvolvidos diferentes tipos de detectores, sendo cada um específico para identificar determinadas características das partículas. São alguns exemplos: Detector a gás, responsável por detectar a ionização produzida pela passagem de uma partícula eletricamente carregada por um determinado gás; Contador de cintilação, responsável por identificar a perda de energia que é convertida em luz e convertê-la em impulso elétrico; Calorímetro, usado para medir a energia e a posição da partícula através da absorção total de sua energia [23].

Existem grandes laboratórios que realizam pesquisas na área da física de partículas, dentre eles destacam-se: CERN [24], DESY [25], KEK [26], Fermilab [27], SLAC [28] e Brookhaven [29].

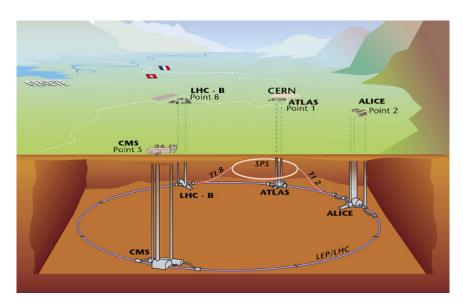

O CERN (Centro Europeu para Pesquisas Nucleares) apresenta-se como um dos maiores centros de pesquisas na área de física de partículas. Criado em 1954, localizado em Genebra, na fronteira Franco-Suíça, esse centro de pesquisas vem desenvolvendo experimentos fundamentais no que diz respeito à descoberta dos constituintes da matéria [30]. No CERN foi projetado e desenvolvido o LHC, o maior acelerador de partículas já construído, tendo suas atividades iniciadas em 2008 [3, 31]. Esse acelerador tem a capacidade de gerar energia de colisão de até 14 TeV<sup>1</sup> e possui um percurso circular de aproximadamente 27 km de comprimento e 100 m de profundidade [22]. Na Figura 2.3 é mostrado o túnel do LHC.

Figura 2.3: Fotografia do túnel do LHC [32].

O LHC tem como objetivo provocar colisões próton-próton a uma velocidade igual a 99,9999% da velocidade da luz, para tentar recriar o ambiente frações de segundos após o big bang [32]. As colisões próton-próton tem uma luminosidade projetada de  $10^{34}cm^{-2}s^{-1}$  enquanto que as colisões de íons pesados tem picos de luminosidade acima de  $10^{27}cm^{-2}s^{-1}$  [33].

A luminosidade gerada nesse experimento é definida pela equação 2.1, onde n representa o número de feixes de partículas,  $N_1$  e  $N_2$  o número de partículas por

<sup>&</sup>lt;sup>1</sup>O Elétron-volt é uma unidade de medida de energia que representa a quantidade de energia cinética de uma partícula. TeV representa Tera Elétron-volt e corresponde a 10<sup>12</sup> elétrons-volt.

feixe, A a área da seção transversal do feixe e f a frequência de colisão.

$$L = n \frac{N_1 N_2}{A} f \tag{2.1}$$

A frequência de colisões nesse acelerador é de 40 MHz, sendo que, a cada colisão espera-se que aconteçam 25 choques protón-próton, dessa forma, a taxa de interações será da ordem de 1 GHz [22].

O LHC é composto por 6 detectores, e estes tem a função de selecionar, a partir de um grande conjunto de eventos, aqueles de real interesse. Os detectores do LHC são: ATLAS [4], ALICE [34], CMS [35], LHCb [36], LHCf [37] e TOTEM [38]. Na Figura 2.4 é ilustrada a distribuição física dos quatro maiores detectores ao longo do percurso do LHC.

Figura 2.4: Ilustração da localização dos quatro maiores detectores do LHC ao longo do percurso do acelerador [22].

#### 2.3 O Detector ATLAS

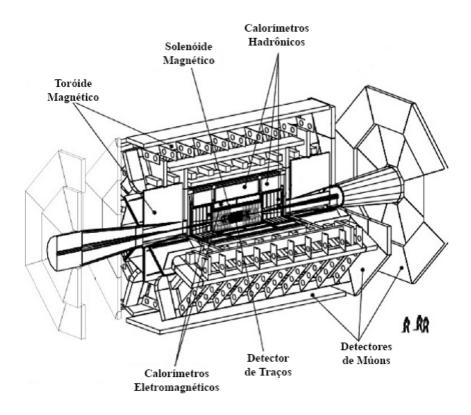

O ATLAS é um detector de propósito geral com formato cilíndrico e capacidade de cobrir um ângulo sólido próximo a  $4\pi$  ao redor da região de colisão [22]. Tem como função detectar os resultados das colisões próton-próton (pp) [32] e pode ser considerado um detector de camadas, pois é composto por sub-detectores. Detector de Camadas é a definição atribuída para equipamentos que precisam extrair

o máximo de informações das partículas com alta precisão. Dessa forma, têm a necessidade de abrigar sistemas específicos para cada característica que se deseja identificar (energia, carga elétrica, momento, etc.).

Dentre as características do detector ATLAS, destaca-se: sistema de calorimetria eletromagnética para medição e identificação de elétrons e fótons com alta performance; sistema de calorimetria hadrônica com total cobertura para medição precisa de energia transversa; alta precisão na medição do momento de múons; alta eficiência no sistema de medição e seleção das partículas, entre outras [39].

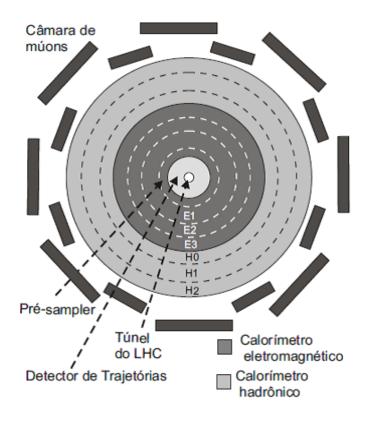

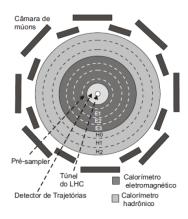

O ATLAS tem aproximadamente 44 metros de comprimento, 25 metros de altura e 7.000 toneladas, sendo assim o maior detector de propósito geral do LHC. Na Figura 2.5 é ilustrada a composição do ATLAS. Dentre os sub-detectores ilustrados na Figura 2.5, os principais são: detector de traços, detector de múons, calorímetro eletromagnético e o calorímetro hadrônico.

Figura 2.5: Esquemático dos detectores do ATLAS [22].

O detector de traços é responsável pela identificação do momento e do vértice das partículas carregadas geradas a cada colisão [4, 40]. Devido à alta frequência de ocorrência dos eventos, para garantir a medição com a alta precisão requerida, foi dividido em três sub-sistemas, dois utilizando semicondutores com a tecnologia

planar e outro uma câmara de tração preenchida com gás, também conhecida como detector gasoso [40, 41]. Os calorímetros têm a função de medir a energia das partículas e a posição de interação no detector [22, 42]. Por fim, o detector de múons contém o sistema de detecção para essas partículas [39, 43], que interagem pouco com o restante do detector.

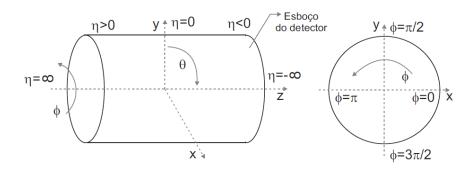

Na Figura 2.6 é apresentado o sistema de coordenadas do ATLAS. Os feixes das partículas seguem o eixo z. Os eixos x e y formam um plano transversal à direção dos feixes de partículas. O ângulo azimutal  $\phi$  é obtido através da equação 2.2 [22]. A direção de projeção das partículas após a colisão é representada por  $\eta$ , que é chamada de pseudo-rapidez e definida na equação 2.3 [22].

Figura 2.6: Eixo de coordenadas do ATLAS [22].

$$\phi = \arctan(\frac{\mathbf{x}}{\mathbf{y}}) \tag{2.2}$$

$$\eta = -\ln\tan(\frac{\theta}{2})\tag{2.3}$$

#### 2.3.1 A Calorimetria do ATLAS

A calorimetria é uma área da física que trata da troca de energia entre elementos. Inicialmente, os estudos nesse campo estavam voltados para fenômenos relacionados aos raios cósmicos. Após aperfeiçoamentos, a calorimetria passou a ser utilizada nos experimentos da física de partículas baseados em aceleradores [44].

Calorímetros [11] são dispositivos utilizados para medir a energia das partículas, como elétrons, próton e hadróns [44]. À medida que interagem com o material que compõe o calorímetro, as partículas vão perdendo energia (e consequentemente, velocidade) e ao final são totalmente absorvidas, sendo transformadas em energia

mensurável pelo sistema eletrônico de medição. Esses equipamentos são utilizados em detectores e precisam ter alta precisão, para, assim, serem capazes de identificar o evento ao qual as partículas são associadas [23].

As colisões que ocorrem na área do calorímetro geram um efeito conhecido como chuva de partículas carregadas, que tem sua energia absorvida ao longo da sua trajetória nas diversas camadas sobrepostas do calorímetro. Essa energia depositada na área ativa dos sensores é detectada sob a forma de carga elétrica ou luz. Efetuando a soma das medições de energia em todos os sensores do calorímetro, obtêm-se uma estimativa da energia total das partículas que colidiram [44]. Esses dispositivos podem ser classificados em dois tipos: calorímetro eletromagnético e hadrônico. O primeiro é responsável por medir as interações eletromagnéticas de elétrons e fótons, enquanto que o segundo as interações eletromagnética e forte dos elementos hadrônicos [44].

Dentre as características que tornam os calorímetros elementos importantes no estudo da física de partículas, destaca-se [44]:

- Calorímetros são sensíveis a quase todos os tipos de partículas, tanto carregadas, como neutras;

- São adaptados para experimentos de altas energias;

- Além de serem utilizados para medição de energia, podem funcionar, também,

para detectar a posição, direção e o tempo de chegada da partícula.

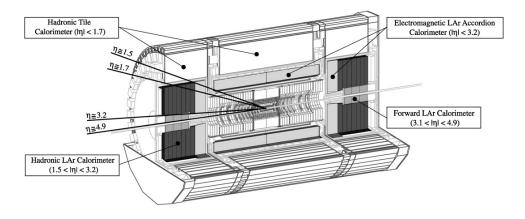

O conjunto dos calorímetros do ATLAS é dividido em 7 camadas, 4 referentes ao calorímetro eletromagnético e 3 aos calorímetro hadrônico [22]. Na Figura 2.7 é ilustrado um corte transversal no conjunto de calorímetros, apresentando suas camadas. Na Figura 2.8 é ilustrada a disposição dos calorímetros do ATLAS.

As camadas eletromagnéticas são o pré amostrador (PS Pré-Sampler), E1, E2 e E3. As camadas hadrônicas são H1, H2 e H3. Cada uma dessas camadas apresenta diferente granularidade, ou seja, concentração de células detectoras por unidade área. O Pré-Sampler, localizado na região onde  $|\eta| < 1, 8$ , é responsável por corrigir medições quando ocorre perda de energia no caminho até os calorímetros [39]. O calorímetro eletromagnético é constituído de finas folhas de chumbo separadas por sensores de argônio liquido [22] e cobre a região onde  $|\eta| < 3, 2$  [39]. Suas camadas

Figura 2.7: Corte transversal do ATLAS [22].

Figura 2.8: Diagrama dos calorímetro eletromagnético e hadrônico do ALTAS [42].

são divididas em uma parte central chamada barril, região onde  $|\eta| < 1,475$ , e duas tampas finais, onde  $1,375 < |\eta| < 3,2$  [39, 42].

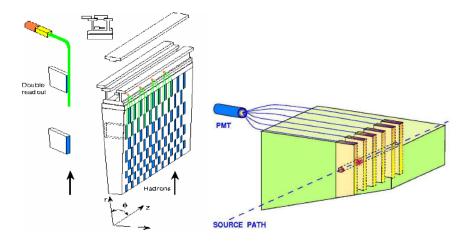

O calorímetro hadrônico é constituído por placas absorvedoras de aço separadas por telhas de material plástico cintilante, cobrindo a região onde  $|\eta| < 1, 7$ . Devido a essa estrutura, também é conhecido como calorímetro de telhas (*Tile Calorimeter* ou *TileCal*). As partículas emitem luz ao passar pelas telhas cintilantes, sendo essa de intensidade proporcional à sua energia incidente [45]. Sendo assim, através de sensores chamados de tubos fotomultiplicadores (PMT, do inglês *Photomultipier*

Tubes), a luz é transformada em sinal elétrico. Esse calorímetro tem a estrutura de um cilindro, sendo dividido em três partes: barril ( $|\eta| < 1, 0$ ) e dois barris estendidos (0, 8 <  $|\eta| < 1, 7$ ) [46, 39]. Na Figura 2.9 é ilustrado o formato do TileCal.

Figura 2.9: Ilustração do formato do TileCal [45].

As informações de energia das partículas detectadas pelos calorímetros são importantes, pois quando um evento é selecionado, ou seja, atende aos requisitos de interesse do processo de seleção online (*Trigger*), as informações são armazenadas para futuras análises *off-line*.

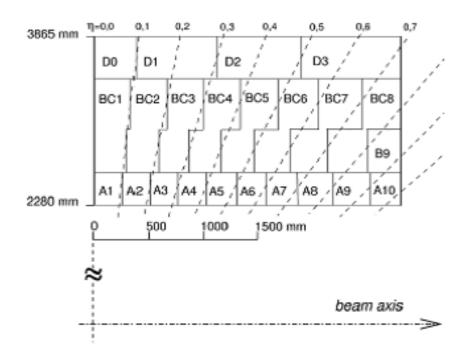

No Calorímetro do ATLAS, a granularidade das células detectoras é diferente em cada camada. Na Figura 2.10 é ilustrada essa distribuição, para uma seção do *TileCal*. Observa-se que a primeira camada, de A1 até A10, apresentam mais sensores, sendo assim, apresenta uma maior precisão na identificação da posição de interação da partícula com o detector. A segunda camada, de BC1 até BC8 e B9, apresenta menos células sendo estas com maior profundidade e, sendo assim, absorvendo maior parcela de energia. A terceira e última camada, de D0 até D3, possui ainda menos sensores e são responsáveis por capturar os detalhes finais do "chuveiro" de energia [22]. As linhas tracejadas na Figura 2.10 ilustram as possíveis trajetórias da partícula em relação às camadas.

Figura 2.10: Exemplo de Segmentação de uma parte do TileCal [47].

# ${\bf 2.3.2}$ O Sistema Online de Seleção de Eventos (Trigger) do ATLAS

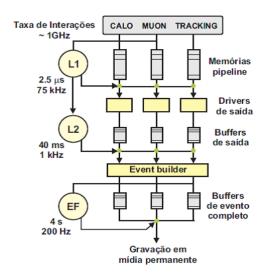

O ATLAS possui um sistema online de seleção de eventos (trigger), tendo como função selecionar os eventos de interesse produzidos pelas colisões do LHC. Esse sistema de trigger é composto por três níveis sequenciais e acessa as informações de três sub-detectores: o detector de trajetória, os calorímetros e a câmara de múons. Na Figura 2.11 é ilustrado esse sistema.

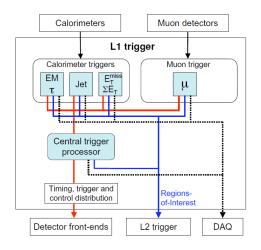

Cada nível do sistema de filtragem é responsável por descartar as assinaturas não relevantes, passando para o próximo nível, apenas as prováveis assinaturas de interesse [22]. O primeiro nível de seleção, L1, baseia-se na redução da granularidade das informações, tanto dos calorímetros, como do detector de múons e tem como principal função identificar os eventos de interesse [39]. Na Figura 2.12 é apresentado o diagrama de blocos contendo o fluxo dos sinais durante o processo de decisão desse nível. Nessa figura, observa-se que a análise dos eventos de interesse é realizada por um processador central de seleção (Central Trigger Processor) e o caminho das informações para o Front-end do detector, para o nível 2 e para o sistema de aquisição de sinais, estão destacados nas cores vermelha, azul e preta, respectivamente.

O nível L1 de seleção recebe todas as amostras geradas pelas colisões, a uma taxa

Figura 2.11: Sistema de filtragem do ATLAS [22].

Figura 2.12: Diagrama de Blocos do Nível 1 do Trigger [4].

de 40 MHz, gerando uma taxa de interações da ordem de 1 GHz, sendo responsável por reduzir de 40 MHz para 75 kHz [39]. Dessa forma, o L1 possui uma latência máxima de até  $2.5~\mu s$  após a colisão. Logo, devido a necessidade de uma alta performance, esse nível foi implementado em hardware dedicado e para atender a restrição de tempo, utiliza-se apenas de parte da resolução disponível no detector. Como ilustrado na Figura 2.11, no L1 existe um *pipeline* de memória, e nessas memórias ficam armazenadas todas as informações do detector referentes ao evento até que a seleção ou rejeição dos dados seja concluída.

O nível L2 já não possui a mesma restrição de tempo de processamento do nível L1, ou seja, lida com uma taxa menor de eventos e possui um tempo de resposta maior. Nessa etapa, a taxa de eventos é reduzida de 75 kHz para 1 kHz.

Com isso, esse nível de seleção possui critérios mais rigorosos de seleção e também utiliza-se da resolução máxima dos calorímetros. Esse nível é executado por cerca de 700 computadores através de software especializado. O segundo nível executa a seleção baseada nas informações de região de interesse disponibilizadas pelo primeiro nível, tendo acesso às informações com máxima granularidade e precisão, mesmo que seu algoritmo normalmente utilize apenas informações de regiões centrais das informações do L1 [39].

O nível L3, conhecido como *Event Filter* (EF) [4], é o último nível de seleção do sistema de *Trigger*. Esse nível utiliza-se de todas as informações não consideradas pelos outros níveis, dos eventos de interesse selecionados. Esse nível opera em software, utilizando-se de algoritmos executados por cerca de 2000 computadores em modo *off-line*. Os eventos selecionados nesse nível são armazenados definitivamente em mídia permanente. Nessa fase, a taxa de eventos é reduzida para cerca de 200 Hz [4].

## Capítulo 3

## Atualização do LHC e os Métodos de Estimação de Energia

## 3.1 Introdução

O LHC vem passando ao longo dos anos por fases de atualização. No que diz respeito ao sistema eletrônico de instrumentação dos calorímetros, é necessário que seja modificado para suportar o aumento da luminosidade. A fase 0 de atualização ocorreu entre os anos 2013 e 2014, tendo como objetivo alcançar uma luminosidade de aproximadamente  $10^{34}cm^2s^{-1}$  [5, 48]. Uma próxima parada do detector está prevista para o período entre 2018 e 2019, com o objetivo de preparar o sistema eletrônico para uma luminosidade de aproximadamente  $2-3\times10^{34}cm^2s^{-1}$ , chamada de fase 1 [5, 48]. Por último, a fase 2, prevista para ocorrer entre 2022 e 2023, tem como objetivo alcançar uma luminosidade de  $5-7\times10^{34}cm^2s^{-1}$  [5, 48].

Através do aumento da luminosidade, esse programa de atualizações permitirá o avanço dos experimentos no âmbito da Física de Partículas. Para viabilizar esse cenário, torna-se necessário realizar modificações no sistema eletrônico do *TileCal*. Dentre os principais objetivos da atualização na eletrônica do *TileCal*, destaca-se: melhorar o desempenho do nível 1 do *trigger*, aumentar a confiabilidade, melhorar a precisão das informações e a relação sinal-ruído (SNR, do inglês *Signal-to-Noise Ratio*) [5].

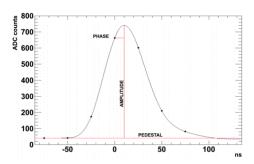

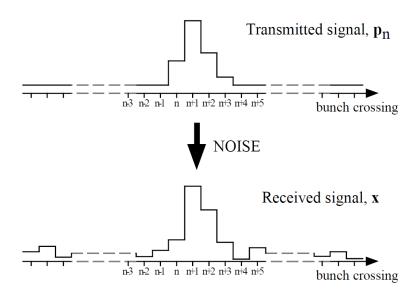

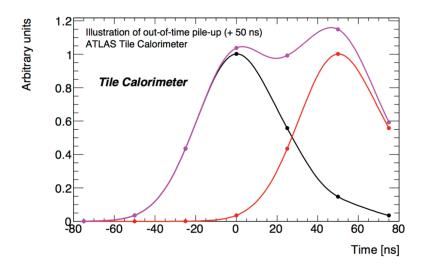

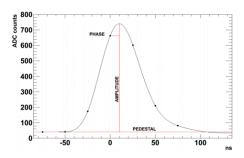

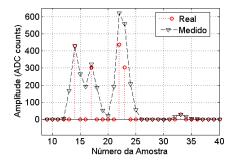

Para alcançar o desempenho desejado, o sistema de seleção de eventos precisa ter acesso a mais informações e, consequentemente, ter maior capacidade de processamento para a execução de algoritmos mais complexos [5]. Esse novo cenário de operação do ATLAS, considerando a atual arquitetura de funcionamento, provocará um problema no sistema de seleção de eventos: o empilhamento de informações subsequentes, também conhecido como *pileup*. Esse problema irá afetar, diretamente, o funcionamento do sistema de seleção, pois provocará a distorção do padrão dos eventos. O problema de empilhamento ocorre devido ao tempo de resposta dos sensores do *Tilecal*. Como pode ser observado na Figura 3.1, o pulso típico desses sensores tem duração da ordem de 150 ns.

Figura 3.1: Representação gráfica da Resposta ao Impulso Típica de um sensor [47].

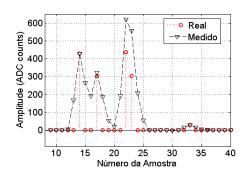

A frequência de ocorrência de colisões entre pacotes no LHC é de 40 MHz. Dessa forma, o intervalo entre duas colisões é de 25 ns. Um mesmo sensor permanece sensibilizado por até 6 colisões em sequência. Na Figura 3.2 é ilustrado (através de simulação) o efeito do empilhamento em um sensor do *Tilecal*.

Figura 3.2: Representação gráfica do efeito de empilhamento de sinais medidos [47].

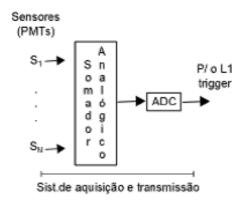

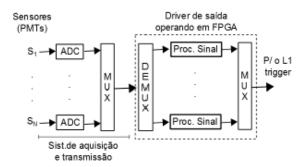

Para alcançar os objetivos do programa de atualização do LHC, a colaboração do ATLAS propôs alterações no nível 1 do sistema de *trigger* do detector. Na configuração atual, o nível 1 é alimentado por sinais resultantes de somadores analógicos, os quais têm como entradas as informações dos tubos fotomultiplicadores. Esses

somadores são responsáveis por compactar a informação, reduzindo o tempo de resposta. A alteração propõe que o nível 1 de decisão utilize todas as amostras de cada uma das PMTs, com isso, aumentando a eficiência de seleção dos eventos de interesse. Na Figura 3.3 é ilustrada a arquitetura atual do nível L1, baseado em calorimetria, e na Figura 3.4 a nova arquitetura proposta.

Figura 3.3: Arquitetura do *Trigger* L1 baseado em calorimetria atual [47].

Figura 3.4: Arquitetura do *Trigger* L1 baseado em calorimetria em desenvolvimento [47].

Devido às novas fases de operação, além da modificação do sistema eletrônico, torna-se necessário remodelar o processo de filtragem do sinal para o nível 1 de trigger. A técnica utilizada atualmente, o Filtro Casado, não é eficiente considerando o novo cenário de operação devido a distorção do sinal. Com isso, uma alternativa para a técnica de estimação de energia precisa ser desenvolvida e embarcada na nova eletrônica do detector.

# 3.2 Sistema Eletrônico Atual do Primeiro Nível de *Trigger* Baseado em Calorimetria

O sistema que compõe o Calorímetro Hadrônico do ATLAS, o *TileCal*, é dividido em uma parte óptica, uma eletrônica de *Front-End* (FE) e de digitalização e, por fim, uma eletrônica de *back-end*. A primeira é responsável por transmitir a luz depositada pelas partículas durante o seu trajeto para as Fotomultiplicadoras, onde são transformadas em pulsos elétricos [32]. As energias depositadas pelas partículas são absorvidas pelas telhas cintilantes e propagadas até suas bordas, onde são absorvidas e transportadas através de uma fibra, composta por material fotofluorescente, até a PMT. Nesse sistema, ilustrado na Figura 3.5, os fótons produzidos em cada telha é enviada para duas PMTs, garantindo a redundância do sinal, enquanto que as fibras de diferentes telhas são conectadas a uma PMT [32].

Figura 3.5: Representação gráfica do módulo do *TileCal* [32].

A eletrônica de *front-end* e de digitalização está localizada em uma estrutura de gavetas removíveis, com a finalidade de facilitar sua montagem e manutenção. Duas gavetas são interligadas, formando uma "super-gaveta", sendo que as localizadas no barril central são conectadas a 45 PMTs, enquanto as localizadas nos barris estendidos, a 32 PMTs.

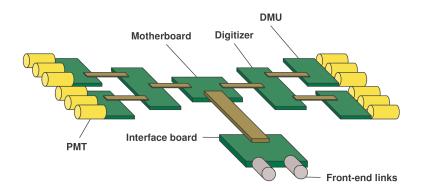

Como pode ser observado na Figura 3.6, as gavetas do sistema de *front-end* e digitalização são compostas por cinco elementos, são eles: Fotomultiplicadora (PMT), Placa Mãe (*Motherboard*), Digitalizador (*Digitizer*), Unidade de gerenciamento de informações (DMU) e Placa de Interface (*Interface Board*).

Figura 3.6: Esquemático da eletrônica de uma gaveta do TileCal [32].

Cada gaveta é composta por seis fotomultiplicadoras organizadas em grupos de 3. Esses dispositivos são divididos em quatro partes: misturador de luz, do inglês mixer; um tubo fotomultiplicador, a PMT; divisor de alta voltagem, High Voltage Divider; e o Cartão 3 em 1 [32]. O mixer é responsável por misturar a luz proveniente de todas as fibras de uma célula, a PMT realiza a conversão do sinal de luz em elétrico, o divisor particiona as altas voltagens entre os dínodos da PMT, e, por fim, o cartão 3 em 1 possui três funcionalidades: disponibilizar pulsos com ganho baixo e alto para a digitalizadora, carregar a injeção de sinais para calibração e realizar a integração lenta dos sinais da PMT para calibração e monitoramento.

A Motherboard conecta-se com as PMTs, com o Digitalizador e com a placa de interface através de três camadas [32]. A mais inferior garante a transmissão de energia de baixa tensão e sinal de controle para as PMTs, em uma camada intermediária é realizada a transmissão dos sinais analógicos das PMTs para o Digitalizador. Por fim, uma última camada é formada pelo circuito de soma e os cabos de saída do nível 1 do Trigger.

O Digitalizador é responsável por amostrar, converter e armazenar as informações de seis PMTs [32]. O processo de amostragem é realizado através de Conversores Analógico Digital, do inglês Analog Digital Converter (ADC), com resolução de 10 bits. Esses sinais digitalizados são armazenados nas duas DMUs. Além desses componentes, o equipamento possui um circuito integrado responsável pelo sistema de sincronização e programação, atuando na distribuição do clock juntamente com as informações de sincronização e controle para a eletrônica do Front-End. Os sinais digitais ficam armazenados nas unidade de gerenciamento de informações a espera da

decisão do nível 1 do sistema de *Trigger* e, quando selecionados, são disponibilizados para os *buffers* de saída [32].

Dentre outros dispositivos, os *Drivers* de Saída, *Read-out Driver* (ROD), são os elementos centrais da eletrônica de *Back-End* [49]. Como pode ser observado na Figura 2.11, esses elementos ficam localizados entre o primeiro e o segundo nível do sistema de *Trigger*. As informações de energia produzidas pelo ATLAS são identificadas e digitalizadas pelo sistema de Front-end e então enviadas para esses *drivers* [32]. Nesses dispositivos, as informações dos módulos do calorímetro, enviadas a uma taxa de 100 kHz, são processadas e transmitidas para o nível 2 [32, 49].

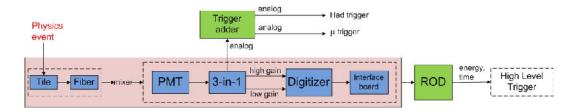

Na Figura 3.7 é possível identificar o caminho do sinal na arquitetura atual do sistema eletrônico do ATLAS no nível 1. Nessa arquitetura, os sinais do primeiro nível são produzidos por somas analógicas de seis sinais de energia, tendo suas saídas transmitidas para o nível 1. Quando ocorre um evento físico, gera-se um sinal óptico no calorímetro, que é transmitido para a eletrônica de *Front-End*. Nessa etapa, o mixer realiza a mistura das informações das fibras de uma célula, que é enviada para a PMT. Esses sinais são processados pelo cartão 3 em 1, os quais são digitalizados a 40 MHz por ADCs de 10 bits. Por fim, os sinais digitalizados das células de um evento selecionado pelo primeiro nível são transmitidos para a eletrônica de *Back-End*.

Figura 3.7: Representação gráfica do caminho do sinal na arquitetura atual do *TileCal* [5].

O nível 1 do sistema de *Trigger* do *TileCal* é alimentado com os sinais analógicos provenientes das estruturas de soma analógica, ou seja, das torres de *trigger*. Esses dispositivos são constituídos de somadores de alto desempenho e um circuito adicional de linha de condução [50]. As informações resultantes desse sistema, que representam combinações das camadas de segmentação do calorímetro, contribuem com a redução da quantidade de sinais processados nesta etapa, reduzindo para uma

taxa de 75 kHz [50]. Sendo assim, esse nível define as regiões de interesse a partir de combinações de sinais, ou seja, com reduzida granularidade [50].

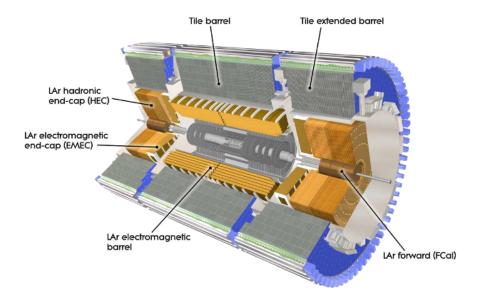

# 3.3 Sistema Eletrônico que será Utilizado após a Atualização do LHC

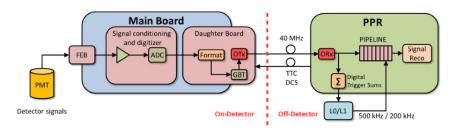

O programa de atualização do *TileCal* propõe modificações em todo o sistema eletrônico do detector, tanto no *Front-end* como no *Back-end*, inclusive estuda-se realizar alterações também em seu sistema mecânico, além das atualizações necessárias no sistema de fontes de alimentação [5]. Na Figura 3.8 pode-se observar o caminho da informação na proposta de atualização dos sistemas eletrônicos do *TileCal*.

Figura 3.8: Representação gráfica do caminho da informação na atualização dos sistemas eletrônicos do *TileCal* [51]

Através da Figura 3.8 pode-se observar que a eletrônica embarcada no detector, representada pela região *On-Detector*, é composta por: Uma nova placa de *Front-End*, uma placa principal, do inglês *Main Board* (MB) e uma placa filha, do inglês *Daughter Board* (DB). A primeira é responsável, entre outras funções, pelo condicionamento e amplificação dos sinais. A MB realiza a digitalização, enquanto que a DB processa a informação e transmite para a eletrônica não embarcada do detector, representa pela região *Off-Detector* [5, 52, 51, 53].

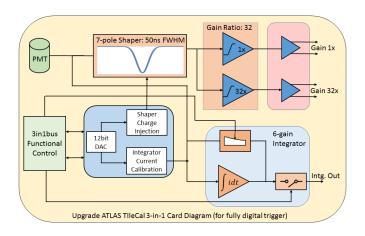

O grupo de pesquisadores do ATLAS está avaliando o desenvolvimento de três diferentes arquiteturas para a eletrônica do FE, denominadas: Front-End-Modified 3-in-1 card, Front-end-QIE chip e a Front-End-FATALIC ASISC [52, 54]. A primeira propõe uma modificação na estrutura do Cartão 3 em 1 presente na arquitetura atual do FE e apresenta-se como uma solução que utiliza elementos discretos, proporcionando melhor linearidade e menor ruído [53]. Baseado na Figura 3.9 pode-se

observar que nessa proposta de arquitetura o sinal analógico da PMT é moldado e seus ganhos, tanto o alto como o baixo, são amplificados com uma taxa de 1:32, digitalizados com 12 bits e amostrados a uma frequência de 40 MHz [55].

Figura 3.9: Protótipo da Proposta de Arquitetura de Modificação do Front-End Baseado no Cartão 3 em 1 [53].

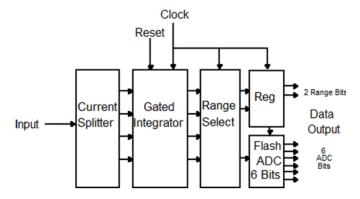

As outras duas propostas de arquitetura para o Front-End utilizam circuitos integrados dedicados. Na solução baseada no chip QIE, que representa Carga, Integrador e Codificador, do inglês Charge, Integrator and Encoder, não realiza-se a modelagem do pulso, reduzindo o problema do efeito de sobreposição e permitindo que os pulsos da PMT sejam medidos [53]. Como pode ser observado na Figura 3.10, o sinal de entrada passa por um divisor de corrente que divide a informação em quatro ganhos. Cada informação então será processada por um integrador e digitalizada por estruturas de ADCs de 6 bits.

Figura 3.10: Diagrama do Fluxo do Sinal do Front-End Baseado no Chip QIE [52].

A terceira opção de arquitetura para o sistema eletrônico do *Front-End* também baseia-se na utilização de um chip dedicado, um Circuito Integrado de Aplicação Es-

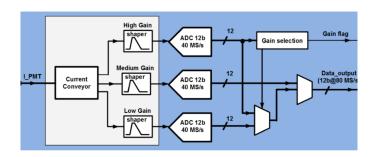

pecífica (ASIC, do inglês Application Specific Integrated Circuit). Através da Figura 3.11 pode-se observar um diagrama básico deste circuito. Denominada de FATA-LIC, abreviação para Front-end for Atlas TilecAL Integrated Circuit, essa proposta utiliza um transportador de corrente para três diferentes faixas de ganho (1x, 8x e 64x). Para cada ganho, o sinal será digitalizado por ADC de 12 bits [53].

Figura 3.11: Diagrama do Fluxo do Sinal do Front-End Baseado no Chip FATA-LIC [52].

Em relação a eletrônica de *Back-End*, representada pela região *Off-Board* na Figura 3.8, uma nova *Read-Out Driver* (*ROD*) está sendo desenvolvida, chamada de "Super" *Read-Out Driver* (*sROD*) [5, 48]. Dentre as funções dessa eletrônica de componentes não embarcados no detector, destaca-se: processamento e recepção da informação proveniente das placas filhas (*Daughter Boards*); Reconstrução e envio dos sinais para o sub-sistema de saída (do inglês *ReadOut Subsystem - ROS*); pré processamento e transmissão da informação para o nível 1 do sistema de seleção de eventos; implementação de algoritmos de reconstrução de sinal; entre outras [5, 53, 48].

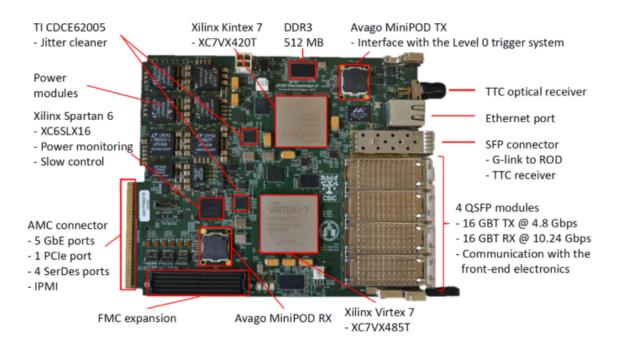

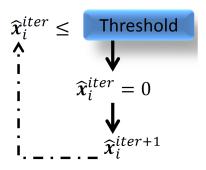

Como pode ser visto na Figura 3.12, a placa da sROD é composta por: módulos QSFP, do inglês Quad Small Form-factor Pluggable, responsáveis pela comunicação com a eletrônica de Front-End; dispositivos FPGA, um Xilinx Virtex 7 e um Kintex 7, responsáveis pelo pré processamento e envio da informação para o nível 1 do Trigger, pela compactação e descompactação das informações de energia e controle, armazenamento dos sinais em memórias, recebimento e decodificação das informações de controle, temporização e seleção, entre outras [56, 53, 48]. Além desses elementos, a placa possui ainda módulos para gerenciamento de energia, comunicação Ethernet, memórias DDR3, entre outros.