### Universidade Federal da Bahia Programa de Pós-graduação em Engenharia Elétrica

Projeto de um Receptor BFSK Integrado para HBC Baseado na Técnica de Injection Locking.

#### Autor:

Marinel Borges Almeida

**Salvador,Bahia** Fevereiro,2024

### Universidade Federal da Bahia Programa de Pós-graduação em Engenharia Elétrica

### Marinel Borges Almeida

# Projeto de um Receptor BFSK Integrado para HBC Baseado na Técnica de Injection Locking.

Dissertação apresentada ao Programa de Pós-graduação em Engenharia Elétrica, como requisito para conclusão do curso stricto-senso em Engenharia Elétrica da Universidade Federal da Bahia sob orientação do Professor Dr.Edson Pinto Santana e coorientação do Professor Dr.Maicon Deivid Pereira.

Orientador: Edson Pinto Santana

Coorientador: Maicon Deivid Pereira

Data da Defesa:

01 de Fevereiro de 2024

# Ficha catalográfica elaborada pelo Sistema Universitário de Bibliotecas (SIBI/UFBA), com os dados fornecidos pelo(a) autor(a).

Borges Almeida, Marinel

Projedo de um Receptor BFSK Integrado Para HBC Baseado na Técnica de Injection Locking / Marinel Borges Almeida, Maicon Deivid Pereira. -- Salvador, 2024.

75 f. : il

Orientador: Edson Pinto Santana. Coorientador: Maicon Deivid Pereira. Dissertação (Mestrado - Pós graduação Engenharia Eleétrica) -- Universidade Federal da Bahia, Universidade Federal da Bahia, 2024.

1. Receptor. 2. HBC. 3. Integrado. 4. CMOS. 5. Baixo Consumo. I. Deivid Pereira, Maicon. I. Pinto Santana, Edson. II. Deivid Pereira, Maicon . III. Título.

### Universidade Federal da Bahia Programa de Pós-graduação em Engenharia Elétrica

### Folha de Aprovação

Projeto de um Receptor BFSK Integrado para HBC Baseado na Técnica de Injection Locking.

Autor: Data da Defesa:

Marinel Borges Almeida 01 de Fevereiro de 2024

#### Banca Examinadora

| Edson Pinto Santana             | (Orientador) Edson Pinto Sontana      |        |

|---------------------------------|---------------------------------------|--------|

| Doutorado                       | UFBA                                  |        |

|                                 |                                       |        |

| Maicon D Santana                | (Coorientador)                        |        |

| Doutorado                       | UFBA Maricon O. Percina               |        |

|                                 |                                       |        |

| Edson Pinto Santana             | (Examinador) Esson Pinto Sontana      |        |

| Doutorado                       | UFBA                                  | _      |

|                                 |                                       |        |

| Robson Nunes de Lima            | (Examinador) Pobou Hurs de dim        | 9_     |

| Doutorado                       | UFBA                                  | _      |

|                                 |                                       |        |

| Gabriele Costa Gonçalves Dantas | (Examinador) Cabriele Cota Gonçales D | lantar |

| Doutorado                       | UFRB                                  |        |

Salvador, Bahia, Brasil Fevereiro, 2024

### Resumo

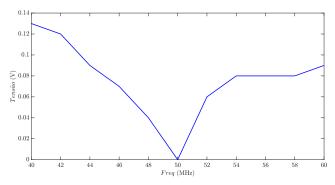

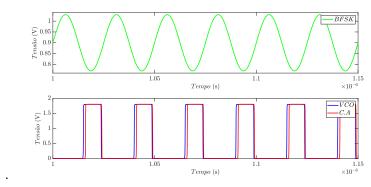

As tecnologias de telecomunicação avançaram a ponto de possibilitar redes especializadas na transmissão de dados nas proximidades do corpo. Este método de comunicação, conhecido como Body Area Network (BAN), está evoluindo rapidamente, exigindo maior portabilidade e uma vida útil mais extensa das baterias. Isso, por sua vez, impulsiona a necessidade de redução no consumo de energia. Por esse motivo, soluções têm sido estudadas nas últimas três décadas para aprimorar a eficiência energética na transmissão de sinais. Dentre essas tecnologias, a técnica HBC (Human Body Communication) destaca-se nas pesquisas acadêmicas recentes. O HBC é um método de comunicação sem fio para redes corporais que oferece vantagens em termos de consumo, segurança e interferência quando comparado a outros métodos baseados em radiação. Essa vantagem advém da utilização do corpo humano como canal de transferência de sinal. No presente trabalho, descrevem-se o projeto e as simulações pós-leiaute de um receptor para HBC com acoplamento capacitivo, desenvolvido em tecnologia CMOS de 180 nm, capaz de demodular sinais BFSK. Utiliza-se uma arquitetura que realiza a conversão frequência-fase, explorando o fenômeno de injection locking. O receptor projetado incorpora um amplificador de entrada para elevar o sinal recebido aos níveis necessários para injection locking em um VCO (Voltage Controlled Oscillator). Com o injection locking, uma diferença de fase estará presente entre o sinal do VCO e o sinal injetado. Essa diferença de fase é identificada por um detector de fase, que determina se o sinal do VCO está atrasado ou adiantado. Após filtragem e comparação dos sinais de saída do detector de fase, obtém-se a demodulação do sinal BFSK. As simulações pós-leiaute do circuito demonstram a capacidade do receptor para operar na faixa entre 40 e 60 MHz, com taxas de dados de até 5 Mbps, consumo entre 0,74 mW e 1,58 mW, e eficiência de comunicação entre 148 pJ/bit e 316 pJ/bit, com alimentação de 1,5 V e 1,8 V, respectivamente. O estudo realizado neste trabalho incrementa o conhecimento sobre o projeto de receptor para HBC demostrando um caminho para o melhoramento no consumo de energia na comunicação de sinal sem fio, permitindo seu uso em BANs em aplicações médicas, de segurança ou entretenimento.

Palavras-chave: Baixo consumo, CMOS, HBC, Injection Locking, Receptor.

### Abstract

Telecommunication technologies have advanced to the point of enabling networks specialized in data transmission in close proximity to the body. This method of communication, known as Body Area Network (BAN), is evolving rapidly, demanding greater portability and longer battery life. This, in turn, drives the need for reduced power consumption. For this reason, solutions have been studied over the last three decades to improve energy efficiency in signal transmission. Among these technologies, the Human Body Communication (HBC) technique stands out in recent academic research. HBC is a wireless communication method for body networks that offers advantages in terms of consumption, security, and interference compared to other radiation-based methods. This advantage comes from using the human body as a signal transfer channel. In this paper, we describe the design and postlayout simulations of a receiver for HBC with capacitive coupling, developed in 180 nm CMOS technology, capable of demodulating BFSK signals. We employ an architecture that performs frequency-phase conversion, exploiting the phenomenon of injection locking. The designed receiver incorporates an input amplifier to raise the received signal to the levels required for injection locking in a Voltage Controlled Oscillator (VCO). With injection locking, a phase difference will be present between the VCO signal and the injected signal. This phase difference is identified by a phase detector, which determines whether the VCO signal is delayed or advanced. After filtering and comparing the output signals of the phase detector, BFSK signal demodulation is obtained. Post-layout simulations of the circuit demonstrate the receiver's ability to operate in the range between 40 and 60 MHz, with data rates of up to 5 Mbps, power consumption between 0.74 mW and 1.58 mW, and communication efficiency between 148 pJ/bit and 316 pJ/bit, with power supply of 1.5 V and 1.8 V, respectively. The study conducted in this work enhances the knowledge of receiver design for HBC by demonstrating a pathway for improving energy consumption in wireless signal communication, enabling its use in BANs in medical, security, or entertainment applications.

**Keywords**: Low consumption, CMOS, HBC, Injection locking, Receptor.

# Agradecimentos

Gostaria de agradecer ao meu coorientador, Dr. Professor Maicon Deivid Pereira, que me ajudou muito neste trabalho, além de suas responsabilidades. Agradeço também aos meus colegas de curso que me apoiaram nesta jornada, à Dra. Profa. Ana Isabela Cunha que me apoiou desde a primeira aula na Universidade Federal da Bahia.

| Este trabalho é todo dedicado aos meus pais, poi posso concluir este Mestrado. | s é graças ao seu esforço que hoje                                                                                                                                                      |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                | "Os que se encantam com a prática<br>sem a ciência são como os<br>timoneiros que entram no navio<br>sem timão nem bússola, nunca<br>tendo certeza do seu destino."<br>Leonardo da Vinci |

|                                                                                |                                                                                                                                                                                         |

|                                                                                |                                                                                                                                                                                         |

| iv                                                                             |                                                                                                                                                                                         |

# Lista de Tabelas

| 1.1  | Características dos métodos de comunicação                         |    |

|------|--------------------------------------------------------------------|----|

| 4.1  | Impedância de entrada por tensão de controle em Volts              | 38 |

| 4.2  | Razões de aspecto do oscilador em anel.                            | 42 |

| 4.3  | Razões de aspecto dos transistores externos.                       | 43 |

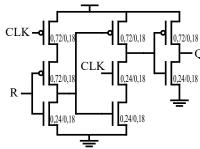

| 4.4  | Dimensões dos transistores do flip-flop tipo D                     | 48 |

| 4.5  | Dimensões dos transistores na porta AND CMOS                       | 48 |

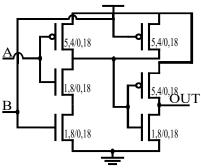

| 4.6  | Dimensões do primeiro estágio do comparador com latch              | 52 |

| 4.7  | Dimensões do estágio 3 do comparador com <i>latch</i>              | 53 |

| 4.8  | Consumo em Watts por tensão de alimentação em Volts                | 64 |

| 4.9  | Comparação da potência consumida para diferentes taxas de transfe- |    |

|      | rência de dados                                                    | 65 |

| 4.10 | Resumo do comportamento do circuito em função da tensão de ali-    |    |

|      | mentação e da temperatura de testes                                | 66 |

| 5.1  | Características dos receptores citados na introdução e do receptor |    |

|      | proposto.                                                          | 69 |

# Lista de Figuras

| 1.1  | Fluxograma da metodologia                                                       |

|------|---------------------------------------------------------------------------------|

| 2.1  | Circuito do receptor com interface capacitiva.                                  |

| 2.2  | Circuito receptor com <i>PIC</i>                                                |

| 2.3  | Transceptor com TRX e RX 8                                                      |

| 2.4  | Transeptor com dois TRXs e dois RXs                                             |

| 2.5  | Circuito do receptor BFSK                                                       |

| 2.6  | TRX POFDM e FSK                                                                 |

| 2.7  | Transceptor NRZ                                                                 |

| 2.8  | Diagrama do wake-up receiver                                                    |

| 3.1  | Imagem ilustrativa do fluxo elétrico do acoplamento capacitivo 17               |

| 3.2  | Modelo RC equivalente ao tecido em nível celular                                |

| 3.3  | Modelo do canal                                                                 |

| 3.4  | Transistor de efeito de campo                                                   |

| 3.5  | Curva $I_D \times V_{DS}$ do MOSFET tipo N                                      |

| 3.6  | Exemplo de receptor heteródino                                                  |

| 3.7  | Exemplo de receptor homodino                                                    |

| 3.8  | Topologia do receptor FSK síncrono                                              |

| 3.9  | Topologia do receptor FSK zero crossing                                         |

| 3.10 | Topologia do receptor FSK com PLL                                               |

| 3.11 | Topologia do receptor não síncrono                                              |

| 3.12 | Demodulador FSK miniaturizado                                                   |

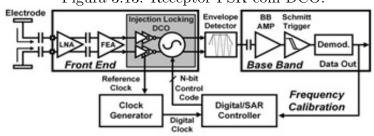

| 3.13 | Receptor FSK com DCO                                                            |

| 3.14 | Topologia de receptor com <i>Injection Locking</i>                              |

| 3.15 | Módulo e fase do circuito sob injection locking                                 |

| 3.16 | Exemplo de circuito oscilador                                                   |

| 3.17 | Diagramas de fasor das correntes em um injection locking oscilator              |

|      | para diferentes valores de $ \omega_0 - \omega_{inj} $ e amplitude de $I_{inj}$ |

| 3.18 | Transição de fases em um oscilador injetado                                     |

| 4.1  | Topologia apresentada neste trabalho                                            |

| 4.2  | Exemplo de circuitos amplificadores com MOSFET                                  |

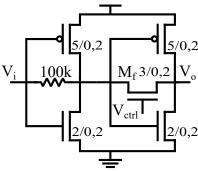

| 4.3  | Amplificador de entrada (valores de dimensões W e L dos transistores            |

|      | em micrometro)                                                                  |

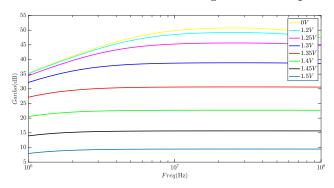

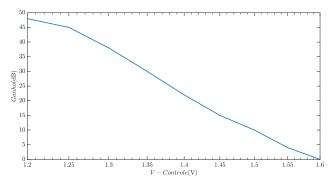

| 4.4  | Curvas da Varredura do ganho do amplificador.                                                                                     | 37       |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.5  | Ganho em função tensão de controle(V-Controle) do amplificador                                                                    | 37       |

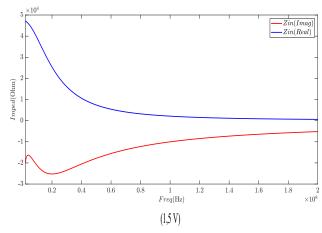

| 4.6  | Impedância de entrada com tensão de controle de 1,5 V                                                                             | 37       |

| 4.7  | Impedância de entrada para tensões de controle de 0 a 1,45 V                                                                      | 38       |

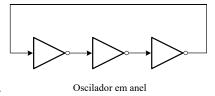

| 4.8  | Oscilador em anel com inversores                                                                                                  | 39       |

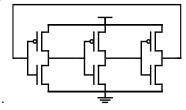

| 4.9  | Topologia do oscilador em anel com inversores CMOS                                                                                | 39       |

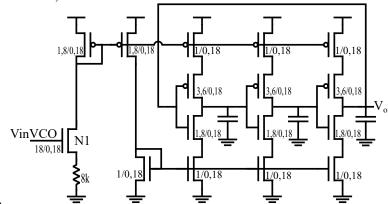

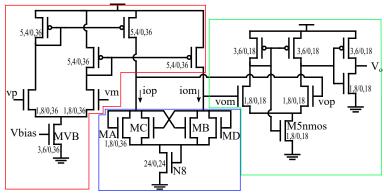

| 4.10 | Topologia do circuito interno do VCO( dimensões W e L dos transistores estão em micrometro)                                       | 41       |

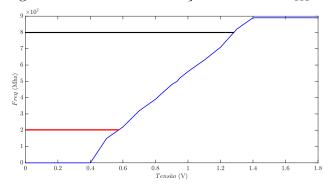

|      | Oscilador em anel com buffer extra para injection locking Curva da relação VinVco x $F_{osc}$                                     | 42<br>42 |

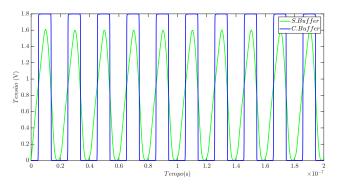

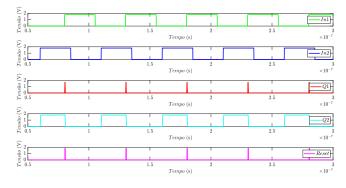

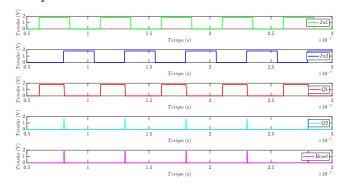

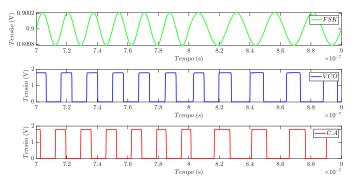

|      | Curvas de saída em oscilação natural utilizando tensão de controle em 0,9 V no VCO.                                               | 43       |

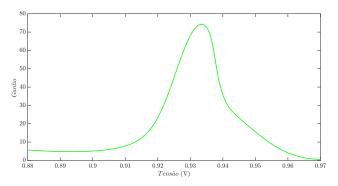

| 111  | Curva de comportamento do intertravamento $V_{inj}$ por frequência no                                                             | 40       |

| 4.14 | VCO                                                                                                                               | 44       |

| 4.15 | Curvas do comportamento do VCO 40 MHz                                                                                             | 44       |

|      | Curvas do comportamento do VCO 60 MHz                                                                                             | 45       |

|      | Circuito Detetor de fase completo                                                                                                 | 46       |

|      | Circuito flip-flop tipo D(dimensões W e L dos transistores em micro-                                                              |          |

|      | metro)                                                                                                                            | 47       |

| 4.19 | Circuito porta lógica $AND$ CMOS(dimensões W e L dos transistores                                                                 |          |

|      | em micrometro).                                                                                                                   | 47       |

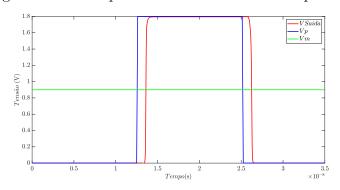

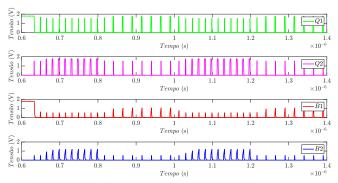

|      | Comportamento do circuito PD com a entrada In2 avançada                                                                           | 49       |

|      | Comportamento do circuito PD com a entrada In1 avançada                                                                           | 49       |

|      | Circuito simplificado do último estágio com filtro e comparador Circuito do comparador com laço e buffer de saída com dimensões W | 50       |

|      | e L em $\mu m$                                                                                                                    | 52       |

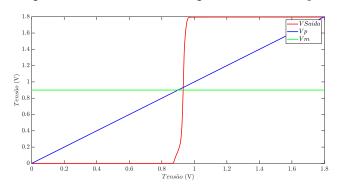

|      | Comportamento da saída do comparador                                                                                              | 53       |

|      | Curva de ganho do comparador em relação a tensão de entrada                                                                       | 54       |

|      | Resposta transiente do comparador em relação à entrada $V_p$                                                                      | 54       |

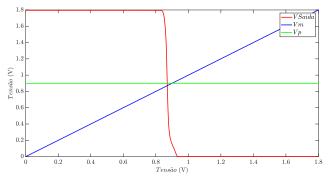

|      | Resposta transiente do comparador em relação à entrada $V_m$                                                                      | 55       |

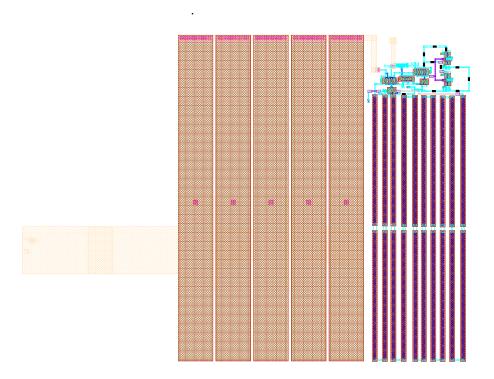

|      | Leiaute do amplificador de entrada e buffers                                                                                      | 56       |

|      | Leiaute do VCO e do circuito auxiliar.                                                                                            | 57       |

|      | Leiaute do detetor de fase e dos <i>buffers</i> de saída das portas Q1 e Q2.                                                      | 57       |

|      | Leiaute do filtro RC e do comparador.                                                                                             | 58       |

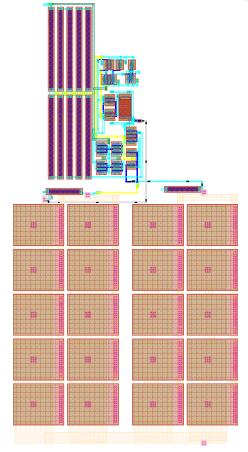

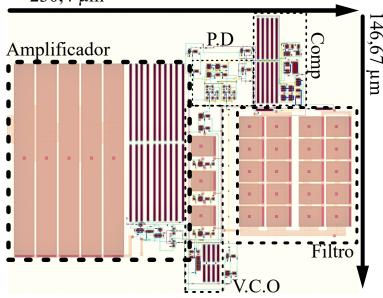

|      | Leiaute do Receptor com circuitos destacados.                                                                                     | 59       |

|      | Circuito de buffers exponenciais para saídas de medição.                                                                          | 60       |

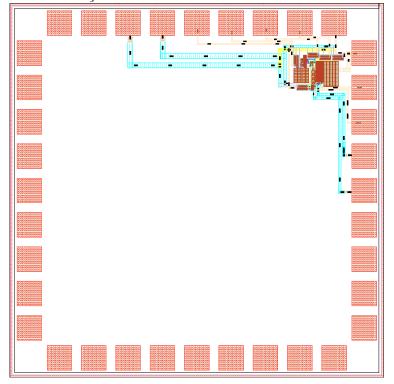

| 4.34 | Leiaute do circuito completo com <i>pads</i> e <i>buffers</i> de medição exponenciais para saídas de medição                      | 60       |

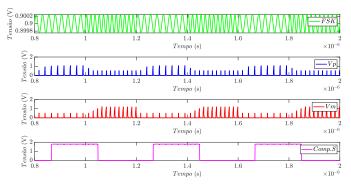

| 4 35 | Sinais de entrada FSK e das saídas do VCO e do sinal cópia no mo-                                                                 | UU       |

| 4.00 | mento da troca de frequência na entrada                                                                                           | 61       |

| 4.36 | Sinais das saídas da conversão frequência-fase antes e depois da apli-                                                            |          |

|      | cação dos buffers                                                                                                                 | 62       |

| 4.37 | Comparação entre o sinal FSK, as entradas do comparador e sua saída.                                                              | 62       |

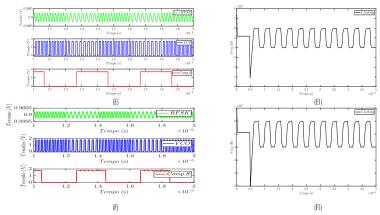

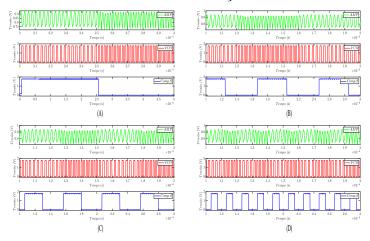

| 4.38 | Curvas de funcionamento com tensão alimentação de 1,3 V(A) 1,4    |    |

|------|-------------------------------------------------------------------|----|

|      | V(B)-1,5 $V(C)$ -1,6 $V(D)$ e temperatura de 27° $C$              | 63 |

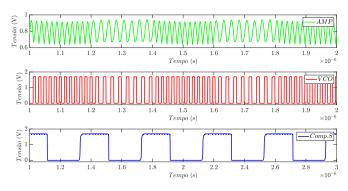

| 4.39 | Curvas de funcionamento com tensão alimentação de 1,7 $V(E)$ -1,8 |    |

|      | V(F) e temperatura de 27° C                                       | 64 |

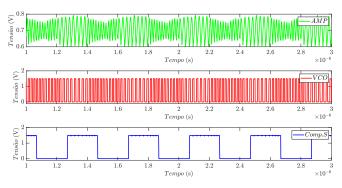

| 4.40 | Curvas resultantes das variações da taxa de transferências        | 65 |

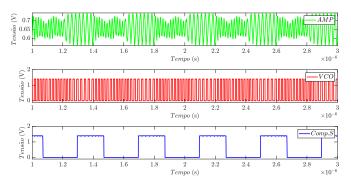

| 4.41 | Exemplo de curva de saída para temperatura de 50° C com tensão de |    |

|      | alimentação de 1,7 V                                              | 66 |

| 4.42 | Exemplo de curva das saídas para temperatura de 0° C e tensão de  |    |

|      | alimentação de 1,5 V                                              | 67 |

| 4.43 | Exemplo de curva das saídas para temperatura de 0° C e tensão de  |    |

|      | alimentação de 1,4 V                                              | 67 |

# Sumário

| R          | esumo                    |                                                                                                                                                                                                                                                                    | j                                      |

|------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| <b>A</b> l | bstrac                   | et et                                                                                                                                                                                                                                                              | ii                                     |

| A          | grade                    | cimentos                                                                                                                                                                                                                                                           | iii                                    |

| Li         | sta de                   | e Tabelas                                                                                                                                                                                                                                                          | v                                      |

| Li         | sta de                   | e Figuras                                                                                                                                                                                                                                                          | viii                                   |

| Li         | sta de                   | e Abreviações                                                                                                                                                                                                                                                      | xi                                     |

| Li         | sta de                   | e Símbolos                                                                                                                                                                                                                                                         | xiii                                   |

| 1          | 1.1<br>1.2<br>1.3        | odução Contextualização Objetivos Metodologia                                                                                                                                                                                                                      | 3                                      |

| 2          | Esta                     | do da arte de transceptores e receptores para HBC capacitivo                                                                                                                                                                                                       | 6                                      |

| 3          | 3.1<br>3.2<br>3.3<br>3.4 | damentação teórica  HBC - Comunicação pelo corpo humano 3.1.1 Acoplamento capacitivo 3.1.2 Modelagem do canal  MOSFET  Arquitetura de um receptor RF 3.3.1 Receptores heteródinos 3.3.2 Receptores homodinos 3.3.3 Topologias de receptores FSK  Injection Locking | 16<br>17<br>19<br>22<br>22<br>23<br>23 |

| 4          | <b>Pro</b> 3             | 1                                                                                                                                                                                                                                                                  |                                        |

|            |                          | 4.1.1 Simulações pós-leiaute do Amplificador de entrada                                                                                                                                                                                                            | 36                                     |

| Re | eferêr | acias                                                        | <b>7</b> 1 |

|----|--------|--------------------------------------------------------------|------------|

| 6  | Tral   | oalhos futuros                                               | 70         |

| 5  | Con    | clusão                                                       | 68         |

|    |        | 4.5.1 Integração do receptor                                 | 60         |

|    | 4.5    | Leiaute                                                      | 56         |

|    | 4.4    | Estágio comparador com <i>latch</i> , filtro e <i>buffer</i> | 50         |

|    | 4.3    | Detector de fase                                             | 46         |

|    | 4.2    | VCO (Voltage Controlled Oscilator)                           | 36         |

# Lista de Siglas

| Abreviação | Descrição |

|------------|-----------|

| BAN        | Rede de Á |

| WCN        | Rodo do S |

Area Corporal Rede de Sensores Sem Fio WSN HBC Comunicação pelo corpo

GPS Sistema de Posicionamento global

RFRadiofrequência

PFD Detector Frequência Fase

PDDetetor de fase

ILO Oscilador com Injection Locking ZCDDetector de cruzamento no zero

CACircuito Auxiliar DEC Circuito de decisão **UWB** Banda Ultra larga

ICL Ligações indutivo-capacitivas

TXTransmissor RXReceptor

TRX Transmissor com Receptor OOK Chaveamento liga desliga

**FSK** Chaveamento por troca de frequências

**BFSK** Chaveamento Binário por troca de Frequências

OSC Oscilador

DPFSK Chaveamento Diferencial de Fase

CMOS Semicondutor de Óxido Metálico Complementar

MOSFET Transistor de Efeito de Campo Metal-Oxido-Semicondutor

ADC Conversor Analógico Digital DAC Conversor Digital Analógico LNA Amplificador de baixo ruido

NRZ Sem retorno para Zero

NRZI Não Retorno a o Zero Invertido

**PMOS** Transistor MOS Tipo P **NMOS** Transistor MOS tipo N EDDetector de envoltória

LO Oscilador Local LPF Filtro passa-baixas BPF Filtro passa-faixas

PG Amplificador com ganho programável

PLL Loop de Fase de Bloqueio

Cont Contador

VCO Oscilador controlado por tensão

CLK Clock

ALC Compensamento autmático de perdas

RC Resistivor-capacitor LC Indutor-capacitor

QAM Modulação de Amplitude em Quadratura

OFDM Multiplexação por Divisão de Frequências Ortogonais QPFSK Chaveamento de Fase por Frequência de Quadratura

IL-DCO Oscilador Controlado Digitalmente

DC Corrente Contínua

FFT Transformada Rápida de Fourier

MUX Multiplexador

PIC Comunicação por indexação de pulso

# Lista de Símbolos

| Símbolo          | Descrição                               |

|------------------|-----------------------------------------|

| $\alpha$         | Fator de incremento alpha               |

| $\beta$          | Ganho do transistor                     |

| $\phi_{osc}$     | Fase do oscilador                       |

| $\phi_{inj}$     | Fase da frequência injetada             |

| $\phi$           | Fase                                    |

| $\omega$         | Frequência                              |

| $\Theta$         | Defasagm                                |

| $\phi_0$         | Desvio de fase                          |

| $\omega_0$       | Frequência natural                      |

| $\omega_1$       | Frequência do oscilador injetado        |

| $\omega_{lo}$    | Frequência do oscilador                 |

| $\mu$            | Mobilidade dos elétrons                 |

| $\phi_t$         | Tensão Termodinâmica                    |

| $\lambda$        | Coeficiente de modulação do canal       |

| $\varepsilon_0$  | Permissividade Absoluta do vácuo        |

| $\sigma(\omega)$ | Condutividade                           |

| $\Delta f$       | Largura de banda                        |

| ID               | Corrente de Dreno                       |

| $W_{inj}$        | Frequência injetada                     |

| $I_{inj}$        | Corrente injetada                       |

| $V_{inj}$        | Tensão injetada                         |

| $V_{dd}$         | Tensão de alimentação                   |

| $A_v$            | Ganho de tensão                         |

| $g_m$            | Transcondutância em pequenos sinais     |

| $g_{mn}$         | Transcondutância canal n                |

| $g_{mp}$         | Transcondutância canal p                |

| $R_L$            | Resistência de Carga                    |

| $R_{MF}$         | Resistência equivalente do transitor MF |

| DC               | Corrente Contínua                       |

| $V_{ctrl}$       | Tensão de controle                      |

| SNR              | Relação sinal Ruido                     |

| С                | Capacidade do canal                     |

# Capítulo 1

# Introdução

### 1.1 Contextualização

Com o aumento da necessidade de monitoramento, movimentação e ações humanas, a utilização de sensores em uma rede para fornecimento de dados em tempo real tornou-se indispensável. Essas redes são chamadas WSN (Wireless Sensor Network) ou, quando utilizadas próximo ao corpo humano, recebem o nome de BAN (Body Area Network)[1] [2]. Esses sensores desempenham três funções fundamentais: comunicação, que pode ocorrer entre eles ou com dispositivos externos; sensoriamento, envolvendo a captura e gravação de dados, como o ritmo cardíaco, movimentação e deslocamento do indivíduo ou de qualquer objeto estranho ao corpo; e processamento de dados quando necessário [1][3][4].

Os biossensores utilizados em redes BAN podem ser classificados como invasivos, posicionados dentro do corpo humano, ou não invasivos, situados na pele[2][5]. Uma das aplicações inclui áreas militar e desportiva para captura de desempenho, com entrada de dados como velocidade, aceleração e força de um determinado movimento, possibilitando correções de técnica. Também encontramos esses sensores na sociedade civil, como em jogos eletrônicos que reproduzem os movimentos dos usuários[3]. Outra aplicação está no mercado dos *smartwatches*, que possuem sensores capazes de medir, por meio do GPS (Global Positioning System), a velocidade e a distância percorrida. Esses dispositivos também contam com sensores de medição do batimento cardíaco colocados no pulso, enviando esses dados para o celular do usuário. Na área de desenvolvimento de software, grandes empresas de jogos ou filmes replicam movimentos de atores para incorporar em personagens por meio de computação gráfica. Existem também aplicações na área de segurança, como assinaturas digitais que carregam dados pessoais para solicitação e pagamento de serviços, autenticação de segurança para acesso a áreas restritas e prevenção de fraudes [3]. Existem pesquisas como a de [6] que focam na robótica com um sistema capaz de captar sinais cerebrais transmitidos para o punho e retransmitir de forma compreensível para uma mão biônica para que a mesma realize movimento de acordo

com o sinal enviado. Para a área médica geralmente utilizada em BAN a taxa de transferência varia entre 10 kbps e 10 Mbps [7].

Para aplicações em BANs, a comunicação por RF (Radiofrequência) apresenta alta susceptibilidade à interferência eletromagnética, sofrendo atenuação do sinal causada pelo corpo humano. Isso aumenta a probabilidade de perda de desempenho e, em casos mais graves, de cortes completos na transmissão. Por esse motivo, os transmissores e receptores precisam ser mais potentes, resultando em uma relação desfavorável entre a energia consumida e a capacidade de transferência de dados (J (Joule)/bit).

Por outro lado, o método de comunicação chamado HBC (Human Body Communication) utiliza o próprio corpo humano como meio de transmissão de sinais e apresenta baixa atenuação na faixa entre 0,1 - 100 MHz. Isso reduz a potência necessária para os transmissores e receptores, além da complexidade e do tamanho dos circuitos quando comparados aos transceptores baseados em RF [8]. Isso permite o aumento da duração das baterias, ou a redução do seu tamanho, possibilitando um menor número de trocas e uma maior portabilidade dos dispositivos. Além disso, ao limitar os sinais ao corpo, o HBC também aumenta a segurança da rede e a privacidade dos dados, e reduz a interferência entre redes distintas[9][10]. Os métodos de acoplamento do HBC incluem o HBC capacitivo (Cap-HBC) e o HBC galvânico (Gal-HBC), que serão detalhados posteriormente. A taxa de transferência geralmente utilizada em BAN para a área médica varia entre 10 kbps e 10 Mbps[7]. A Tabela 1.1 apresenta uma comparação entre os principais métodos de comunicação utilizados em BAN e mostra uma propensão à interferência menor para os métodos HBC capacitivo e galvânico quando comparados ao UWB (*Ultra Wide Band*), comumente utilizado em IoT (Internet of Things - Internet das Coisas), Zigbee e Bluetooth, que são os principais métodos de transmissão via RF para WSN.

No que diz respeito ao parâmetro de distância, UWB, Zigbee e Bluetooth, todos com 10 metros, têm o maior alcance, enquanto o HBC se limita a uma distância de poucos metros, com o método de acoplamento capacitivo tendo um alcance de 2 metros e o acoplamento galvânico permitindo alcançar cerca de 40 centímetros. Já os links de acoplamento indutivos ou capacitivos, representados com sigla ICL (*Inductive Capacitive Links*), possuem um alcance de aproximadamente 3 centímetros, o que é uma distância curta demais para a maioria dos projetos. A frequências de operação das técnicas Zigbee e Bluetooth é 2,4 GHz, o UWB opera entre 3 e 10 GHz, enquanto o HBC, com acoplamento capacitivo, opera entre 10 - 100 MHz, e o HBC com acoplamento galvânico opera em 0,1 a 1 MHz[9].

| Técnica            | Frequência(GHz) | Taxa de<br>transferência (Mbps) | Potência(dBm) | Alcance de transmissão | Alcance de<br>Interferência |

|--------------------|-----------------|---------------------------------|---------------|------------------------|-----------------------------|

| <b>Zigbee</b> [93] | 0,865-2,4       | 0,25                            | -3-10         | 10 m                   | alta                        |

| Bluetooth[94]      | 2,4             | 0,721-20                        | <20           | 10 m                   | alta                        |

| UWB                | 3-10            | 0,85-20                         | -41           | 10 m                   | alta                        |

| ICL                | 0,001-0,4[15]   | 0,0001-4[95]                    | -             | $0,5-3~{ m cm}$        | baixa                       |

| Cap-HBC            | 0,01-0,1        | 0,002-10                        | -15-5         | 5 cm-2 m               | baixa                       |

| Gal-HBC            | 0,0001-0,01     | 0,0009-2                        | -30-(-4)      | 5  cm-40  cm           | baixa                       |

Tabela 1.1: Características dos métodos de comunicação.

Fonte: Extraído de [9].

vezes maiores do que as frequências do acoplamento galvânico. A taxa de transferência de dados é significativamente superior no HBC capacitivo, assim como o alcance da transmissão, conforme apresentado na Tabela 1.1 [9]. Além disso, uma nova forma de acoplamento está emergindo no meio acadêmico, baseada em indução e denominada acoplamento magnético, mas não será abordada neste trabalho [11][12].

Dessa forma, o objetivo geral deste trabalho é abordar o projeto de um receptor para a tecnologia HBC, com ênfase no acoplamento capacitivo e arquitetura voltada para baixo consumo energético.

### 1.2 Objetivos

O projeto tem como objetivo geral alcançar as seguintes realizações com base nas informações obtidas na revisão bibliográfica: desenvolver um circuito receptor para HBC com acoplamento capacitivo em tecnologia CMOS 180 nm, utilizando modulação FSK com aprimoramentos no consumo energético e com taxa de dados adequada para aplicações médicas na faixa de operação do HBC. Dessa forma, os objetivos específicos podem ser delineados da seguinte maneira:

- Estudar a comunicação por HBC e o modelo de canal para a transmissão de dados.

- Projetar e simular os blocos de um circuito receptor, como amplificador, oscilador, entre outros, separadamente, com foco na análise de comportamento e desempenho, visando viabilizar a construção do circuito.

- Integrar os blocos do receptor, realizar avaliações funcionais e de desempenho por meio de simulações e, em seguida, produzir o leiaute para a fabricação do circuito.

- Comparar os resultados obtidos para o receptor proposto com alguns circuitos apresentados na revisão bibliográfica, com foco no consumo energético, nível de complexidade e custo de projeto.

### 1.3 Metodologia

O trabalho segue as seguintes fases para o seu desenvolvimento:

- 1. Revisão bibliográfica: uma pesquisa realizada voltada para estudar a comunicação via HBC e circuitos semelhantes aos que se propõe desenvolver aqui, mas no estado da arte, com o objetivo de obter dados pertinentes à caracterização do canal, às topologias e ao desempenho de circuitos, como taxa de transferência de dados, tecnologia de construção, consumo e eficiência energética.

- 2. Projeto e simulação: projetar e simular os blocos utilizados em tecnologia CMOS UMC L180 Mixed-Mode/RF , utilizando ferramentas matemáticas, como Octave e Matlab, e de simulação, como o Cadence Virtuoso, para verificação da funcionalidade e do desempenho individual e integrados no circuito receptor.

- 3. Confecção de leiaute: Produção do leiaute do circuito completo para fabricação em tecnologia CMOS, com a devida verificação das regras de fabricação e do desempenho do projeto em simulações pós leiaute.

- 4. Análise de resultados: Analisar os resultados de simulação e compará-los com receptores encontrados na literatura.

- 5. Redação do texto final: Organizar todo o conhecimento obtido pela pesquisa realizada no item 1, descrever a concepção dos blocos individuais e do receptor, demonstrar os resultados das simulações realizadas nos itens 2, 3 e 4, e resumir o trabalho em forma de artigo para apresentação no XLI Simpósio Brasileiro de Telecomunicações e Processamento de Sinais.

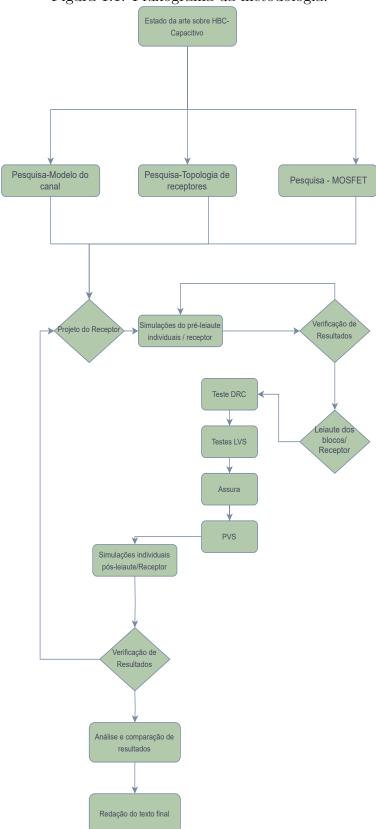

A metodologia utilizada pode ser resumida no fluxograma representado na Figura 1.1. Para a realização das atividades, foram utilizados softwares gratuitos ou as licenças dos softwares disponíveis para o Laboratório de Concepção de Circuitos Integrados (LCCI) no desenvolvimento de trabalhos em tecnologia CMOS, a rede interna para trabalhos à distância da UFBA e o acesso ao conteúdo IEEE disponibilizado pela CAPES para pesquisa de referências.

Figura 1.1: Fluxograma da metodologia.

Fonte: Fluxograma produzido pelo autor.

# Capítulo 2

# Estado da arte de transceptores e receptores para HBC capacitivo

Em 1995, a análise conduzida por T.G Zimmermann representou um marco inicial crucial para a pesquisa da tecnologia conhecida como BCC (Body Couple Communication), também denominada HBC (Human Body Communication). Nessa pesquisa, Zimmermann abordou um modo de comunicação corpórea, modelando separadamente os componentes TX (transmissor) e RX (receptor), operando sob consumo de energia proveniente de bateria.[8]

Os eletrodos de TX e RX são fixados ao corpo, sendo a transferência de dados do RX para o TX realizada por meio de aterramento externo, conferindo importância ao eletrodo de aterramento. Já a transferência do TX para o RX ocorre através do corpo humano. Os circuitos responsáveis pela recepção de dados e os circuitos transmissores evoluíram em capacidade de taxa de dados, distância coberta e redução no consumo de energia, permitindo aprimoramentos em suas versões desenvolvidas também para HBC [8].

A abordagem feita por [13] sobre HBC capacitivo explora o projeto de um transceptor que utiliza a modulação *OOK (On-Off Keying)*, chaveamento ligadesliga, e opera numa banda *quasi-static* (a partir de 30 MHz e menor que 200 MHz), considerada mais estável em relação à perda de sinal. O projeto apresentado utiliza a técnica *auto-loss-compensation (ALC)*, que se baseia em atenuar a capacitância de acoplamento reverso, reduzindo assim a potência necessária para a transferência de dados. O circuito foi desenvolvido na tecnologia CMOS 180 nm, alcançando uma taxa de transferência de 4 Mbps.

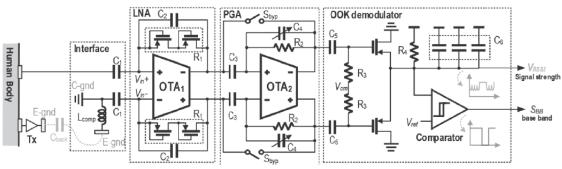

O receptor do circuito está apresentado na Figura 2.1 e é composto pelos seguintes blocos: uma interface para contato com a pele, seguida por um LNA para amplificação de baixo ruído. No terceiro estágio, é utilizado um PGA (programmable gain amplifier), um amplificador programável. O último estágio consiste em um demodulador OOK. O consumo do receptor é de 160  $\mu W$  [13].

Figura 2.1: Circuito do receptor com interface capacitiva.

Fonte: Imagem extraída de [13].

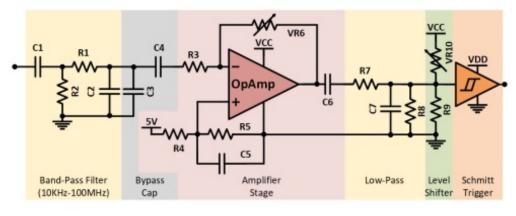

O receptor apresentado por [14] é baseado no método chamado PIC (pulse index communication), que utiliza as bordas dos pulsos transmitidos para codificar e detectar os pulsos. O objetivo é simplificar a topologia física de um transceptor para HBC, reduzindo assim o consumo final ao eliminar circuitos dedicados ao clock, à recuperação de dados e à correção do ciclo de trabalho. O esquemático do receptor neste projeto é demonstrado pela Figura 2.2.

Este projeto tem um consumo estimado de cerca de 1 mW a 9 mW para os dois modos de operação. Os blocos na Figura 2.2 incluem um filtro passa-faixas, que permite apenas a passagem de frequências de 10 kHz até 100 MHz, seguido por um estágio de amplificação com um amplificador inversor, um filtro passa-baixas, um circuito auxiliar para troca de nível DC realizado por um divisor de tensão com uma resistência fixa e uma variável, e, por último, um *Schmitt Trigger* [14].

Figura 2.2: Circuito receptor com *PIC*.

Fonte: Circuito Extraído de [14].

Em [15], foi projetado um transceptor, demonstrado na Figura 2.3, para HBC com tecnologia CMOS de 180 nm, focado em ultra baixo consumo. Utilizouse a modulação DPFSK (*Discontinuous-phase FSK*), escolhida com o objetivo de simplificar o circuito, resultando em redução na área do chip resultando em uma área de 0,046 mm<sup>2</sup>. O transceptor, atuando como transmissor e receptor na mesma unidade, foi desenvolvido para a conexão de biossensores, coletando dados na rede e transmitindo para equipamentos externos.

A frequência utilizada como portadora foi de 80 MHz. O circuito apresenta uma taxa de transferência de 1 Mbps, e o projeto opera com 1,8 V de tensão de alimentação. O receptor tem um consumo de 1,79 mW, enquanto o transmissor consome 700  $\mu$ W, resultando numa energia consumida de 1,79 nJ/bit no receptor e 0,7 nJ/bit no transmissor. O TRX apresentado na Figura 2.3 é composto por um receptor (RX) com conversão direta e amplificadores limitadores, que também servem para a proteção do circuito. Um demodulador baseado em DL ( $Delay\ Line$ ) no front-end converte os sinais de frequências DPFSK em sinais de banda modulados em quadratura (Q/I) com uma linha DL replicada para Q atrasada em 90°. No final do demodulador, um filtro Sallen Key é utilizado para remover e filtrar os harmônicos da saída do demodulador. Quanto ao transmissor (TX), ele foi implementado com um amplificador, um multiplexador, dois osciladores em anel controlados por tensão (VCO) e dois DACs (Digital-to- $Analog\ Converters$ ) [15].

Front-end

Amp.

| Delay Line |

Figura 2.3: Transceptor com TRX e RX.

Fonte: Circuito extraído de [15].

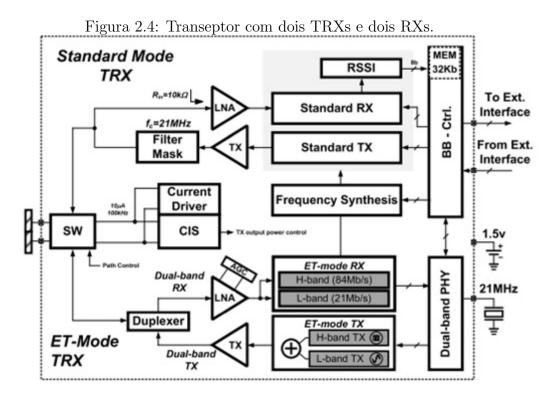

Em outubro de 2020, [16] propôs uma nova abordagem sobre HBC, concebendo um transceptor com dois TRXs e dois RXs. O circuito, mostrado na Figura

2.4, é adaptável a duas formas de utilização: uma no padrão IEEE 802.15.6 com modulação BPSK, taxa de transferência entre 164 kbps e 1,315 Mbps, sendo o TX consumindo 0,9 mW para esse modo, e o RX (ambas partes do TRX demonstrado na Figura 2.4 consumindo 5 mW. O projeto possui um segundo TX e um segundo RX para o método de operação ET (*Entertainment-Mode*), modo de entretenimento, e suas características estão presentes na Tabela 2.

O circuito completo tem uma relação energética de 3,8 nJ/bit e banda de frequência entre 18,375 MHz e 23,625 MHz. O segundo método de funcionamento do circuito possui duas bandas, a primeira sendo de 31,5 MHz até 52,5 MHz e a segunda entre 147 MHz e 189 MHz, com modulação QPSK e taxa de transferência de 105 Mbps, sendo 21 Mbps para a primeira banda e 84 Mbps para a segunda. A tecnologia utilizada foi 180 nm para o TRX, e o RX foi fabricado em 65 nm. Os blocos dos circuitos consistem em duas unidades de funcionamento [16].

Fonte: Circuito extraído de [16].

O estudo proposto por [17] é um projeto desenvolvido em um circuito integrado CMOS de 130 nm. O circuito receptor utiliza modulação BFSK, com uma taxa de transferência especificada de 2 Mbps, consumindo 1,68 mW no receptor. Com potência consumida de 1,68 mW, e a tensão de alimentação é de 1,2 V. A faixa de frequência abrange 10 -100 MHz.

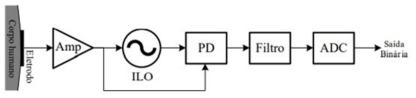

O receptor, ilustrado na Figura 2.5, é composto por um amplificador conectado diretamente ao eletrodo de contato com a pele. Utiliza um ILO (oscilador injetado), que é um oscilador empregando a técnica de injection locking, onde um oscilador em anel é projetado para sincronizar com uma frequência externa. Adicionalmente, inclui um PD (detector de fase) baseado no circuito flip-flop tipo D, um filtro RC passa-baixa e um comparador ADC. Isso resulta em uma demodulação por meio da conversão frequência-fase [17] [18].

Figura 2.5: Circuito do receptor BFSK.

Fonte: Diagrama extraído de[17].

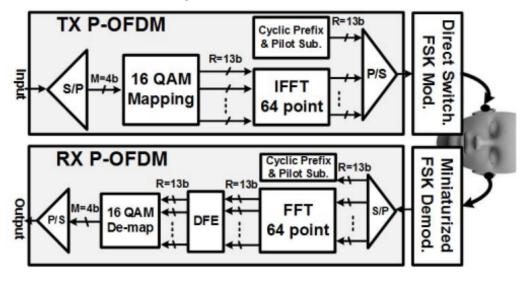

O transceptor, conforme apresentado na Figura 2.6, desenvolvido em 2017 por [19], utiliza POFDM (Pseudo Orthogonal Frequency Division Multiplex). O circuito, composto por dois TRXs, foi projetado para aplicações na área audiovisual, mais especificamente para comunicação auditiva. Assim, o circuito é constituído por um TRX para OFDM e um TRX para FSK, fabricado em tecnologia CMOS 65 nm. A ideia é empregar a modulação OFDM em duas frequências portadoras usando modulação FSK para reduzir a interferência.

A taxa de transferência do transceptor é de 1 Mbps, com uma banda de frequência de 20 MHz até 120 MHz e consumo de 1,4 mW.O circuito TR é composto por um TX utilizando QAM 16 para modulação em quadratura, e um RX que utiliza demodulador OFDM. Quanto ao modelo de demodulação FSK proposto, utiliza o algoritmo adaptive frequency hop para evitar interferência nos quatro canais. O seletor de canais realiza uma troca direta para FSK.

No receptor, há também um LNA para compensar as perdas no canal, um misturador com topologia Gilbert Cell para converter o sinal para banda base. O sinal resultante é direcionado para um circuito de decisão baseado em um comparador com histerese Schmitt Trigger para ajustar o sinal para bit 0 ou 1 [19].

Figura 2.6: TRX POFDM e FSK.

Fonte: Projeto extraído de [19].

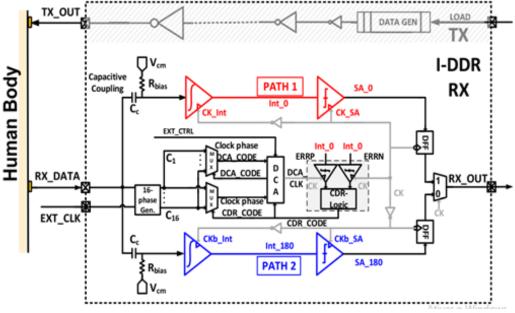

O circuito TRX proposto por [20], apresentado na Figura 2.7, é um transceptor HBC com tecnologia CMOS de 65 nm, utilizando modulação NRZ (Non Return to Zero). O circuito possui uma taxa de transferência de 30 Mbps, e seu receptor consome 98  $\mu W$ . No receptor, baseado na técnica de integração e amostragem periódica para mitigar interferências, existem dois caminhos com integrador e amostrador para processar bits alternados. Também são utilizados pseudo resistores para polarizar os integradores e garantir a impedância necessária para a transferência de tensão.

O circuito inclui ainda componentes para recuperação do clock (CDR - Clock-Data Recovery) e DCA(Duty Cycle Adaptation) para ajustar o ciclo de trabalho do clock e habilitar a rejeição de frequências variáveis. No transmissor, o circuito conta com um gerador de dados seguido por buffers em sequência para encaminhar o sinal pelo corpo [20].

Figura 2.7: Transceptor NRZ.

Fonte:Projeto extraído de [20].

Além dos receptores citados, utilizados para taxas de dados geralmente elevadas, que demandam um consumo moderado, existem receptores com propósitos secundários e taxas ultra baixas de dados, como na abordagem de [21], apresentada no circuito da Figura 2.8. Essa proposta visa um wake-up receiver para HBC, um tipo de receptor auxiliar de ultrabaixo consumo, utilizado para acionar dispositivos ociosos, como, por exemplo, outro receptor principal. Sua arquitetura, adequada para receber sinal OOK, conta com múltiplos estágios amplificadores para aplicar ganho na portadora modulada. Inclui também um detector de envoltória responsável por identificar os picos do sinal de entrada e converter o sinal OOK, modulado em 50 kHz, para a banda base.

Os dados da banda base, por fim, entram no Digital Correlator, que gera um pulso de wake-up quando uma sequência predeterminada de pulsos é detectada nesses dados. O circuito foi fabricado em tecnologia CMOS de 65 nm e consome uma potência de 694 pW, com a portadora do sinal escolhida em frequência de 50 kHz e a tensão de operação em 0,3 V [21].

Correlated OOK Tx Data **Pulse Output** Digital Envelope Transmitter Detector Correlator Front-End Gain Buffer Buffer (4 Stages)

Figura 2.8: Diagrama do wake-up receiver.

Fonte: Diagrama extraído de [21].

A Tabela 2 resume As características mais relevantes. Considerando a amostra constituída pelos trabalhos apresentados, verifica-se uma tendência para por circuitos de baixo consumo, com diversas topologias e resultados variados para a implementação do HBC.

Comparação entre os principais projetos pesquisados.

| _                 | _                        | _                                 | _                                                          |                       |                                           |                                                     |                    |                                           |                       |       |                    |       |  |

|-------------------|--------------------------|-----------------------------------|------------------------------------------------------------|-----------------------|-------------------------------------------|-----------------------------------------------------|--------------------|-------------------------------------------|-----------------------|-------|--------------------|-------|--|

| [19]              | $64 \cdot P(OFDM) + FSK$ | 65 nm                             | 1 Mbps                                                     | 1,4 mW $20-120 MHz$   |                                           | ~ 11 11 01                                          | 1,1 V              |                                           |                       |       |                    |       |  |

| [17]              | FSK                      | 130 nm                            | 2 Mbps                                                     |                       | A A                                       | 3ο μw (κ.α.)   Αρτοχ 1.0ο πων (κ.α. est.)   1,4 πων |                    | Não nosemi 10_100 MHz                     |                       | 1,2~V |                    |       |  |

| [20]              | NRZ                      | 65 nm                             | 30~Mbps                                                    |                       | (AG)/H= 80                                | 90 µW (nA)                                          |                    | Não possui                                | masod on t            |       | 1 V                |       |  |

| [16](802.15.6)/ET | BPSK/QPSK                | 180 nm (TRX)/ 65 nm RX adicional  | 164 kbps-1,315 Mbps(BPSK)- 105 Mbps(QPSK)(21+84)   30 Mbps | $5~mW({ m RX})$ -BPSK | $0.9~mW(\mathrm{TX})/$                    | $2,1~mW(\mathrm{TX})$                               | 9,4 $mW(RX)$ -QPSK | $18,375-23,625\ MHz(BPSK)/31,5-52,5\ MHz$ | $147-189 \ MHz(QPSK)$ |       | 1,5 V              |       |  |

| [15]              | DPFSK                    | UMC 180 nm                        | 1~Mbps                                                     |                       | (VG)/II 07 1                              | 1,19 mW (KA)                                        |                    | 80 MHz                                    | 21111                 |       | 1,8 V              |       |  |

| [14]              | Não informada            | Circuito Discreto                 | 21 Mbps-120 Mbps                                           |                       | Est $LS(0,2-0,8)$                         | HS(1,3-4,4)                                         |                    | Não informado                             |                       | 1,1 V | $3,3\ V$           | 5,5 V |  |

| [13]              | OOK                      | 180 nm                            | 4 Mbps                                                     |                       | $160~\mu W({\rm RX})$                     |                                                     |                    | 91 MHz                                    | 21~MHz                |       | 0,8 V              |       |  |

| Parâmetros        | Modulação                | Tecnologia de construção   180 mm | Taxa de transferência   4 Mbps                             |                       | Consumo de potência $160~\mu W({\rm RX})$ |                                                     |                    |                                           |                       |       | Tensão de operação |       |  |

Fonte: Tabela produzida pelo autor.

Os transceptores HBC possuem demanda energética muito baixa, como verificado nos circuitos apresentados, mas ainda existe espaço para melhoria desse aspecto técnico. Todos os transceptores pesquisados têm uma tendência de consumo energético na ordem de nanojoules por bit, assim como uma tensão de alimentação por volta de 1 V a 2 V, dadas as escolhas da tecnologia de fabricação. As modulações também apresentam a tendência de serem as mais simples, como OOK e FSK. O motivo para essa escolha é que a modulação mais simples reduz a complexidade do circuito. As frequências tendem a situar-se entre 20 e 100 MHz para as modulações mais simples e modos de baixo consumo, e o foco é sempre uma transmissão maior ou igual a 1 Mbps, e o mínimo de consumo energético possível.

# Capítulo 3

### Fundamentação teórica

### 3.1 HBC - Comunicação pelo corpo humano

O HBC, Human Body Communication, ou Comunicação pelo Corpo Humano em português, é uma tecnologia criada em 1995 por Thomas Gutrie Zimmmerman. O HBC tem como principal característica utilizar o corpo humano como meio de transporte de sinal. Estudos também dividem em três as possíveis classificações para o HBC, de acordo com o tipo de ajuste de fixação dos eletrodos no corpo humano. São eles: o acoplamento capacitivo [9] [11] [17] e o acoplamento galvânico [9] [11], como principais, além do acoplamento magnético [11] [22]. Neste trabalho, abordaremos apenas o acoplamento capacitivo do HBC.

### 3.1.1 Acoplamento capacitivo

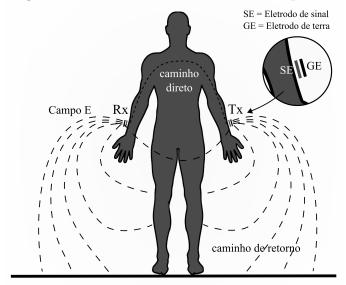

O acoplamento capacitivo é uma ligação que utiliza dois pares de eletrodos fixados no corpo: um par de eletrodos para o circuito transmissor e outro para o receptor. Em cada par de eletrodos, tanto do receptor quanto do transmissor, um eletrodo está em contato com o corpo humano (eletrodo de sinal), e o outro eletrodo está em contato com o ar (eletrodo de terra).

A condução ocorre quando campos elétricos se formam entre os eletrodos de sinal e os tecidos, e entre os eletrodos de terra e o plano de terra externo, como mostrado na Figura 3.1. Esse campo elétrico, resultante de um potencial elétrico no transmissor (TX), consegue transmitir informação utilizando o corpo como meio de condução. A faixa de frequência para utilização do HBC capacitivo é, usualmente, entre 10 e 100 MHz, e o alcance da transmissão está entre 5 cm e 2 m [9] [11] [17] [4].

Figura 3.1: Imagem ilustrativa do fluxo elétrico do acoplamento capacitivo.

Fonte: Imagem produzida pelo autor.

#### 3.1.2 Modelagem do canal

Os modelos do canal HBC se dividem em dois grupos gerais distintos: os modelos analíticos, baseados nas equações eletromagnéticas, e os modelos de circuitos com parâmetros concentrados ou distribuídos [9] [8]. De maior relevância para o projeto de circuitos são os modelos baseados em circuitos.

Na literatura, algumas modelagens de circuitos do canal HBC capacitivo consideram que as impedâncias das camadas de tecido, as distâncias dos eletrodos com o meio externo e entre os eletrodos em si aparecem como variações de circuitos RC em série e paralelo.

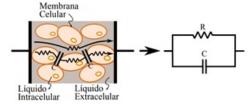

Muitos modelos apresentados para os tecidos convergem para uma representação elétrica de um circuito RC, estando de acordo com as características capacitivas e condutivas apresentadas durante os testes realizados tanto na membrana celular quanto nos líquidos internos e externos às células. Assim, utilizando as dimensões de comprimento (L) e secção transversal (A), a permissividade e a condutividade de um determinado agrupamento de amostras de tecidos modelados pelas equações de Cole-Cole, que descrevem a condutividade e permissividade nos tecidos, podemos obter as aproximações para a resistência R, Equação (3.1) e para a capacitância C,(Equação 3.2) com base nas permissividade e condutividade. A Figura 3.2 representa o modelo simplificado comparando o circuito RC com a célula de um tecido [17] [9] [20].

$$R = \frac{L}{\sigma(\omega)A} \tag{3.1}$$

$$C = \frac{\varepsilon_r(\omega)\varepsilon_o A}{L} \tag{3.2}$$

Figura 3.2: Modelo RC equivalente ao tecido em nível celular.

Fonte: Imagem extraída de [17].

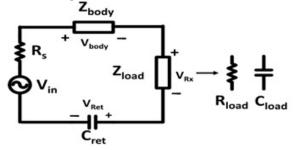

Considerando a representação elétrica dos tecidos e que a distância dos eletrodos de terra com o plano de terra pode ser representada por uma capacitância, uma função de transferência para o canal pode ser encontrada a partir da representação simples do canal HBC mostrada na Figura 3.3, onde  $Z_{\text{body}}$  é a impedância do corpo,  $R_s$  é a resistência do receptor,  $Z_{\text{load}}$  é a impedância do receptor, e  $C_{\text{ret}}$  é a capacitância do caminho de retorno. Assim, a Equação 3.3, apresentada por [20], oferece uma forma muito simplificada de modelar a perda completa no canal [20].

Figura 3.3: Modelo do canal.

Fonte: Imagem extraída de [20].

$$\frac{V_{Rx}}{V_{in}} = \frac{Z_{\text{load}}}{R_s + Z_{\text{body}} + Z_{\text{load}} + \frac{1}{sC_{\text{ret}}}}$$

(3.3)

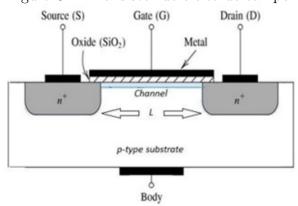

### 3.2 MOSFET

O transistor de efeito de campo, MOSFET ( $Metal\ Oxide\ Semiconductor\ Field\ Effect\ Transistor$ ), é um dispositivo eletrônico que possui quatro terminais com as seguintes nomenclaturas e abreviações: D (Drain), Dreno; G (Gate), Porta; B (Bulk), substrato; e S (Source), Fonte. A Figura 3.4 apresenta um transistor MOSFET tipo N, no qual o substrato é feito de material semicondutor, geralmente silício, tipo P, e Fonte e Dreno são feitos com material tipo N. Por outro lado, o MOSFET tipo P possui substrato com tipo N, e Fonte e Dreno são feitas com material tipo P. A porta é um contato metálico separado do substrato por um dielétrico, como  $SiO_2$ . Materiais de tipo P possuem um excesso de portadores de carga elétrica positiva (lacunas), enquanto materiais N possuem um excesso de portadores de carga elétrica negativa (elétrons).

O funcionamento básico do MOSFET fundamenta-se na amplitude da diferença de potencial entre o terminal Gate e o Bulk ( $V_{GB}$ ), seja ela positiva ou negativa, dependendo do tipo de transistor, seja ele tipo N (NMOS) ou tipo P (PMOS).

Isso cria entre os terminais de Fonte e Dreno uma zona de condução composta por cargas elétricas opostas às presentes no substrato, gerando uma corrente entre dreno e fonte ao aplicar um potencial adequado entre esses terminais[23] [24].

Figura 3.4: Transistor de efeito de campo.

Fonte: Imagem extraída de [23].

O MOSFET possui basicamente dois regimes de operação em modelos descontínuos: inversão fraca e inversão forte, de acordo com a tensão  $(V_{GB})$ . As equações das correntes  $I_D$  para cada regime de operação serão citadas nos parágrafos seguintes. Nas expressões a seguir,  $V_t$  é a tensão de threshold,  $(V_{ds})$  é a tensão entre dreno e fonte, Vgs é a tensão entre porta e fonte, Vsb é a tensão entre fonte e substrato, Vg é a tensão da porta, n é o fator de rampa,  $(I_D)$  é a corrente entre dreno e fonte, W é a largura escolhida para o transistor, L é o comprimento,  $C'_{ox}$  é a capacitância do óxido,  $\mu$  é a mobilidade de elétrons no material,  $\phi t$  é a tensão Termodinâmica, uma

variável função de k(T/q) em que k é a constante de Boltzmann e T é a temperatura medida em Kelvin e q é a carga elétrica do elétron em Coulombs [23] [25].

O regime de inversão fraca, que se subdivide em regiões linear ou de saturação, tem como condição primária a relação  $(V_{gs}) < (V_t)$ , caso  $V_{sb}$  seja igual a 0, ou  $(V_{GB}) < (V_t) + n.(V_{sb})$  para o transistor NMOS. A região de tríodo ou linear é aquela em que o MOSFET apresenta uma relação linear entre a corrente  $(I_D)$  e a tensão entre dreno e fonte. A corrente  $I_D$  é representada pela Equação 3.4. O limiar desta região é definido por  $(V_{ds}) < 4\phi T$ , onde  $(V_{ds})$  é a tensão entre dreno e fonte, e  $4\phi T$  é a tensão de pinch-off. A região de saturação, onde  $(I_D)$  é aproximadamente constante em relação a  $(V_{ds})$ , ocorre para  $(V_{ds}) \ge 4\phi T$ , e  $(I_{Do})$  é a corrente  $(I_D)$  para  $(V_{gs}) = (V_t)$ . Seu comportamento é dado pela Equação 3.5 [23][26] [24].

$$I_D = I_{Do} e^{\left(\frac{V_{gb} - V_t}{n\phi t} - V_{sb}\right)} \left(1 - e^{\frac{-V_{ds}}{\phi t}}\right), (V_{ds}) < 4\phi T$$

$$(3.4)$$

$$I_D = I_{Do}e^{(\frac{V_{gs} - V_t}{\phi t})}, (V_{ds}) > 4\phi T$$

(3.5)

De maneira análoga, a inversão forte, que ocorre quando  $(V_{gs}) \geq (V_t) + n(V_{sb})$  ou  $(V_{gs}) \geq (V_t)$ , para Vsb igual a 0, também possui regiões tríodo e de saturação. Para região tríodo, a sua relação de tensões é  $V_{db} < (Vgb - Vt)/n$  ou  $V_{ds} < (Vsg - Vt)/n$ , considerando  $V_{sb} = 0$ . Para a região de saturação, a relação é  $V_{db} \geq (V_{gb} - Vt)/n$  ou  $V_{ds} \geq (V_{sg} - Vt)/N$ , considerando  $V_{sb}$  igual a 0. A equação do comportamento da corrente  $I_D$ , cujo modelo é baseado na aproximação de canal gradual, para região tríodo com inversão forte é dada pela Equação 3.6 [23][26] [24]:

$$I_D = K \left[ 2 \left( V_{gs} - Vt \right) V_{ds} - V_{ds}^2 \right], onde K = \frac{1}{2} \mu C'_{ox} \frac{W.n}{L}$$

(3.6)

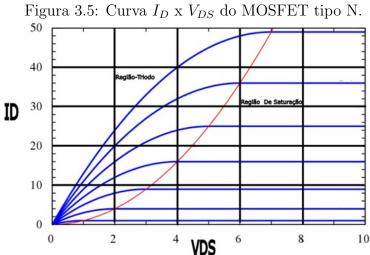

O gráfico resultante das operações do MOSFET tipo N, apresentado na Figura 3.5, indica a relação entre  $I_D$  e  $V_{DS}$ . O comportamento da corrente  $I_D$  para a região de saturação com inversão forte é dada pela Equação 3.7 [23][26] [24]:

$$I_D = K \left[ 2 \left( V_{gs} - V_t^2 \right) \right] \left[ 1 + \lambda V_{ds} \right], onde K = \frac{1}{2} \mu C'_{ox} \frac{W.n}{L}$$

(3.7)

Para o MOSFET PMOS, as condições de inversão forte são  $V_{sg} \geq |V_t|$  e  $V_{sd} < (V_{sg} - |V_t|)$ , caracterizando a região de tríodo, conforme a Equação 3.8, que descreve o comportamento da corrente  $I_D$ . Já na região de saturação, as condições

são  $V_{sg} \ge |V_t|$  e  $V_{sd} \ge (V_{sg} - |V_t|)$ . A Equação 3.9 representa a corrente  $I_D$  nesse contexto. No caso do transistor PMOS, é sempre válido que  $V_t < 0$  [23][26] [24].

$$I_D = K \left[ 2 \left( V_{gs} - |V_t| \right) V_{sd} - V_{sd}^2 \right], onde K = \frac{1}{2} \mu C'_{ox} \frac{W.n}{L}$$

(3.8)

$$I_D = K \left[ (V_{sg} - V_t)^2 \right] \left[ 1 + \lambda V_{ds} \right], onde K = \frac{1}{2} \mu C'_{ox} \frac{W.n}{L}$$

(3.9)

Fonte: Imagem produzida pelo autor.

## 3.3 Arquitetura de um receptor RF

Para qualquer comunicação que sofre severas restrições causadas pelo ambiente, uma das maiores limitações ocorre devido ao número limitado de banda que pode ser alocado para cada usuário. O resultado é uma restrição no tráfego de informação, tornando necessário o uso de técnicas avançadas de codificação, compressão e modulações eficientes para faixas específicas de frequência.

Existem várias técnicas capazes de realizar a recepção de um sinal, e a escolha deve ser baseada nas necessidades de cada projeto, como taxa de transferência, consumo, desempenho, complexidade, custos ou características do sinal a ser recebido. Neste contexto, serão abordadas apenas algumas topologias básicas para receptores[25].

## 3.3.1 Receptores heteródinos

Os receptores heteródinos são aqueles que utilizam misturadores de frequência e pelo menos um oscilador local (LO), geralmente um PLL( $Phase\ locked\ loop$ ), que gera um sinal de referência com frequência  $\omega_{lo}$  diferente da frequência de RF do sinal recebido. Essa operação realiza a multiplicação entre a frequência RF e a frequência LO, resultando em uma frequência intermediária IF ( $Intermediate\ Frequency$ ). Esse processo é uma das etapas utilizadas para reduzir a frequência de RF para a banda base.

As técnicas de conversão de frequência para a banda base são denominadas down conversion e, em alguns receptores, podem envolver vários estágios de mistura de sinais, utilizando mais de uma IF [25]. Existem duas opções para a utilização dessa técnica. Na primeira, a frequência do LO é fixa, com cada canal RF convertido para uma IF separada, resultando em  $F_{if} = F_{rf} - F_{lo}$ . A segunda opção envolve uma frequência do LO variável, onde as frequências RF são convertidas para uma mesma IF, selecionando  $F_{lo} = F_{rf} - F_{if}$ . Após essa etapa, o sinal resultante passa por um filtro passa-baixas para remover componentes indesejadas geradas pela multiplicação no domínio da frequência [25][26].

Os receptores heteródinos sempre utilizam amplificadores de baixo ruído antes dos misturadores, uma vez que estes tendem a introduzir muito ruído, além de o sinal recebido já estar bastante atenuado. Um exemplo básico de receptor heteródino está ilustrado na Figura 3.6.

Figura 3.6: Exemplo de receptor heteródino.

Entrada

LNA

Filtro

Saída

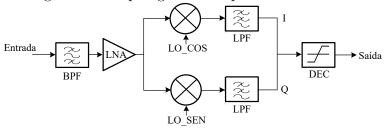

#### 3.3.2 Receptores homodinos

Nos receptores homodinos, também chamados de receptores de conversão direta, em vez de reduzir as frequências para a banda base por múltiplos estágios, utilizando uma ou mais frequências intermediárias entre esses estágios, como no receptor heteródino, a conversão é feita diretamente do sinal RF para a banda base, usando  $\omega_{lo}$  igual à frequência de RF. O circuito apresentado na Figura 3.7 é um exemplo de circuito receptor homodino, no qual um filtro passa-faixa (BPF) está conectado a um amplificador de baixo ruído (LNA). Este, por sua vez, é ligado a dois misturadores (mixers), sendo que cada mixer recebe um sinal senoidal de LOs em quadratura. O sinal resultante da operação entre o sinal do LO e o sinal proveniente do LNA, misturados no mixer, é o sinal de banda base, que passa por um estágio adicional de filtragem com um filtro passa-baixas (LPF) para realizar a seleção de canal[25][26].

Figura 3.7: Exemplo de receptor homodino.

Entrada

BPF

LO\_COS

LO\_SEN

LO\_SEN

Fonte: Imagem produzida pelo autor.

## 3.3.3 Topologias de receptores FSK

A modulação FSK é amplamente empregada em receptores de baixo consumo, devido à sua resistência a interferências e à baixa complexidade exigida nos projetos

de circuitos. A seguir, serão apresentadas algumas topologias de receptores FSK para fins de comparação.

A primeira abordagem é chamada de demodulação FSK síncrona. Nesta configuração, um sinal RF é direcionado para dois ramos paralelos conectados a misturadores que recebem sinais de osciladores locais em cada frequência do FSK. Esses ramos, geralmente denominados caminhos I e Q, são seguidos por filtros passabaixas. Os sinais resultantes desses ramos convergem em um circuito de decisão, que pode ser um comparador capaz de diferenciar as componentes da modulação FSK. O diagrama esquemático dessa topologia é apresentado pela Figura 3.8 [19] [27].

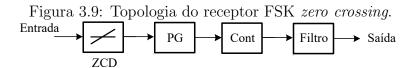

A segunda abordagem é denominada zero crossing demodulator (demodulador de cruzamento por zero). Ela opera com base no princípio de que a informação é carregada pela frequência do sinal. Assim, o período é verificado no momento em que ocorre o cruzamento do sinal para determinar sua frequência local. Essa arquitetura inclui um zero crossing detector (ZCD), seguido por um gerador de pulso (PG), um contador e um filtro. Seu diagrama é demonstrado na Figura 3.9[19][20].

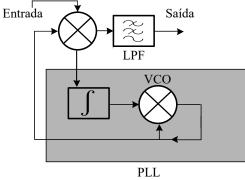

A próxima topologia é baseada em PLL, que opera em função das mudanças na frequência de RF, resultando em alterações na entrada do detector de fase. Após a filtragem, essas mudanças permitem recuperar a informação. Seu circuito inclui um LNA (amplificador de baixo ruído), seguido por um misturador (ou mixer), conectado a este misturador está um PLL (phase-locked loop). O sinal resultante da operação entre o misturador e o PLL é então direcionado para um LPF (low-pass filter), um filtro passa-baixas. Essa topologia é demonstrada na Figura 3.10 [19].

A última topologia básica é a não síncrona ou assíncrona, na qual o sinal RF passa por dois ramos paralelos compostos por filtros passa-faixa sintonizados para as frequências do sinal FSK e detectores de envoltória ED (*Envelop Detector*). As saídas dos ramos são analisadas por um circuito de decisão para concluir a demodulação. A Figura 3.11 demonstra o diagrama esquemático correspondente[19][27].

As próximas topologias a serem descritas são alternativas de baixo consumo em relação às técnicas mencionadas anteriormente.

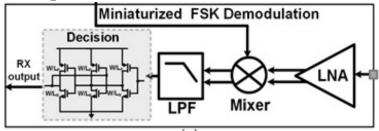

A abordagem proposta por [19] é baseada na conversão direta, composta por um LNA seguido por um misturador, filtro passa-baixas e um circuito de decisão. Essa abordagem permite distinguir entre duas frequências próximas à frequência do oscilador local, possibilitando a detecção síncrona sem a necessidade de um PLL. A Figura 3.12 apresenta o circuito. Outra técnica, apresentada por [27], utiliza a conversão em frequência-amplitude por meio do mecanismo de *injection locking*: o sinal FSK recebido é amplificado por um LNA, injetado em um IL-DCO (oscilador com *injection locking* controlado digitalmente), e a envoltória do IL-DCO é obtida e avaliada para realizar a demodulação. A Figura 3.13 ilustra essa técnica [19][27].

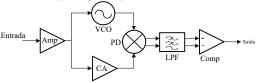

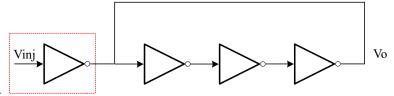

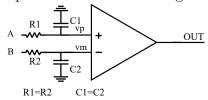

A próxima técnica a ser abordada também utiliza o mecanismo de *injection locking*, mas para a conversão frequência-fase [18]. Consiste em aproveitar um efeito do travamento por injeção que relaciona cada frequência do sinal injetado com um desvio de fase específico entre o sinal injetado (frequência de entrada) e o sinal resultante da operação no oscilador. O circuito é composto por um VCO (*Voltage-Controlled Oscillator*) em série com um P.D (*Phase Detector*), detetor de fase, para comparar os sinais de saída do VCO e de um sinal cópia, além de um *buffer* de saída. O esquema está representado na Figura 3.14[18].

Figura 3.8: Topologia do receptor FSK síncrono.

Fonte: Imagem produzida pelo autor.

Fonte: Imagem produzida pelo autor.

Figura 3.10: Topologia do receptor FSK com PLL.

Entrada ➤ Saída BPF ED

Figura 3.11: Topologia do receptor não síncrono.

Fonte: Imagem produzida pelo autor.

Figura 3.12: Demodulador FSK miniaturizado.

Fonte:Diagrama extraído de[19].

Figura 3.13: Receptor FSK com DCO.

Fonte: Diagrama extraído de [27].

Figura 3.14: Topologia de receptor com *Injection Locking*.

Fonte: Diagrama extraído de [18].

A maioria das topologias apresentadas requer o uso dos filtros, o que implica em dificuldade adicional para circuitos integradosnas frequências do HBC devido à necessidade de limitação na reconfiguração da faixa de frequência ou ao aumento da complexidade do circuito para soluções baseadas em filtros OTA-C ou a capacitores chaveados. Além disso, os projetos que empregam o detector de envoltória (ED) demonstram maior sensibilidade ao ruído, uma vez que são circuitos responsáveis pela conversão de frequência para amplitude.

Outro fator importante para a definição da arquitetura do receptor é a taxa de dados desejada para a aplicação e seu impacto na banda necessária. Como prevê o teorema de Shannon-Hartley 3.10, a capacidade do canal e, portanto, a taxa de dados, aumentam com a banda, exigindo um receptor capaz de operar com uma banda larga para taxas de dados elevadas. Neste sentido, os receptores que não utilizam técnicas de seletividade para demodulação da frequência são os mais adequados e, desta forma, o receptor baseado na conversão frequência-fase pelo travamento por injeção da Figura 4.1 apresenta-se como uma boa solução, especialmente ao utilizar um oscilador com fator de qualidade baixo, que fornece uma faixa de travamento larga, e um amplificador de entrada banda larga. Desta forma, esta será a arquitetura utilizada para o receptor a ser projetado.

$$C = \Delta f \log_2(1 + \text{SNR}) \tag{3.10}$$

Onde:

- C é a capacidade máxima do canal em bits por segundo (bps).

- $\Delta f$  é a largura de banda do canal em hertz (Hz).

- SNR é a relação sinal-ruído do canal.

## 3.4 Injection Locking

O injection locking, ou travamento por injeção, foi descoberto por volta do século XVII por Christiaan Huygens, que observou a mudança na frequência de oscilação de um pêndulo quando sujeito ao efeito de uma oscilação externa. O principal objetivo dessa técnica é sincronizar a frequência de um oscilador com uma frequência externa injetada. Em outras palavras, um oscilador operando em uma frequência natural  $\omega_0$  passa a operar sob a influência de um sinal injetado com frequência  $\omega_1$ , tornando sua frequência de operação igual à do sinal injetado  $\omega_1$ , desde que o sinal esteja dentro das limitações de amplitude e frequência inerentes a cada oscilador.

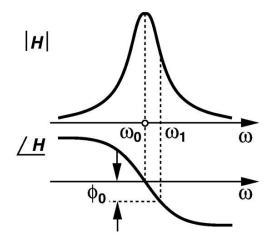

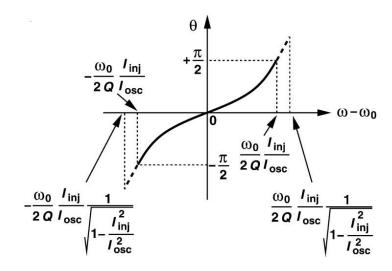

Para entender como esse efeito ocorre, é necessário compreender que um oscilador possui um circuito ressonante, geralmente um circuito LC (indutivo-capacitivo), com  $\omega_0 = \sqrt{LC}$ , chamada de frequência natural do oscilador. Quando um novo sinal é inserido no sistema, o circuito deixa de operar em  $\omega_0$  e passa a atuar em uma nova frequência, criando um desvio  $\phi_0$  no ciclo de acordo com o distúrbio. Este efeito força o oscilador a operar em uma nova frequência  $\omega_1$  de acordo com o desvio  $\phi_0$ , como demonstrado na Figura 3.15. O circuito ressonante passa a influenciar na frequência, opondo-se ao desvio  $\phi_0$  e tentando cancelá-lo [28].

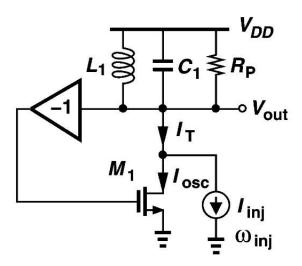

Ao injetar uma corrente  $I_{\rm inj}$  no dreno de um oscilador, conforme demonstrado na Figura 3.16, considerando que a amplitude e a frequência são compatíveis, o oscilador passa a operar na frequência presente em  $I_{\rm inj}$ ,  $\omega_1$ , deixando sua frequência natural de oscilação. Então, o injection locking ocorre, e a diferença entre as frequências de injeção e do oscilador deve produzir um desvio de fase. Assim, o circuito ressonante passa a interferir na fase, tentando compensar o desvio a cada ciclo. Isso força  $V_{\rm out}$  a sofrer mudanças na fase para acompanhar a fase da corrente total resultante. A tensão  $V_{out}$  e a corrente  $I_T$  precisam conter fases diferentes, pois  $I_{osc}$  permanece em fase com  $V_{out}$ , tornando-se defasado em relação a  $I_T$ . Assim, a fase de  $I_{inj}$  forma um ângulo com a fase  $I_{osc}$ .

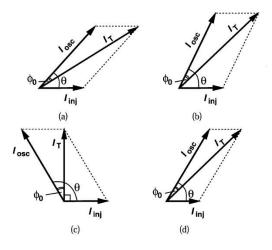

Para determinar a faixa de travamento (distância entre  $\omega_0$  e  $\omega_1$  onde o travamento pode ocorrer), analisa-se o diagrama fasorial das correntes para o circuito da Figura 3.16, apresentado na Figura 3.17(a). À medida que a distância entre  $\omega_0$  e  $\omega_1$  aumenta, a interferência do circuito ressonante nas fases cresce, resultando em um maior ângulo  $\phi_0$  entre  $I_{osc}$  e  $I_T$ . Para compensar,  $I_{osc}$  é forçada a seguir em sentido anti-horário, como mostrado na Figura 3.17 (b), levando às equações 3.11 [28].

Figura 3.15: Módulo e fase do circuito sob injection locking.

Fonte: Imagem extraída de [28].

Figura 3.16: Exemplo de circuito oscilador.

Fonte: Imagem extraída de [28].

Figura 3.17: Diagramas de fasor das correntes em um injection locking oscilator para diferentes valores de  $|\omega_0 - \omega_{inj}|$  e amplitude de  $I_{inj}$ .

Fonte: Imagem extraída de [28].

$$\sin(\phi_0) = \frac{I_{inj}}{I_T} \sin(\theta) \tag{3.11}$$

Em que:

$$I_T = I_{osc}^{ej\theta} + I_{inj} (3.12)$$